标签:

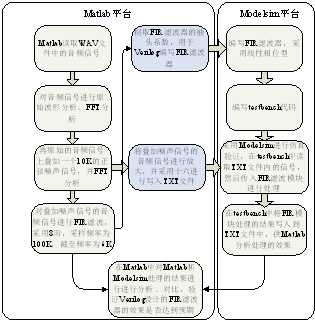

如今FPGA开发过程势必要涉及到一个过程:验证仿真,验证很多情况下是在Matlab上进行的,而仿真大部分初学者都是采用Modelsim仿真软件进行。比如设计一个信号滤波模块,验证该滤波模块是在Matlab上进行设计验证,得到该模块的设计参数和设计结构,然后再转换为RTL代码,再用Modelsim软件进行仿真,这个过程涉及到采用matlab软件产生待测试的信号,输入到RTL代码中,然后在通过Modelsim软件进行仿真得到处理后的信号,再将该信号输出到文件,最后通过Matlab软件分析处理后的信号的频谱,评估滤波效果。验证评估测试完成后,在综合下载到板上。该流程如下所示:

硬件在环 (Hardware in the Loop, HIL)是一种半实物实时仿真技术,实现整个系统的半实物实时仿真测试,可以方便快速实现设计方案的验证与优化,缩短开发周期,降低研发成本。HIL先后在航天航空、军事、汽车等领域得到推广应用。

????硬件在环是一种半实物(FPGA)实时仿真(simulink)技术,利用该原理可以将FPGA和simulink联合起来,通过PC与FPGA的物理连线,实现FPGA和PC端simulink之间的通信,目前该物理连接方式有以太网和JTAG两中方式,其实这个连接的原理与Quartus II 的signaltap类似,都是在FPGA中生成相应的模块,负责信息数据的接收和发送来完成整个硬件在环的通信过程,如果之前接触过signaltap,理解起来就相对简单容易。

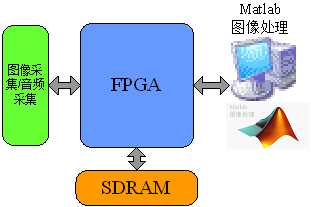

????由此,采用硬件在环有什么好处呢?采用硬件在环就可以省略了modelsim这中间环节,在简单的实验中,直接进行板级验证,直接在simulink上的生成待测试的信号,再将待测试的信号,通过以太网或者JTAG接口传送到FPGA,然后再将FPGA处理后(采集到)的信号传送到simulink进行分析,由此加快RTL的设计验证过程。

????同时,该方法也可以应用于图像/音频处理领域,通过FPGA采集图像/音频信号,再通过硬件在环传送回PC端的simulink(在此可以将FPGA视为一个采集预处理板卡的功能),然后在simulink端做处理和分析,由此可以降低购买图像或者音频采集板卡的成本,并且将PC端的simulink和FPGA联合起来形成一个实时的处理系统,具有很大的意义。

标签:

原文地址:http://www.cnblogs.com/logic3/p/5616363.html