标签:

????在simulink创建测试模块,通过测试模块产生信号,再传送到FPGA,FPGA读出后再将信号无处理传送回simulink进行显示。由此来测试整个硬件在环的功能是否正常,并且熟悉整个基础开发流程。

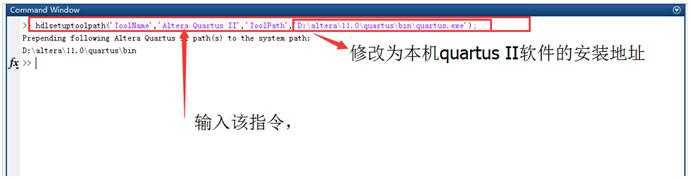

????在Matlab的指令窗口输入以下指令,hdlsetuptoolpath(‘ToolName‘,‘Altera Quartus II‘,‘ToolPath‘,‘C:\altera\11.0\quartus\bin\quartus.exe(修改为软件安装的路径)‘)。

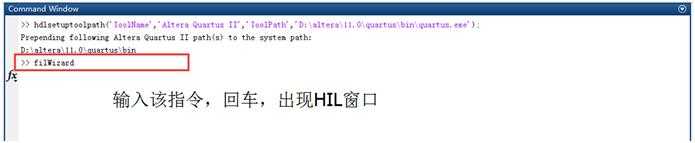

????Simulink菜单操作 Verification Wizards -> FPGA-in-the-Loop (FIL)....

或Matlab 提示符输入:filWizard。

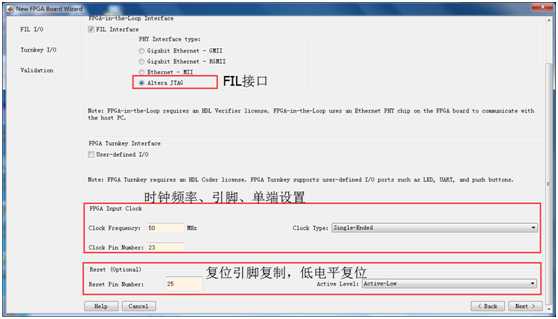

????在实验开始之前,需要根据大西瓜开发板的设计原理图,对开发板的信息进行配置,主要是对时钟信号和复位信号、采用的FIL的通信接口进行配置,如下图所示。

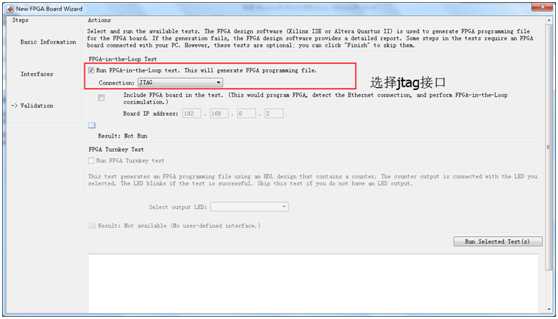

????在board name的选项中选择创建新的用户板卡。连接方式采用JTAG进行连接,大西瓜FPGA板卡上没有以太网,由此采用JTAG接口。

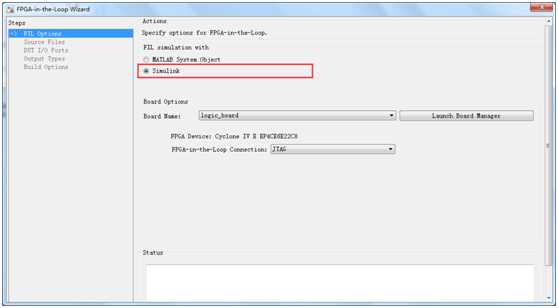

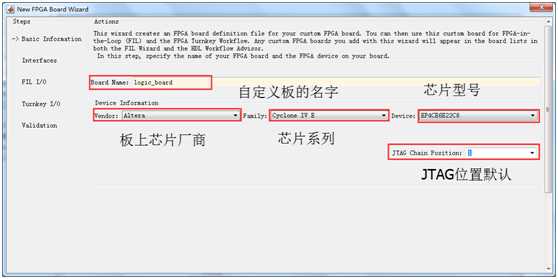

????在板卡的配置信息窗口中,首先进行板卡上FPGA芯片信息的配置,如下图所示。

设置板卡的名字logic_board,FPGA的厂商为Altera,芯片为cyclone IV E,选择对应的芯片类型 EP4C6E22C8,JTAG链位置默认。

设置板卡的名字logic_board,FPGA的厂商为Altera,芯片为cyclone IV E,选择对应的芯片类型 EP4C6E22C8,JTAG链位置默认。

????JTAG接口类型,时钟信号的频率、引脚号、时钟类型,复位信号的引脚号,复位的电平信息的设置,如下图所示。

?

保存板子的配置信息,在接下来的实验均要使用到该信息文件。

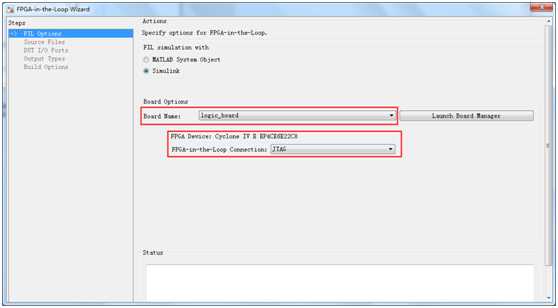

????在board name中选择前面配置好的板卡信息,板卡名为logic_board,选择JTAG接口,点击next。

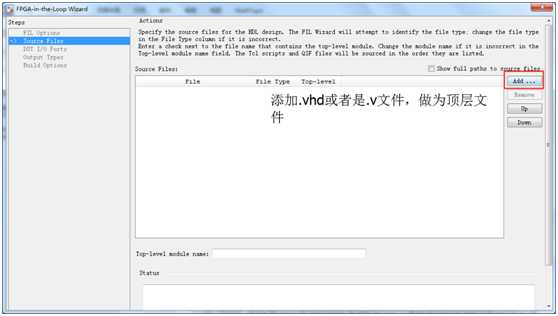

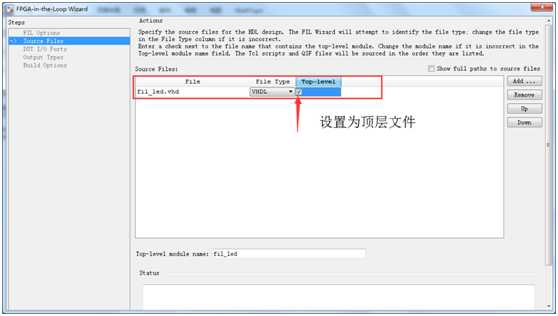

????添加RTL文件,即设计的verilog或者是VHDL设计的代码文件,并将该文件设置为顶层文件。

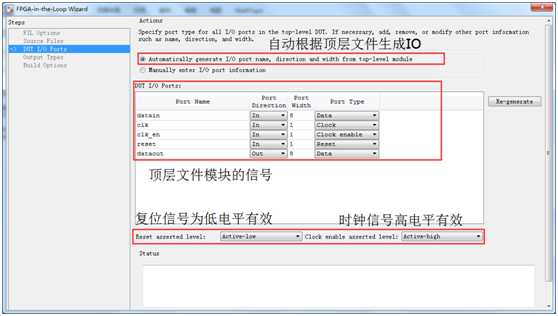

????选择自动根据顶层文件生成IO,各个IO的详细信息在栏目中,IO的类型的也是很重要的,在以后的设计中要主要IO类型选择的正确。同时对复位信号的电平和时钟使能信号的电平进行设置。如下图所示。

?

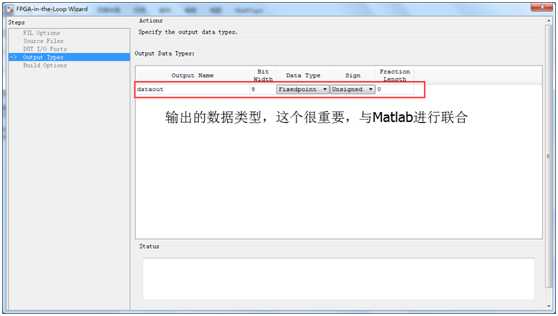

????输出信号类型,这里可能会和前面的IO混淆,其实这里的信号是前面IO中由FPGA输出到simulink中的信号,这里的信号是dataout,该信号输出到simulink中,信号的位宽为8bit。

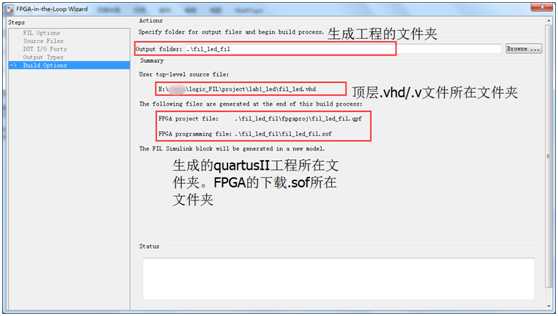

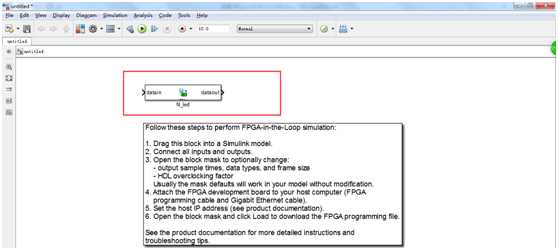

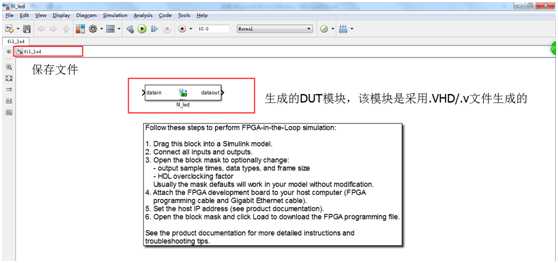

生成simulink模型和硬件模型,输出的文件类型和文件所在文件夹如下图所示。

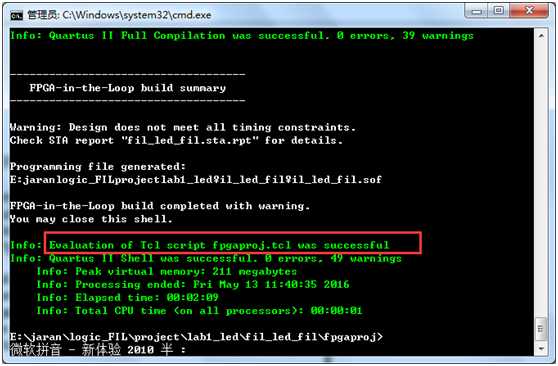

????当出现上图中,红色标注的信息时,simulink模型和硬件模型创建成功,接下来进行simulink模型的设计和硬件的下载验证。

RTL代码如下所示:

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.numeric_std.ALL; ? ? ENTITY fil_led IS port( datain : in std_logic_vector(7 downto 0); dataout: out std_logic_vector(7 downto 0); clk: in std_logic; clk_en: in std_logic; reset: in std_logic); end entity; ? architecture rtl of fil_led is begin ? process(clk) begin if clk‘event and clk=‘1‘ then if reset = ‘0‘ then dataout <= (others => ‘0‘); elsif clk_en = ‘1‘ then dataout <= datain; end if; end if; end process; ? end rtl;? |

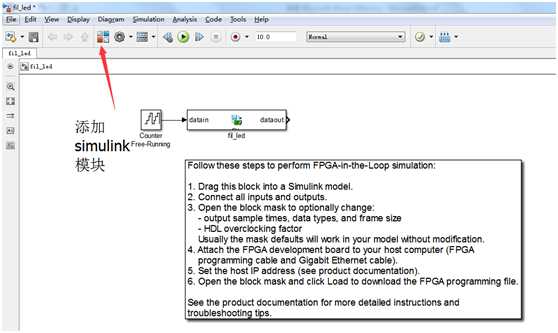

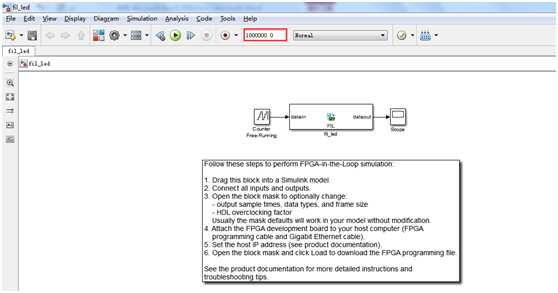

把Matlab产生的信号,通过JTAG接口输出到FPGA然后,FPGA再通过JTAG传送到Matlab,用于测试整个环路。

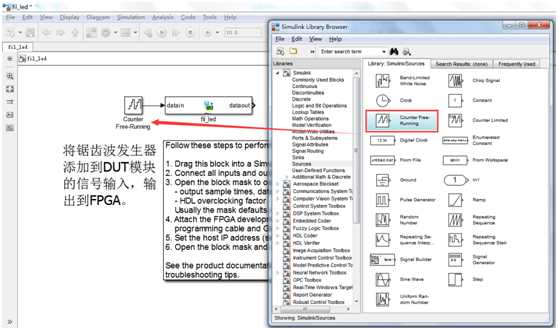

添加锯齿波产生模块,如下图所示:

?

?

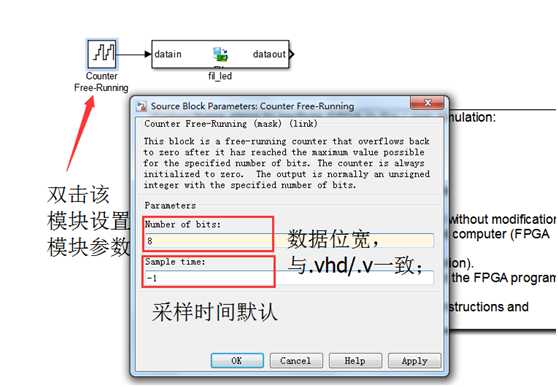

????设置锯齿波模块的参数。

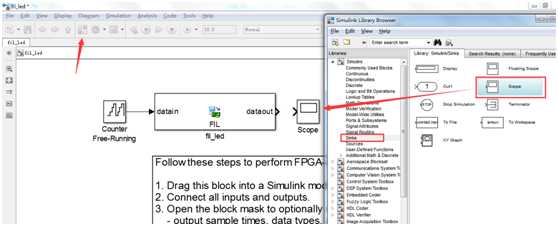

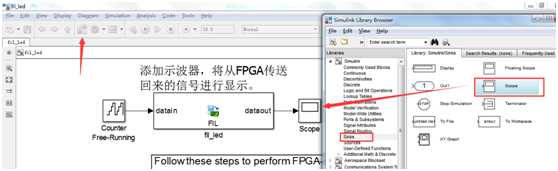

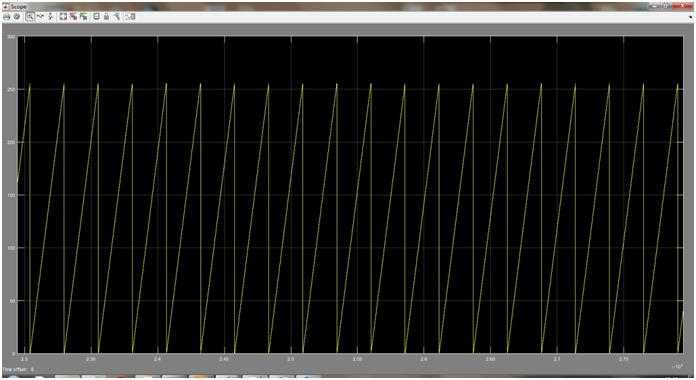

????添加示波器模块,如下图所示。

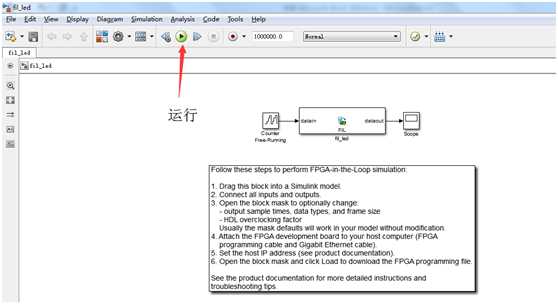

修改运行的时间

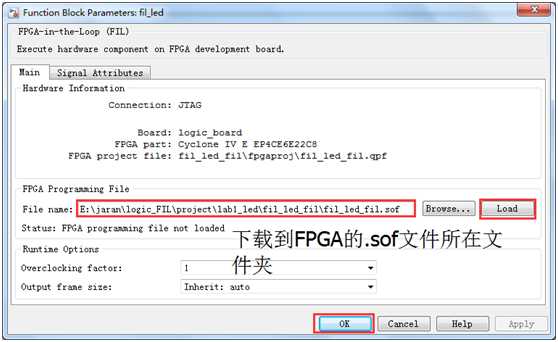

双击fil_test模块,下载硬件sof文件(由此,该实验中硬件模型没有修改,由此,直接选择默认的sof保存路径,接下来的实验中,由于硬件模型修改了,所以直接在Quartus II工程中下载)。

?

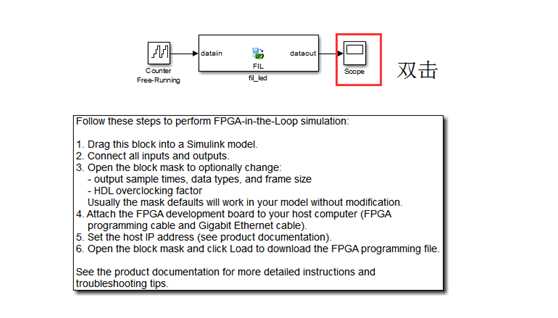

双击示波器后出现

标签:

原文地址:http://www.cnblogs.com/logic3/p/5616544.html