标签:

通用序列总线(USB) 从1996问世以来,一统个人电脑外部连接界面,且延伸至各式消费性产品,早已成为现代人生活的一部分。2000年发表的USB 2.0 High-speed规格,提供了480Mbps的传输速率,至今已超过十年的历史,随着高分辨率的影音应用逐渐普及,动辄GByte等级的影音资 料,USB 2.0的频宽已经逐渐捉襟见肘。

USB协会在2008年,提出新一代的USB 3.0传输规格,将USB的频宽上推十倍达5Gbps及全双工双向传输,并且兼容的连接器设计可以确保装置的向下兼容性,并提升供电电流从5V 500mA至5V 900mA。随着装置端及主控端的控制芯片陆续问世,Intel及AMD陆续将USB 3.0主控端纳入参考设计,并计划推出原生支持芯片组,USB 3.0的普及终成定局。而其中普及的关键,就是由intel订定的主控端接口规格定案版本:eXtensible Host Controller Interface(xHCI)1.0。

USB 3.0系统架构及主控端设计

USB系统的实体装置包括三种类:主控端(Host),周边端(Peripheral)及集线器 (Hub)。周边端(Device)负责提供单一或多样的功能性,例如提供人机接口装置(Human Interface Device):键盘鼠标;影像装置:扫描仪、webcam;储存装置:外接硬盘、U盘等。集线器介于主控端及周边端,提供上下层信息的传递与交换以提供 简单易用的装置扩充联接性。

主控端是USB系统中的核心运作装置,系统中的装置控制及数据传递皆由主控端发起。主控端的运作由硬件及软件相互配合完成下列工作,主控端的运作均须仰赖USB主控端系统中软硬件层次:

●侦测装置的连接或移除

●管理主控端及周边装置的控制流程

●管理主控端及周边装置的数据流

●管理并统计系统运作状态

●提供USB装置的电源

●装置端的启动及设定

●数据传输的排程

●装置端电源管理

●USB总线管理

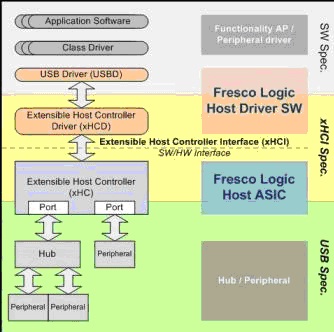

图1 USB 3.0系统运作的系统区块图

图1中的虚线代表软硬件的区分线,软硬件的沟通则遵循xHCI界面规格。虚线以上的区块表示主控端的软件部分,包含下列四大软件层:

●Application Software:通过Class Driver所提供的标准类别服务,提供使用者USB周边装置的所提供的特定功能;

●Class Driver Software:在主控端PC执行USB的特定类别功能。如储存类别软件,人机接口类别软件,声讯类别等;

●USB Driver(USBD):对应操作系统以及xHCD驱动程序的软件层,向上经标准USB Driver界面(USBDI)与操作系统或装置之Class Driver传递信息;

●Host Controller Driver(xHCD):经由xHCI界面与主控端控制器沟通的软件层,提供USB Driver及xHC控制器的软硬件沟通界面。

软件层部分,Application Software及Class Driver Software提供使用者操作周边装置端功能,由操作系统或装置厂商提供。而USB Driver及Host Controller Driver则是与控制器的运作紧密配合,目前多是由USB 3.0控制器的厂商研发提供。

图1虚线以下的部分表示USB系统中的硬件实现,包括一个主端控制器硬件及多个集线器、多个周边装置。

●Host Controller(xHC)主控端控制器:USB 3.0主控端的硬件ASIC,提供xHCI界面供软件执行指令及传递信息;提供支持LS/FS/HS及SuperSpeed运作速度之下行实体连接端口。 硬件设计则必须遵循两大主要规格:xHCI及USB 3.0规格。

●USB Device周边装置:提供特定功能的USB硬件装置,或扩展USB总线的集线器硬件。

综合以上架构,主控端的整体设计可以分成软件硬件两大部分:

1. xHCI软件,包括xHC Driver及USB Driver;

2. xHCI硬件,包括对应软件的xHC Controller,以及提供USB连接的USB Port部分。

xHCI 0.96与1.0比较

xHCI规格是由Intel制定。2008年8月首次发布0.9初步版本,首次定义USB 3.0主控端与PC软硬件接口规格,设计之初便以USB 3.0为主要应用对象,并保留对应未来更高频宽界面的可缩放性。

2009年5月,Intel发布0.96版本,也是早期设计的USB 3.0 Host Controller兼容的版本。2010年5月,Intel发表正式定案1.0版本,成为目前USB 3.0主控端规格的最终版本。xHCI 1.0版本也将成为未来USB 3.0控制器的主流规格。

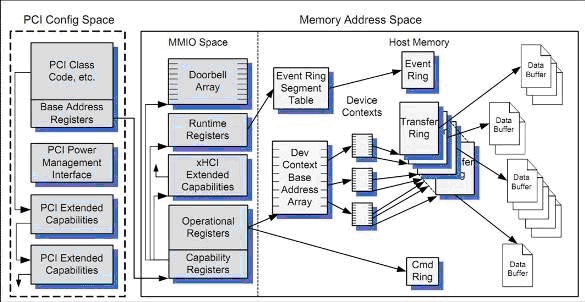

图2 xHCI的基本运作

xHCI定义在现今的PC系统中,软件存取PCI Express的PCI Config Space、MMIO Space,执行USB 3.0主控端所需的控制及快速数据传输。xHCI以Ring作为所有动作执行的基本数据结构,为一环状的储列数据结构,包含三种类:

●Command Ring:系统软件以Command Ring发出指令给主控端控制器硬件(xHC)

●Event Ring:主控端控制器以Event Ring回传状态及执行结果给系统软件

●Transfer Ring:用来在系统内存及端点(Endpoint)两端搬移数据。Transfer Ting包含多组的Transfer Descriptor,TD由一组或多组Transfer Ring Block(TRB)组成,为xHCI数据结构中之基本传输单位。系统软件通过TRB来传输数据区块,包括一组数据缓冲指针,及状态及控制单元。

xHCI 1.0修正了超过20章节以上,以厘清xHCI规格发展过程中,定义模糊或争议的部分,并纳入主要开发者的回馈意见,也被认为是未来支持原生USB 3.0芯片组的设计规格定案。xHCI 1.0也新增了部分设计,藉此提升整体系统效率及使用者体验。以下列举几项较重要的改善功能。

较少的软件中断

在一般的运作下,每个Event TRB在Event Ring结束时,会触发软件中断,使CPU必须进入service routine处理软件中断。然而这些软件中断并非都是必须且有意义的,xHCI 1.0对此现象,在Normal TRB及Isoch Transfer TRB加入Block Event Interrupt(BEI)旗标,允许系统发送Event TRB而不会产生软件中断。较少的软件中断意味着CPU被占用的时间将会降低,对CPU的依赖程度也会降低,等效于提升传输的效能。

错误处理

USB为支持热插拔之开放界面,大多数的兼容性问题都需要靠错误处理来回复,减低使用者的不便。 xHCI 1.0新增了Soft retry机制,当发生USB传输错误的时候,周边装置端不知道主控端已经停止部分endpoint,会持续等待主控端的再次尝试。Soft retry机制可针对此状况给予多次尝试,回复错误。

使用于影音应用的ISOCH传输,由于不支持CErr的错误回复,xHCI 1.0也为此加入较严谨之错误回复机制。

低功耗模式的支持

xHCI 1.0支援Save and Restore Operations。针对PC系统上的省电模式如Sleep、 Hibernate、Save and Restore Operations可使USB系统在进出省电模式时省却重新启动内部状态的繁复步骤,迅速的进出省电状态。特别针对不会移除的周边装置,如内建的视频摄像头等。此外对于USB 2.0 Link Power Management(LPM)的支持,xHCI 1.0也一并更新对于支持USB2 LPM硬件控制机制。

USB 3.0主控端认证

USB协会目前已开始认证支持xHCI 1.0的主控端控制器,其中的xHCI CV(Command Verifier)测试程序会针对主控端进行xHCI的细部规格测试,确保主控端控制器符合xHCI设计规范。Microsoft WLK 1.5版本已宣告在未来系统上的USB 3.0主端控制器必须符合xHCI 1.0规范。这一测项,也将成为未来Windows对于USB 3.0主端控制器的内建驱动程序的开发依据。

至于USB协会对于主控端的认证包括三大部分:

电气特性量测

测试USB 3.0装置的实体层及线路设计是否符合USB 3.0规格的电气特性规范,包含传输端及接收端。传输端测试包含5Gbps信号质量眼图、展频规范、时基误差规范等。接收端测试包含在多组特定时基误差规 范下的位错误率。电气特性量测确保所有USB 3.0实体层设计能有基本传输接收兼容性。同时,USB 2.0的向下兼容信号,也必须符合USB 2.0的规范。

xHCI/USB Command Verifier测试

主控端的Command Verifier(CV)测试不同于周边装置,除了周边装置的USB CV,主控端还必须针对xHCI的设计部分进行CV测试。CV测试针对待测物的硬件设计,进行xHCI及USB的细项规范验证,确保待测物的硬件设计完全符合xHCI及USB规范,其中针对xHCI 1.0的测项,也是以此执行。

兼容性测试

USB协会对于主控端控制器的兼容性非常重视,主控端对于USB 3.0及USB 2.0的周边,都必须经过详细的兼容性交互测试,确保未来市售产品的质量。

主控端的兼容性测试包括两大项目:Gold tree测试及大量USB 3.0及USB 2.0周边装置测试,考验主控端硬件及软件的功能完整性及错误处理能力。Gold Tree测试为超过10种以上的包含各种类别(Class)的装置,以多层USB 3.0及USB 2.0集线器连接成树状,而合格的主控端软硬件必须能同时使所有的装置运作,且具备正确的插拔、休眠、及错误处理能力。主要考验的硬件设计是否能够处理极 端的多装置状况,及软件设计是否有完整支持各类型装置和错误处理能力。此外,协会会以取得认证的USB 3.0/2.0装置,总数超过200只以上,横跨所有USB定义的类别,逐一测试主控端的兼容性。

结论

随着Intel及AMD陆续导入USB 3.0参考设计及未来的原生支持,USB 3.0以确立成为主流外部连接接口。10倍的频宽,也将把应用带往实时、高分辨率影音的编辑及输出入发展,不再局限于大容量储存装置。主机板上的端口数也 将从早期的1-2个接口,持续增加至6-10个接口,并导入前面板支持,也将考验主控端控制器厂商的模拟设计能力及多接口数的频宽处理能力

标签:

原文地址:http://www.cnblogs.com/zxc2man/p/5631015.html