标签:

通过《基于modelsim-SE的简单仿真流程》和《调用altera IP核的仿真流程》是否感受到仿真流程中的繁琐步骤,特别是在modelsim创建工程之后的步骤:编译、添加仿真信号、开始仿真。这三个步骤涉及到一大堆的鼠标操作,涉及到一大堆的窗口操作,由于RTL仿真过程是一个反复迭代的过程,同时要求覆盖到100%的功能测试,由此也要覆盖到所有状态机和条件判断的所有情况,由此,RTL的功能仿真功能需要不断的修改RTL代码,每次修改RTL代码都需要进行编译、添加仿真信号、开始仿真,这要是用鼠标操作这得多累人。

由此,需要采用脚本的方式编写*do文件,将编译、添加仿真信号、开始仿真这三个步骤采用脚本的方式进行,只需在脚本执行窗口输入*.do文件,并执行就可以解决以上的问题。

编写测试操作脚本,需要对modelsim的脚本有所了解

|

脚本语言 |

说明 |

|

vlib work |

新建工作目录 |

|

vmap work work |

将新建库映射到当前工作目录 |

|

Vlog D:/***/*.v -cover bcesxf |

Vlog:编译文件,需要文件的所在地址及文件名; -cover bcesxf:覆盖分支条件表达式语句 |

|

vsim -novopt work.(待测试的模块名) |

Vsim:加载仿真 -novopt:不进行优化 |

|

add wave -decimal /(待测试的模块名)/* |

add wave:添加仿真信号; -decimal:表示十进制有符号表示; -unsigned:表示十进制无符号; -hex:表示十六进制表示; /(待测试的模块名)/:将待测试的模块添加到单斜杠里面; *:表示整理模块里面的所有信号,也可以将*替换为具体的信号; |

|

run 1ms |

run 进行仿真,后面带仿真时间长度; |

本实验在《调用altera IP核的仿真流程》的实验上进行修改,使用的RTL代码、创建工程的过程和《调用altera IP核的仿真流程》一致。将步骤编译、添加仿真信号、开始仿真采用脚本的方式进行操作,编写的脚本如下(带#号为注释,注释用#号),在将脚本文件编写完成后,需要将文件保存为.do的后缀,然后保存到工程所在的文件夹,不需要包含到modelsim工程中。

|

#Creat a work lib vlib work

#Map the work lib to current lib vmap work work

#Compile the source files # -cover bcesxf 覆盖分支条件表达式语句 vlog E:/jaran/modelsim/lab2/altera_mf.v -cover bcesxf vlog E:/jaran/modelsim/lab2/rom_tst.v -cover bcesxf vlog E:/jaran/modelsim/lab2/rom_top.v -cover bcesxf vlog E:/jaran/modelsim/lab2/rom.v -cover bcesxf vlog E:/jaran/modelsim/lab2/counter.v -cover bcesxf

#Start simulation vsim -novopt work.rom_tst

#add wave add wave -unsigned /rom_top_1/* # add wave -hex /rom_top_1/* # add wave -hex/rom_tst/* # add wave -hex/rom_tst/clk #set run time run 1ms |

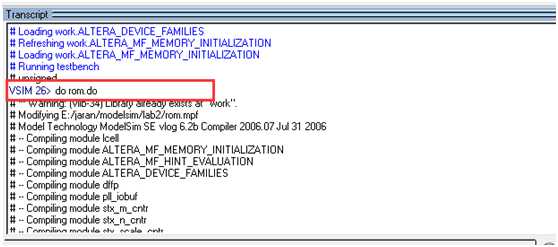

编写、保存为rom.do文件,在脚本窗口输入do rom.do,然后按下回车键。

软件便进行编译、添加仿真信号、开始仿真。

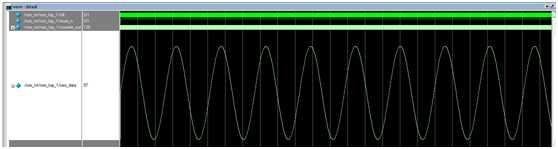

仿真完成后,波形窗口产生相应的信号,如下所示。

将rom_data显示为模拟信号会得到如下的结果,与实验《调用altera IP核的仿真流程》一致。

采用脚本的方式,解决了仿真过程繁琐的操作过程,极大地加快了仿真的过程,该方式高效便捷专业,是采用modelsim进行仿真所要首推的方式。

标签:

原文地址:http://www.cnblogs.com/logic3/p/5636948.html