标签:

FPGA DDR3调试

Spartan6 FPGA芯片中集成了MCB硬核,它可以支持到DDR3。在Xilinx的开发工具Xilinx ISE中提供了MIG IP核,设计者可以用它来直接生成 DDR3 控制器设计模块,并通过 MIG 的 GUI 图形界面完成相关配置。

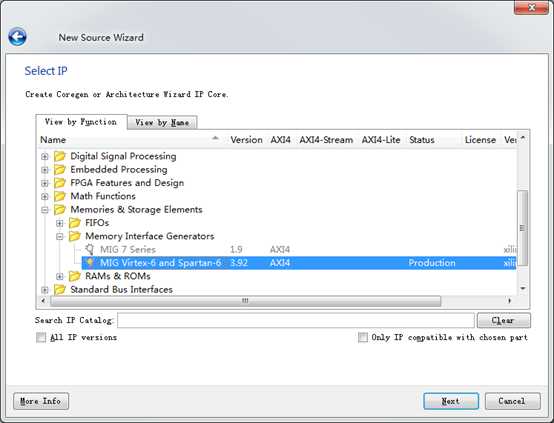

首先,建立ISE工程,并添加MIG IP核,

接下来进行MIG IP核配置,这里列出主要的部分,

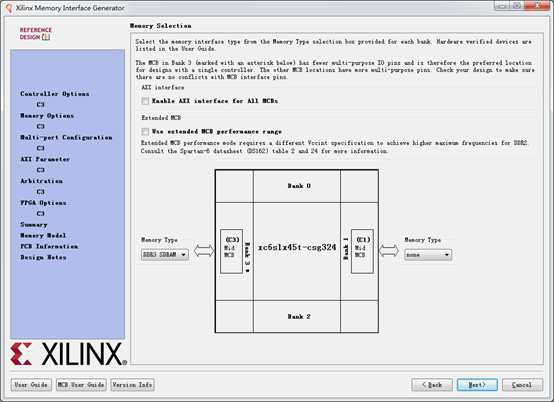

这里选择DDR的类型,并选择使用Spartan6的哪一个bank,一般选择左边的bank,

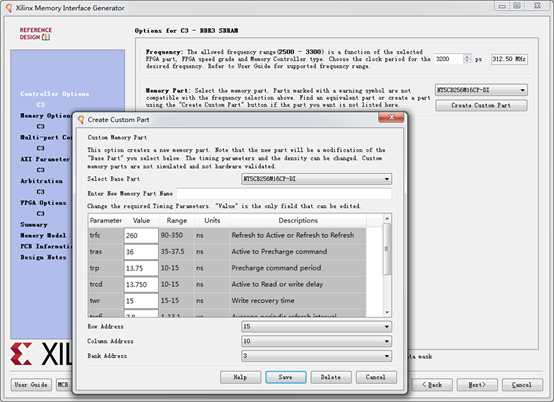

这里设置DDR3的时钟频率以及DDR3的设备型号,Xilinx列举了部分DDR3型号,如果没有,则需要点击“create custom part”自定义型号,这里注意在自定义型号的时候最好选择一个模板与自己的DDR3型号数据位宽一样的,因为自定义选项中无法修改数据位宽(当然也可以在生成的代码中修改位宽),在自定义界面中,主要设置与DDR3有关的几个时间参数以及地址线宽度,这些信息都可以在芯片的Datasheet上找到,

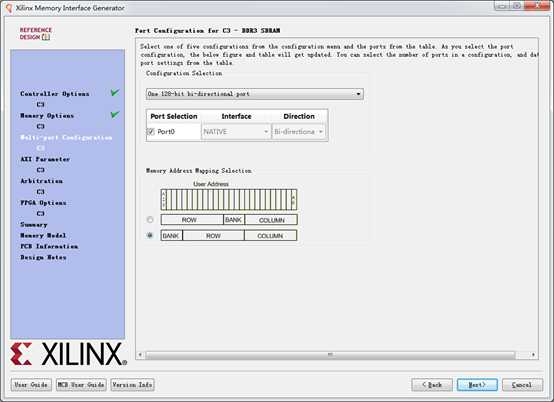

这里选择不同的端口方式,可以选择一个端口,也可以选择不同位宽的多个端口,选择多个端口时,可以对不同的端口进行读写控制,这在乒乓模式操作DDR3时有用(如利用P0端口对地址1进行写操作,同时利用P1端口对地址2进行读操作;完成一次读写时,P0端口对地址2进行写操作,同时利用P1端口对地址1进行读操作),以及地址映射关系(可以查看:Spartan-6 FPGA Memory Interface Solutions 和 Spartan-6 FPGA Memory Controller),

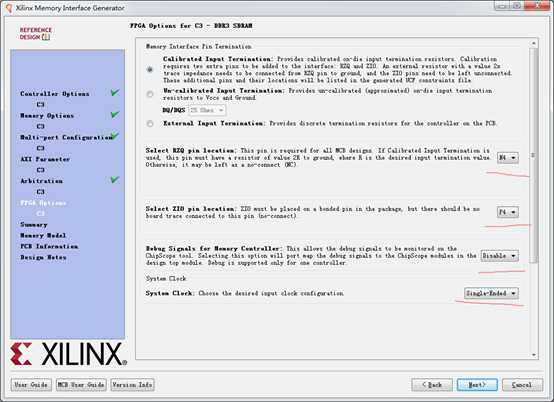

这里设置RZQ和ZIO的引脚,需要根据硬件电路来进行选择,同时可以选择是否使用chipscope调试,如果自己添加chipscope的话就不需要。

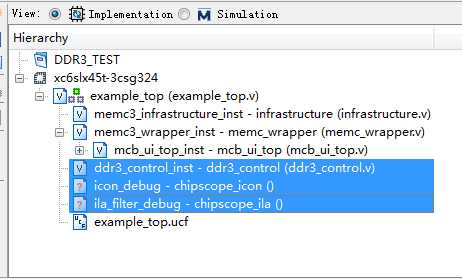

生成MIG IP核以后,可以新建工程,在user_design文件下拷贝以下文件(选中部分为自己添加),然后进行代码修改。

首先,完成约束文件的修改,使之与自己的硬件设备一致,一般有以下几点:

1、 VCCAUX 电压修改

CONFIG VCCAUX=3.3; # Valid values are 2.5 and 3.3

2、 系统时钟输入的周期,需要跟PCB板上的晶振频率一样。

NET "memc3_infrastructure_inst/sys_clk_ibufg" TNM_NET = "SYS_CLK3";

TIMESPEC "TS_SYS_CLK3" = PERIOD "SYS_CLK3" 20 ns HIGH 50 %;

3、 修改部分管脚电压和位置,如时钟、复位管脚等

接下来完成顶层文件的设置,一般有以下几点:

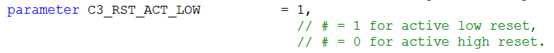

1、 复位极性与PCB板一致

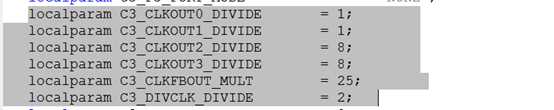

2、 根据板子上的时钟修改DDR3时钟配置部分,我使用的时钟输入为50Mhz,由于在MIG中设置了 DDR3 的频率为312.5MHz,且DDR3是上下沿采样,所以FPGA内部 DDR3控制器的时钟需要625MHz,所以这里先把时钟频率倍频25, 再分频2,得625Mh的CLKOUT0和CLKOUT1, 再分频 8分别得到 user interface 的时钟和 calibration 的时钟 78.125Mhz。

3、 删除mcb_traffic_gen相关例化代码,编写自己的DDR3测试代码,并例化

4、 编写DDR3测试代码,需参考Spartan-6 FPGA Memory Controller中的读写时序,主要参考,主要包含命令、数据、地址,本测试中,由于采用了128bit的单端口,所以每写一个数据,地址线需要加8,若涉及到突发读写,则地址线也要相应按8的倍数增加。

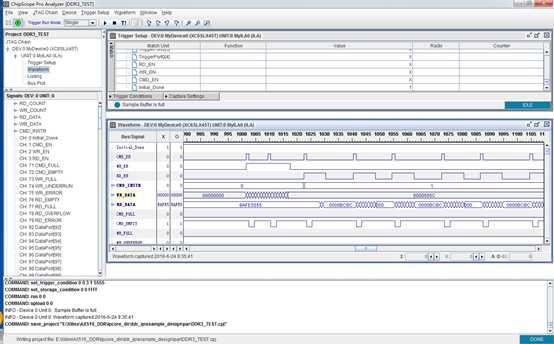

5、最后添加chipscope,完成测试

标签:

原文地址:http://www.cnblogs.com/yangjun1219/p/5647947.html