标签:

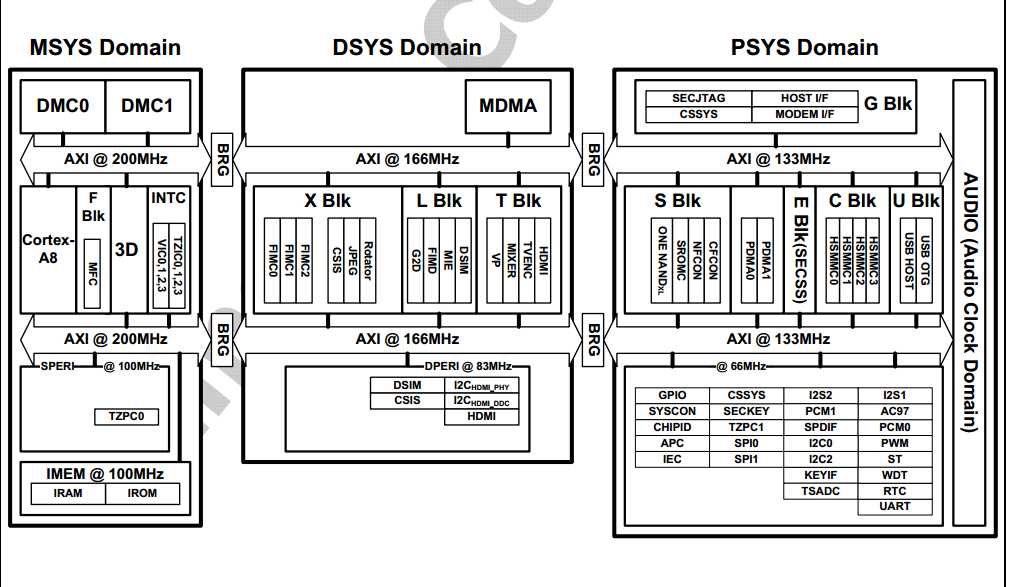

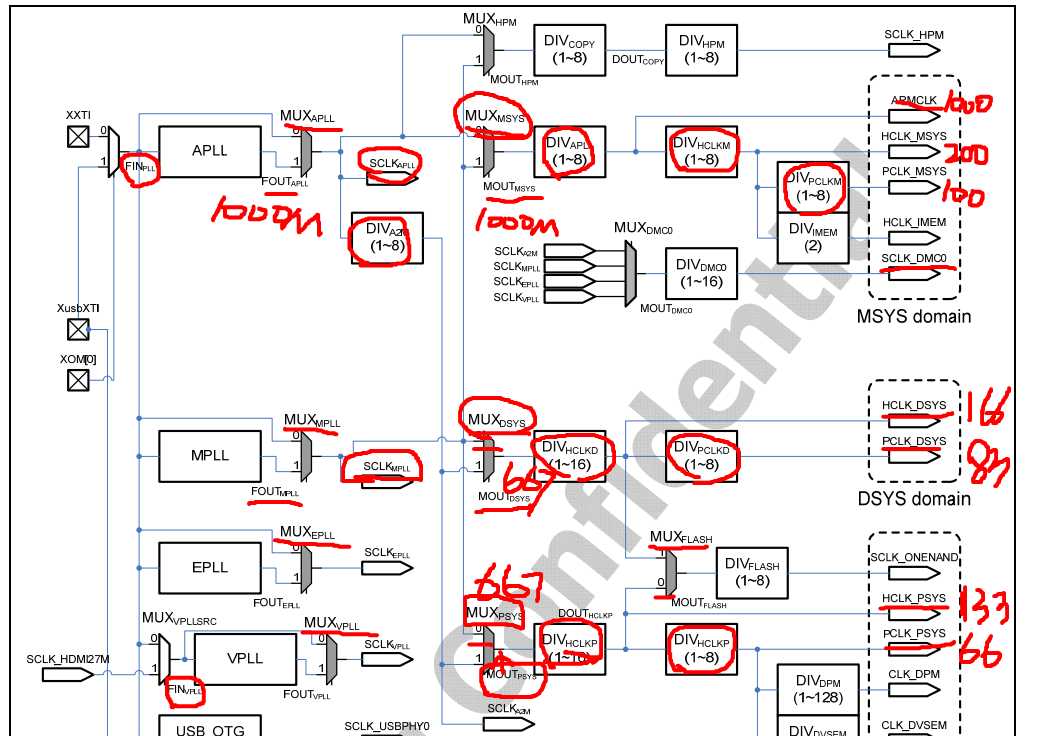

S5PV210一共有三个时钟域:MSYS,DSYS,PSYS

MSYS:(main system)主时钟域,包括CPU,DDR内存条,IROM和IRAM等

DSYS:(display system)显示时钟域,就是一般的和视频有关的就在这个时钟域中,如HDMI,TVENC。。。

PSYS:(peripheral system)外围时钟域,就是GPIO接口,I2C接口,UART接口等这些外围设备就在这个时钟域上。

每个时钟域通过一条BRG(异步总线的桥梁)连接在一起。

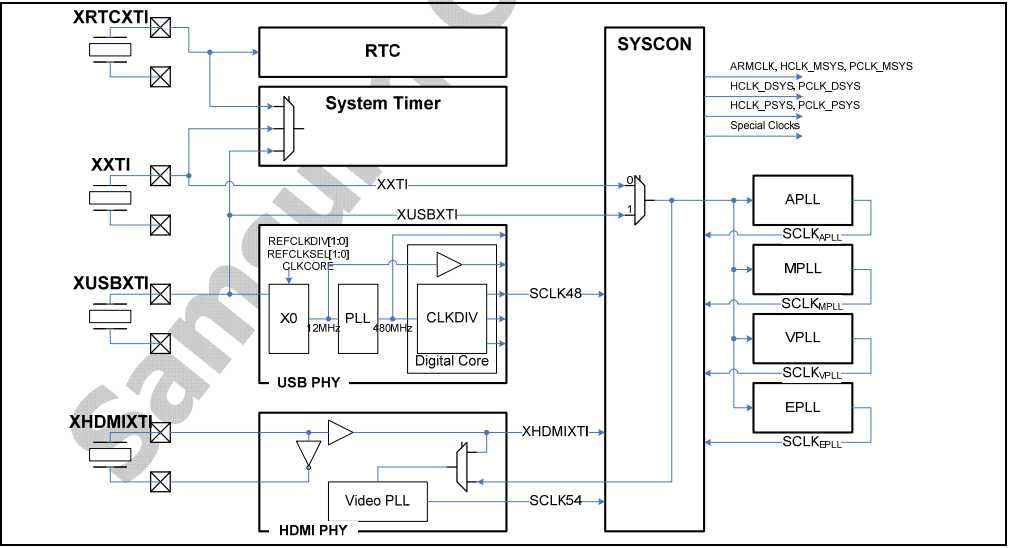

常见的时钟的来源:

外部直接输入时钟信号,SoC有个引脚用来输入外部时钟信号,用的很少。

外部晶振+内部时钟发生器产生时钟,大部分低频单片机都是这么工作的。

外部晶振+内部时钟发生器+内部PLL产生高频时钟+内部分频器分频得到各种频率的时钟,210属于这种。

上图可见:我们的210芯片,一般是从XXTI这个接口进入,这个接口连接外部晶振(规定是24MHz),然后进入内部时钟发生器(syscon),再分别进入4个PLL,分别产生4种不同的高频时钟,各个高频时钟再经过内部的分频器分频得到各种频率的时钟。

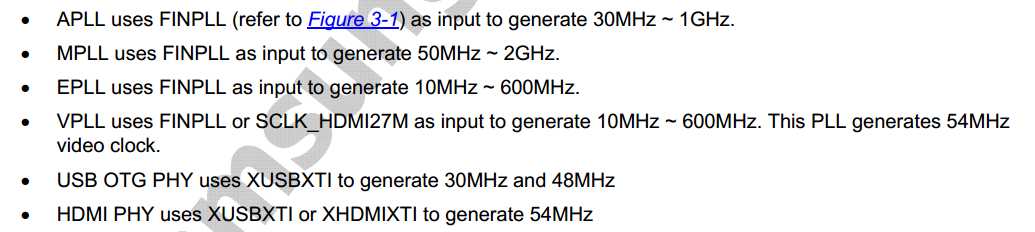

下面是各种PLL可以产生的时钟的频率的范围:

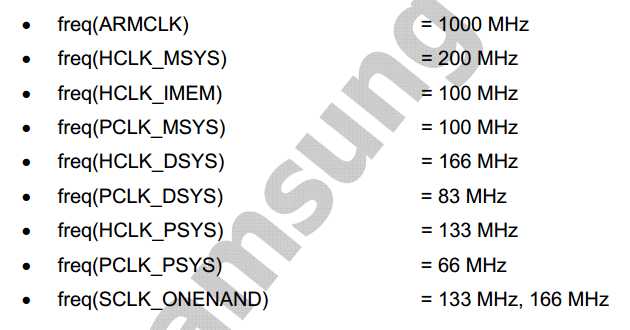

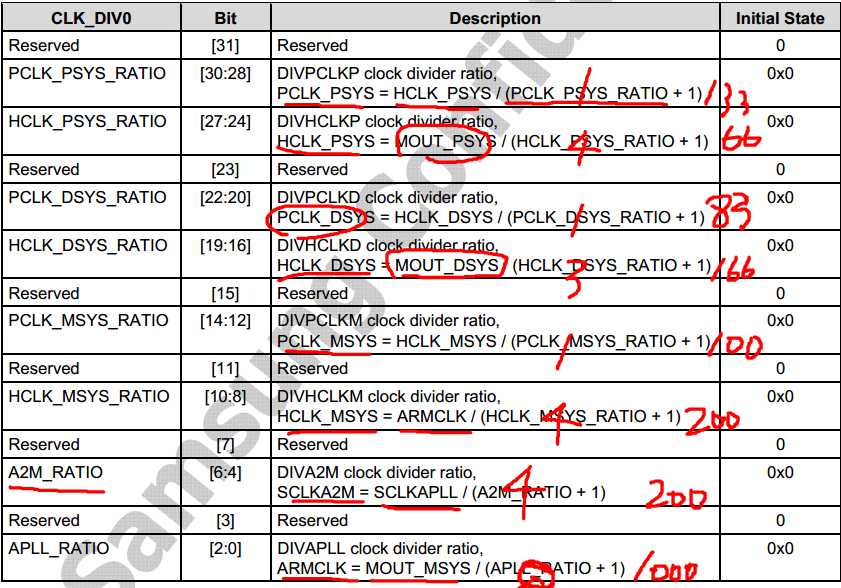

HCLK_DSYS:DSYS时钟域的高频率线;

PCLK_DSYS:DSYS时钟域的低频率线;其他的依次类推

设置时钟的时候一共有五个步骤:

1 rREG_CLK_SRC0 = 0x0; 它所起的作用:就是让我们的暂时不用PLL,只使用原始时钟24MHz

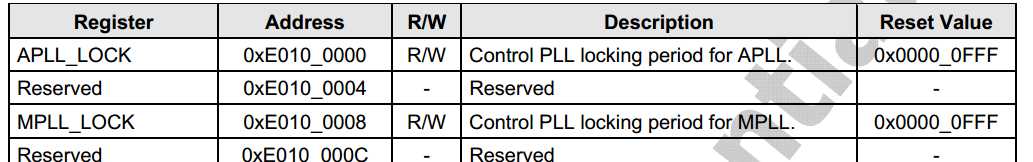

1 rREG_APLL_LOCK = 0x0000ffff;

2 rREG_MPLL_LOCK = 0x0000ffff;

使用的都是默认值:

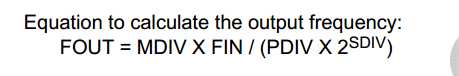

1 rREG_CLK_DIV0 = 0x14131440;

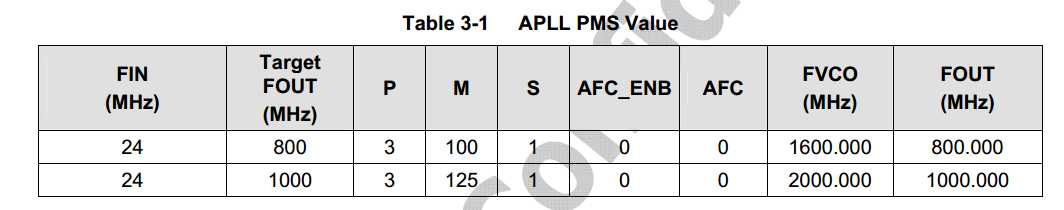

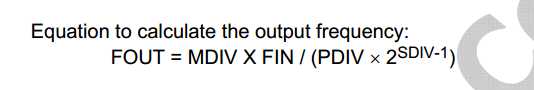

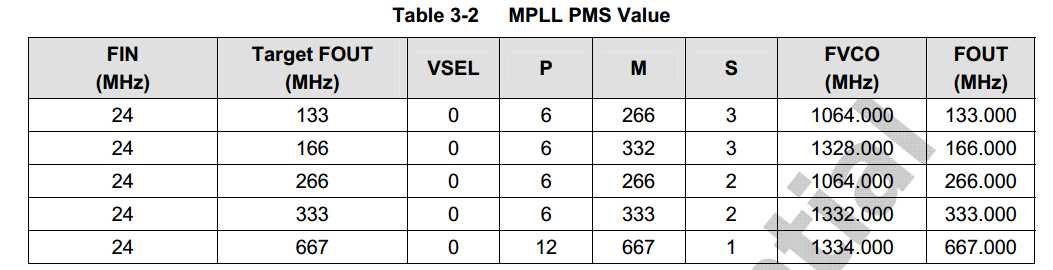

1 // FOUT = MDIV*FIN/(PDIV*2^(SDIV-1))=0x7d*24/(0x3*2^(1-1))=1000 MHz 2 rREG_APLL_CON0 = APLL_VAL; 3 // FOUT = MDIV*FIN/(PDIV*2^SDIV)=0x29b*24/(0xc*2^1)= 667 MHz 4 rREG_MPLL_CON = MPLL_VAL;

计算的数据和公式都是已经给出来了的,其中M对应MDIV,P对应PDIV,S对应SDIV

上面对应的APLL的数据和公式,我们是设置1000MHz的,所以M,P,S的值就是:125,3,1,带入公式就可以了

下面对应的是MPLL的数据和公式,我们是设置667MHz的,所以M,P,S的值就是:667,12,1,带入公式就可以了

1 REG_CLK_SRC0 = 0x10001111;

就这样就完成了时钟的设置了。

最后附上完整的代码:

1 // 时钟控制器基地址 2 #define ELFIN_CLOCK_POWER_BASE 0xE0100000 3 4 // 时钟相关的寄存器相对时钟控制器基地址的偏移值 5 #define APLL_LOCK_OFFSET 0x00 6 #define MPLL_LOCK_OFFSET 0x08 7 8 #define APLL_CON0_OFFSET 0x100 9 #define APLL_CON1_OFFSET 0x104 10 #define MPLL_CON_OFFSET 0x108 11 12 #define CLK_SRC0_OFFSET 0x200 13 #define CLK_SRC1_OFFSET 0x204 14 #define CLK_SRC2_OFFSET 0x208 15 #define CLK_SRC3_OFFSET 0x20c 16 #define CLK_SRC4_OFFSET 0x210 17 #define CLK_SRC5_OFFSET 0x214 18 #define CLK_SRC6_OFFSET 0x218 19 #define CLK_SRC_MASK0_OFFSET 0x280 20 #define CLK_SRC_MASK1_OFFSET 0x284 21 22 #define CLK_DIV0_OFFSET 0x300 23 #define CLK_DIV1_OFFSET 0x304 24 #define CLK_DIV2_OFFSET 0x308 25 #define CLK_DIV3_OFFSET 0x30c 26 #define CLK_DIV4_OFFSET 0x310 27 #define CLK_DIV5_OFFSET 0x314 28 #define CLK_DIV6_OFFSET 0x318 29 #define CLK_DIV7_OFFSET 0x31c 30 31 #define CLK_DIV0_MASK 0x7fffffff 32 33 // 这些M、P、S的配置值都是查数据手册中典型时钟配置值的推荐配置得来的。 34 // 这些配置值是三星推荐的,因此工作最稳定。如果是自己随便瞎拼凑出来的那就要 35 // 经过严格测试,才能保证一定对。 36 #define APLL_MDIV 0x7d // 125 37 #define APLL_PDIV 0x3 38 #define APLL_SDIV 0x1 39 40 #define MPLL_MDIV 0x29b // 667 41 #define MPLL_PDIV 0xc 42 #define MPLL_SDIV 0x1 43 44 #define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv) 45 #define APLL_VAL set_pll(APLL_MDIV,APLL_PDIV,APLL_SDIV) 46 #define MPLL_VAL set_pll(MPLL_MDIV,MPLL_PDIV,MPLL_SDIV) 47 48 49 #define REG_CLK_SRC0 (ELFIN_CLOCK_POWER_BASE + CLK_SRC0_OFFSET) 50 #define REG_APLL_LOCK (ELFIN_CLOCK_POWER_BASE + APLL_LOCK_OFFSET) 51 #define REG_MPLL_LOCK (ELFIN_CLOCK_POWER_BASE + MPLL_LOCK_OFFSET) 52 #define REG_CLK_DIV0 (ELFIN_CLOCK_POWER_BASE + CLK_DIV0_OFFSET) 53 #define REG_APLL_CON0 (ELFIN_CLOCK_POWER_BASE + APLL_CON0_OFFSET) 54 #define REG_MPLL_CON (ELFIN_CLOCK_POWER_BASE + MPLL_CON_OFFSET) 55 56 #define rREG_CLK_SRC0 (*(volatile unsigned int *)REG_CLK_SRC0) 57 #define rREG_APLL_LOCK (*(volatile unsigned int *)REG_APLL_LOCK) 58 #define rREG_MPLL_LOCK (*(volatile unsigned int *)REG_MPLL_LOCK) 59 #define rREG_CLK_DIV0 (*(volatile unsigned int *)REG_CLK_DIV0) 60 #define rREG_APLL_CON0 (*(volatile unsigned int *)REG_APLL_CON0) 61 #define rREG_MPLL_CON (*(volatile unsigned int *)REG_MPLL_CON) 62 63 64 void clock_init(void) 65 { 66 // 1 设置各种时钟开关,暂时不使用PLL 67 rREG_CLK_SRC0 = 0x0; 68 69 // 2 设置锁定时间,使用默认值即可 70 // 设置PLL后,时钟从Fin提升到目标频率时,需要一定的时间,即锁定时间 71 rREG_APLL_LOCK = 0x0000ffff; 72 rREG_MPLL_LOCK = 0x0000ffff; 73 74 // 3 设置分频 75 // 清bit[0~31] 76 rREG_CLK_DIV0 = 0x14131440; 77 78 // 4 设置PLL 79 // FOUT = MDIV*FIN/(PDIV*2^(SDIV-1))=0x7d*24/(0x3*2^(1-1))=1000 MHz 80 rREG_APLL_CON0 = APLL_VAL; 81 // FOUT = MDIV*FIN/(PDIV*2^SDIV)=0x29b*24/(0xc*2^1)= 667 MHz 82 rREG_MPLL_CON = MPLL_VAL; 83 84 // 5 设置各种时钟开关,使用PLL 85 rREG_CLK_SRC0 = 0x10001111; 86 }

参考来源:朱老师物联网大教程

标签:

原文地址:http://www.cnblogs.com/nibuyaoni/p/5731175.html