标签:

基于Verilog HDL整数乘法器设计与仿真验证

1.预备知识

整数分为短整数,中整数,长整数,本文只涉及到短整数。短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为0表示为正数),取值范围为-127~127。

负数的表示方法为正值的求反又加1。例如:

8’b0000_0100; //表示值:4,正值求反为:8’b1111_1011;再加1表示为:8’b1111_1100,这样便得到了-4的表示方法为:8’b1111_1100。

同理,负值变成正值的方法为:负值求反又加1。

2.设计思路

怎样判断一个短整数是正值还是负值?

利用一个数的最高位,if(!A[7]) //A是正值;if(B[7]) //B是负值。

在乘法运算中,运算结果的符号可以通过异或运算得到。

|

A值 |

B值 |

结果 |

|

正(0) |

正(0) |

正(0) |

|

正(0) |

负(1) |

负(1) |

|

负(1) |

正(0) |

负(1) |

|

负(1) |

负(1) |

正(0) |

3.乘法器程序设计思路

首先考虑输入信号量,有乘数与被乘数,有一个开始指令(Start_Sig),相当于我们在计算器中输入完计算式子之后,再按下一个“=”号,得到最终的结果。

再考虑输出信号量,有计算结果,同时在计算结果出来后,输出一个运算完成信号(Done_Sig)。

乘法运算的Verilog HDL程序实现:以8X5来举例,其中8是被乘数,5是乘数,表示的含义是5个8相加。乘法运算可以拆分成三个步骤来实现:

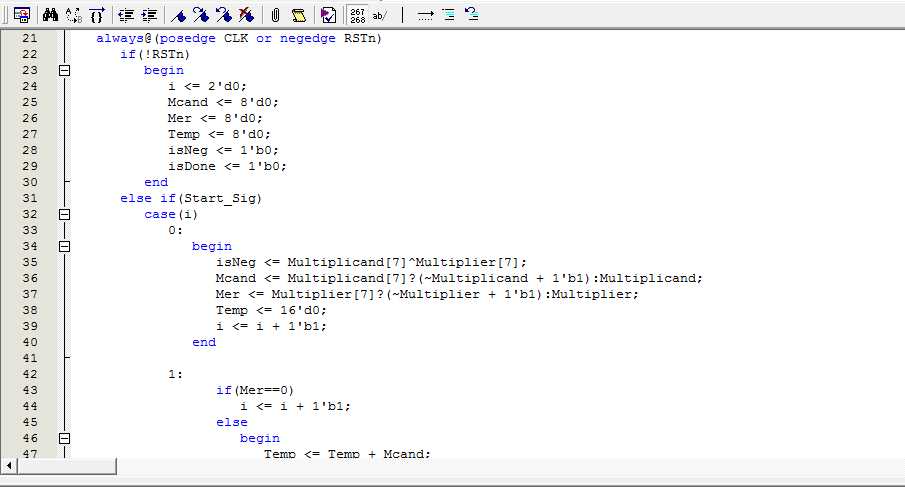

在运算前,取得乘数和被乘数的符号位,然后取被乘数和乘数的正值。

isNeg <= Multiplicand[7]^Multiplier[7];

Mcand <= Multiplicand[7]?(~Multiplicand+1’b1):Multiplicand;

Mer <= Multiplier[7]?(~Multiplier+1’b1):Multiplier;

4.基于ModelSim的乘法器仿真验证

本文将详细描述ModelSim的配置过程,方便以后查阅。

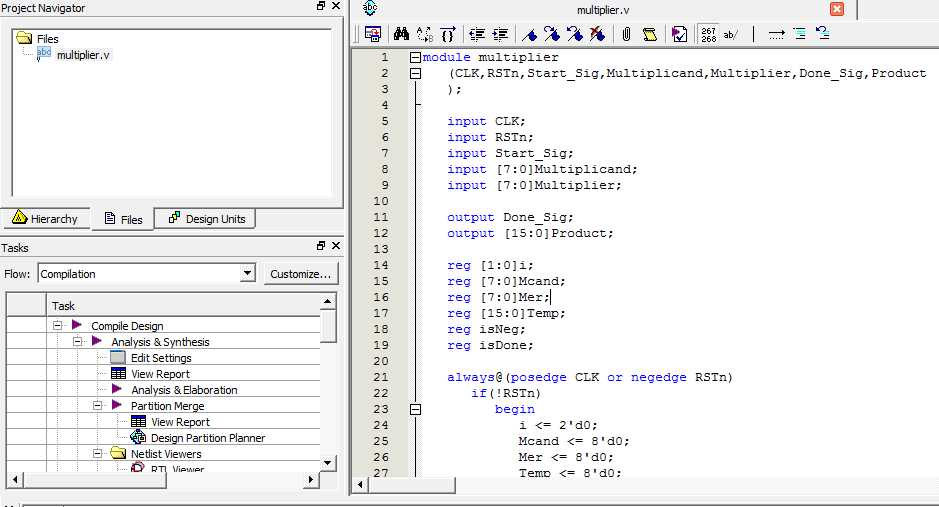

(1)首先建立乘法器的模型,编辑好Verilog HDL程序(学习重点)

(2)关联Quartus与Modelsim-Altera

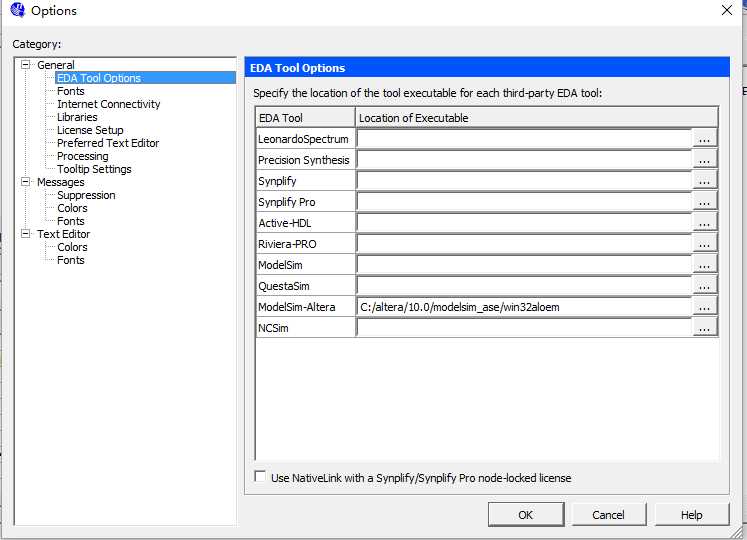

(2)关联Quartus与Modelsim-Altera

Tools ---- Options ---- EDA Tool Options,选择仿真工具,并添加仿真工具的安装路径。本文选用的Modelsim-Altera。

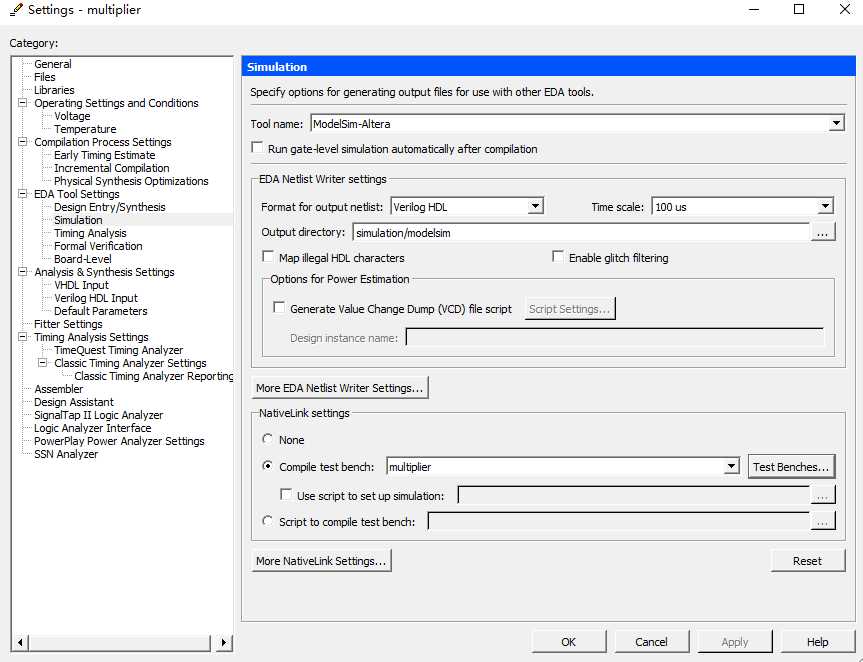

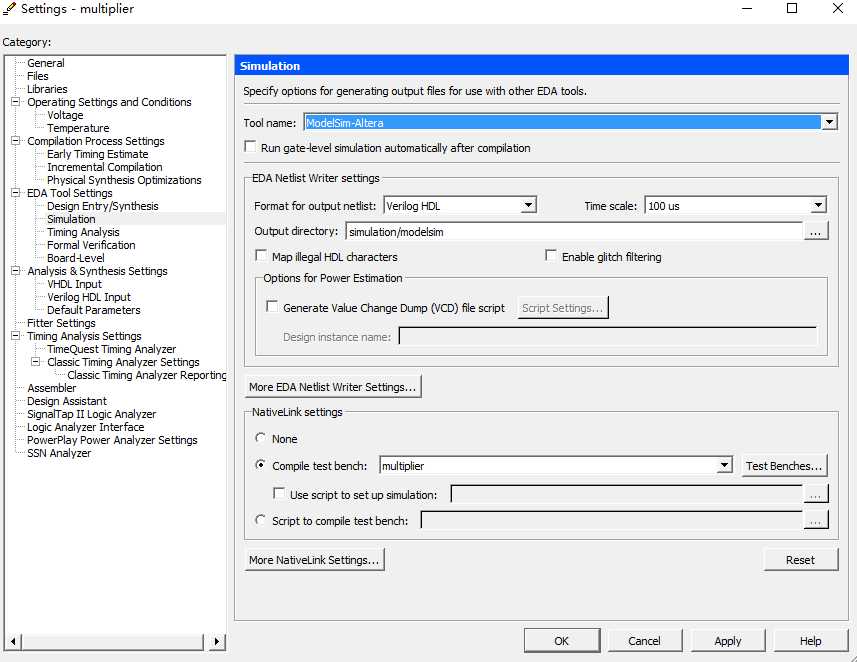

(3)设置仿真工具与需要仿真的文本格式,Time Scale。

Assignments ---- Settings ---- Simulation

Tool name:

Format for output netlist:

Time scale:

Output directory:为默认设置

(4)自动生成Test bench模板

(4)自动生成Test bench模板

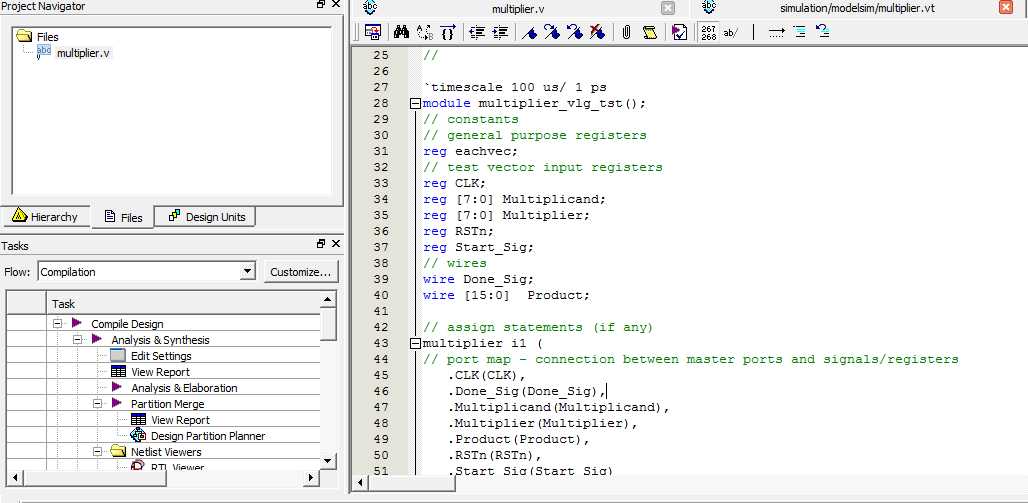

Processing ---- Start ---- Start Test Bench Template writer,操作完成后,自动生成Test bench。

打开Test Bench文件,在整个工程文件中会生成一个simulation文件夹,打开,找到里面的“XXX.vt”文件。

(5)编辑Test bench文件

(5)编辑Test bench文件

按照模板文件中的注释,填充相应的测试程序即可。(里面有大学问)

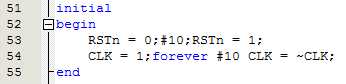

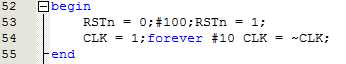

在测试文件中,有一个初始化模块,一般用来初始化时钟信号(CLK)和复位整个电路(RSTn)。

在测试文件中,有一个初始化模块,一般用来初始化时钟信号(CLK)和复位整个电路(RSTn)。

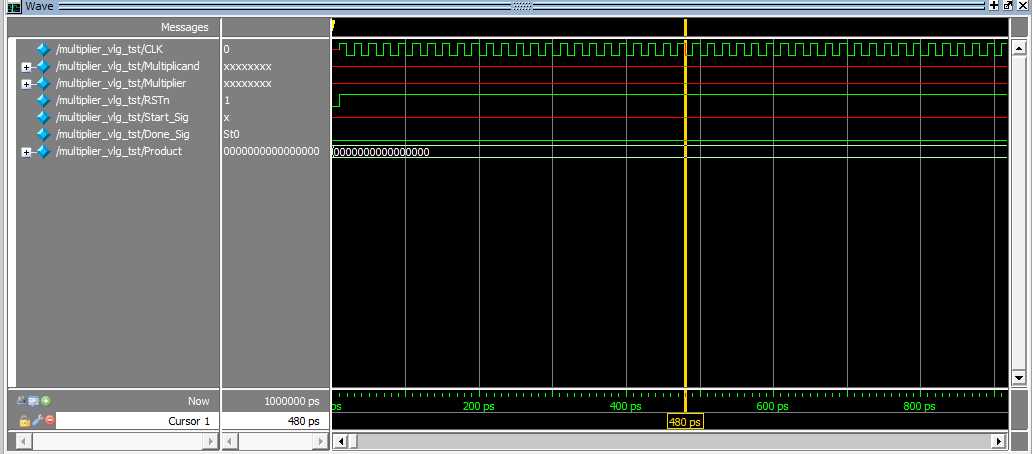

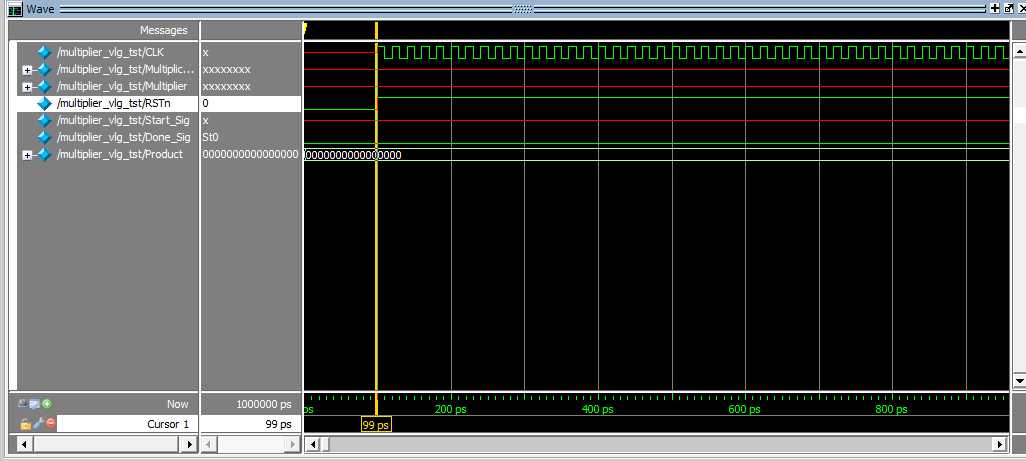

结合“#num”这一参数的变化,与仿真波形的对比,可以得出“#num”是用来设定时间的语句。

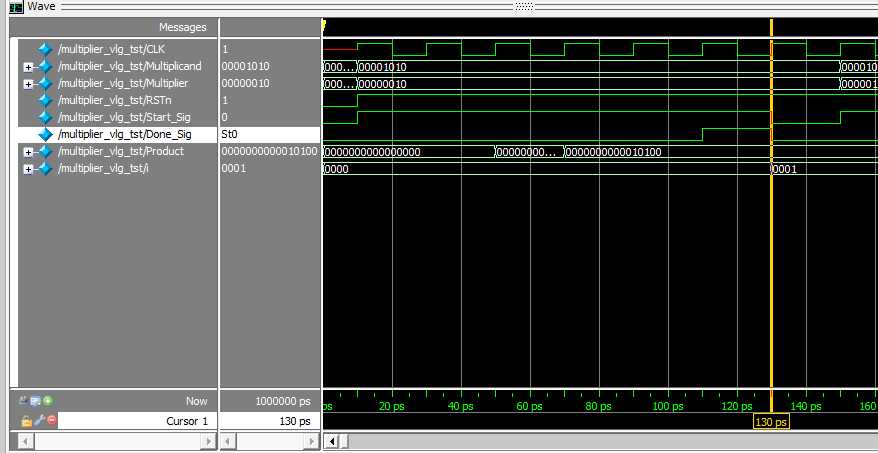

首先谈谈乘法器的工作原理:首先输入乘数与被乘数,当Start_Sig信号置高电平,乘法器开始工作,按照预先写好的模型一步一步运算完后,Done_Sig输出高电平,代表运算完成,得出运算结果输出到Product上。

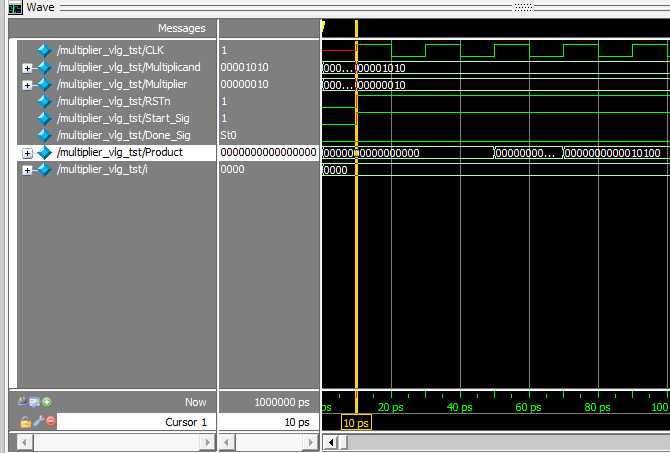

1.Start_Sig由0跳变到1,乘法器开始运算(相当于计算器上的等号按钮),此时乘数与被乘数输入端口已经有数值,Done_Sig处于st0状态,代表还未完成计算。

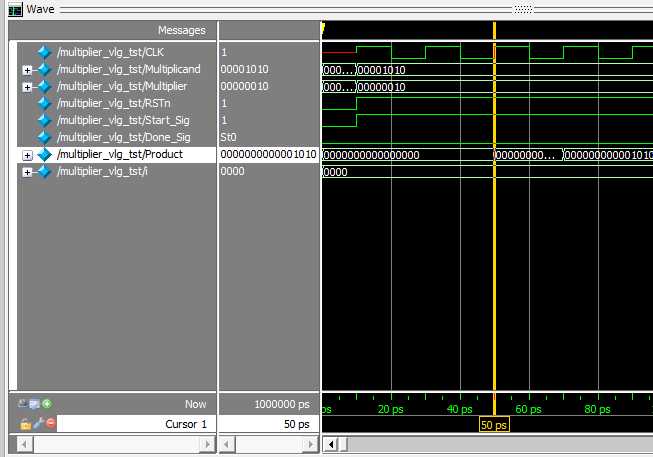

2.计算完了乘法的第一步,输出Product上已经有第一步的运算结果了,但是Done_Sig信号还是保持st0状态,代表计算还未结

2.计算完了乘法的第一步,输出Product上已经有第一步的运算结果了,但是Done_Sig信号还是保持st0状态,代表计算还未结

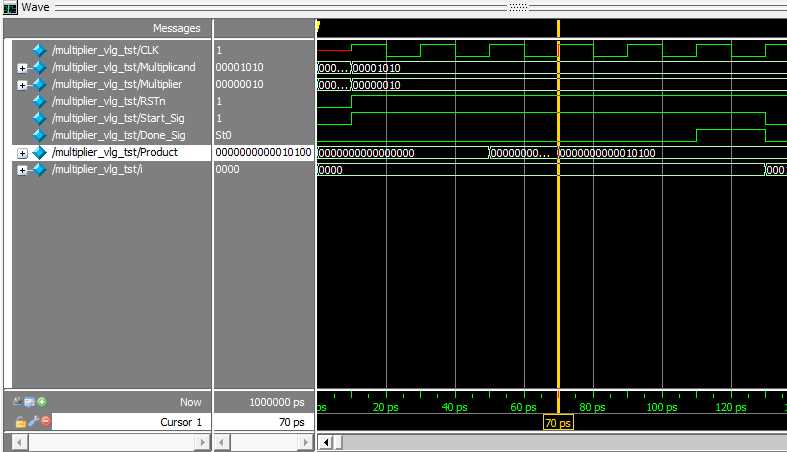

3.第二步运算完成,结果输出到了Product信号线上,但是Done_Sig信号还是保持st0,乘法器还在继续工作。

3.第二步运算完成,结果输出到了Product信号线上,但是Done_Sig信号还是保持st0,乘法器还在继续工作。

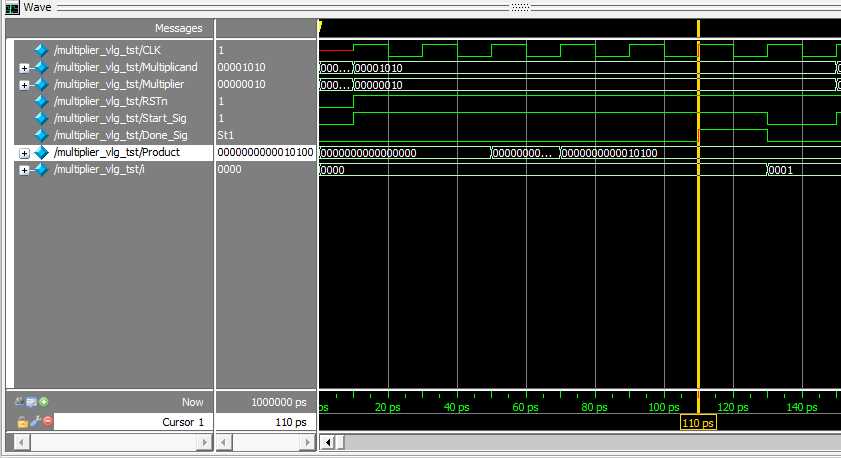

4.Done_Sig信号线由st0跳变为st1,并持续一个脉冲周期,此刻表示乘法器完成计算,Product信号线上的数据即为乘法运算的最终结果。

4.Done_Sig信号线由st0跳变为st1,并持续一个脉冲周期,此刻表示乘法器完成计算,Product信号线上的数据即为乘法运算的最终结果。

5.Done_Sig状态又恢复到st0,此刻Start_Sig信号由1变为0,代表乘法器关闭,停止工作,always块语句里面的乘法算法将不再执行。

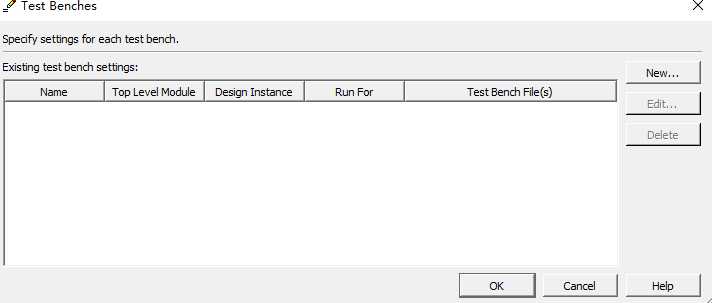

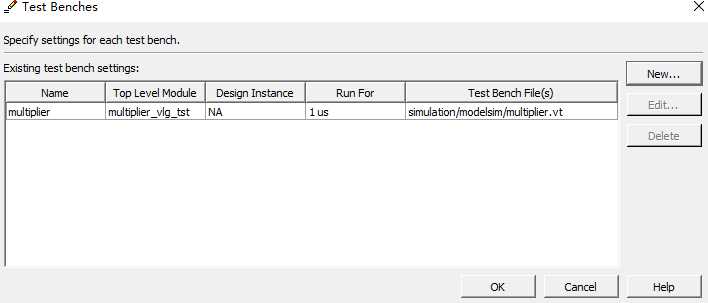

(6)将编辑好的Test bench文件添加到工程中

Assignments ---- Settings ---- Simulation

选择 Compile test bench选项,单击“...”

New ----

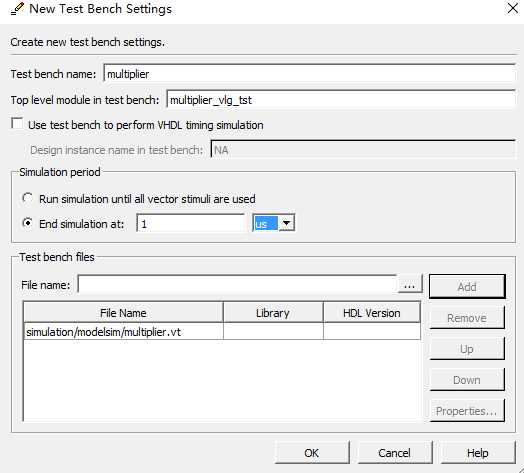

需要填充如下内容:

Test bench name:就是testbench文件的名字,即“.vt”文件的文件名。

Top level module in test bench:就是testbench文件的顶层模块名。

End simulation at:就是仿真最大的时间。

在Test bench files面板中添加Test bench文件,单击“...”找到“.vt”文件的路径,单击add即可,最后单击OK。

单击OK。

单击OK。

单击Apply,单击OK。

单击Apply,单击OK。

(7)开始仿真

Tools ---- Run EDA Simulation Tool ---- EDA RTL Simulation

自动启动ModelSim程序,即可以看到仿真波形。

标签:

原文地址:http://www.cnblogs.com/chensimin1990/p/5750956.html