标签:

第一个FPGA工程----点亮开发板上的3个LED灯

1.新建FPGA工程

开启Quartus2的画面

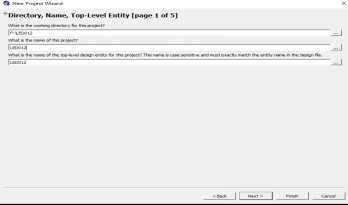

File--New Project Wizard..指定工程的路径与工程名

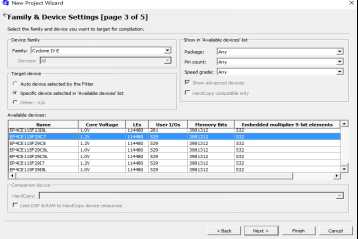

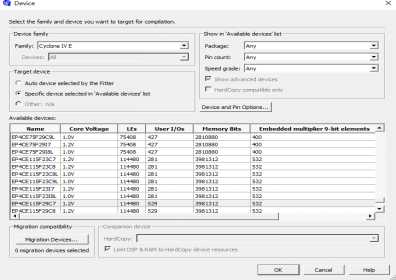

指定所使用的FPGA设备型号

2.添加设计文件

本设计采用Verilog HDL硬件描述语言建模

3.建模

本设计有三个输出量,没有输入量,这三个输出量对应FPGA芯片的三个管脚,同时被置高电平,用来驱动LED灯。

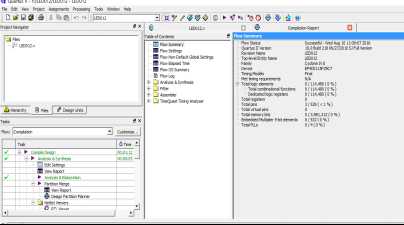

4.编译工程

Processing--Start compilation 并生成编译报告

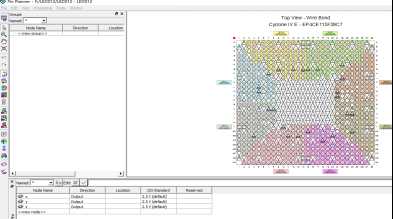

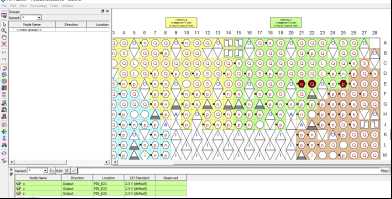

5.引脚分配

引脚分配旨在于将我们用硬件描述语言建立起来的模型与实际的硬件电路对应起来。

在Location中指定Node name对应的管脚。

在指定完管脚后,FPGA的引脚图会做出相应的标记。

完成引脚分配后,需要对工程文件进行综合:Analysis &Synthesis ,单击右键,start,得到综合报告。

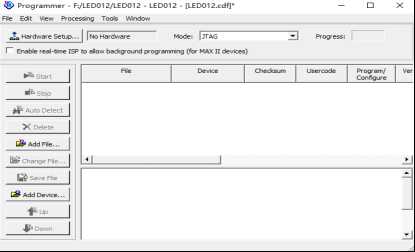

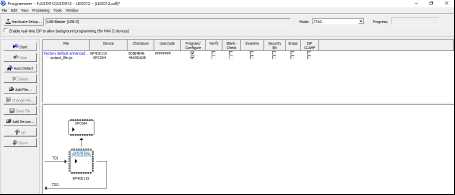

6.将程序烧写到芯片

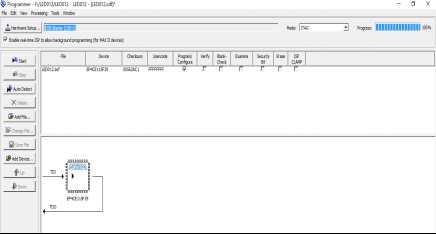

Tools--programmer

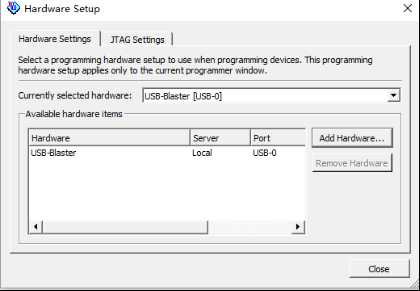

Hardware Setup...添加硬件:USB-Blaster

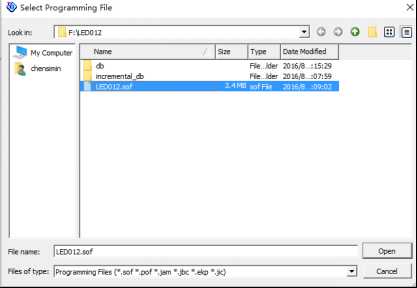

Add File.. 添加烧写文件.sof

单击Start开始烧写程序到FPGA芯片中,同时会有进度条显示,当达到100%时,即表示烧写成功,此时开发板上相应的LED灯会点亮(此种程序烧写方式是将程序下载到了SRAM中,掉电程序会消失,但烧写完成后,电路板无需复位,立马做出响应)。

7.将程序烧写到Flash中,上电自动读取

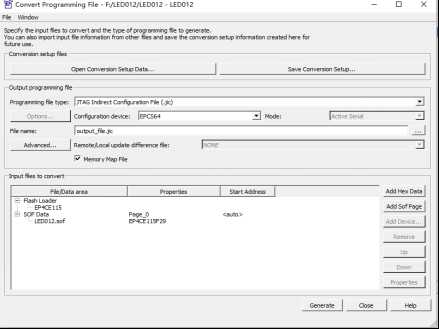

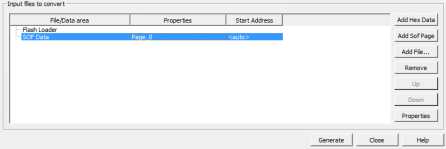

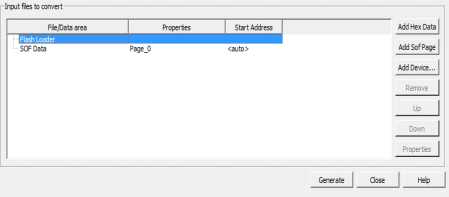

首先需要将.sof烧写文件转化为.jic文件

File--Convert programming Files

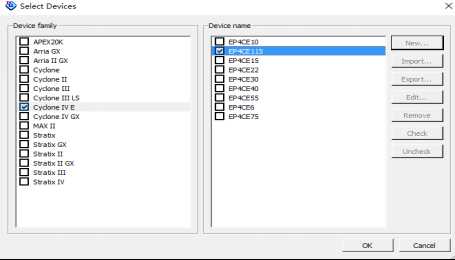

其中,Configuration device:EPCS64,(此选项依据开发板用户手册)

添加转换文件与设备

单击Generate生成.jic文件,最后会给出生成文件成功的提示。

烧写.jic文件到Flash中,同烧写到SRAM中的操作流程一样,只需添加上.jic文件,单击Start按钮就可以了。(此种程序烧写方式是将程序下载到了FPGA外部挂载的FLASH芯片中,掉电程序不会消失,上电,程序会自动加载并开始运行,但烧写完成后,电路板需要重新上电,程序才会做出响应)。

注意:

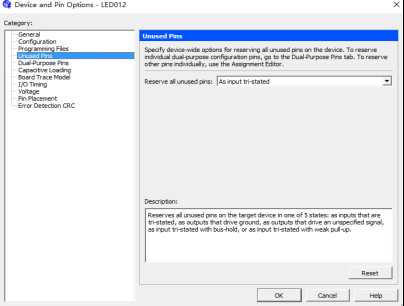

至此,整个FPGA工程已经完成,但是会发现开发板上有其它未被点亮的LED灯发出微弱的光,因此,我们需要设置一下FPGA芯片上未被使用的引脚。

Assignments----Device

单击Device and pin options...

Unused Pins----Reserve all unused pins: As input tri-stated(设置成三态输入)即可消除其它LED灯发出微弱光的现象。

标签:

原文地址:http://www.cnblogs.com/chensimin1990/p/5759274.html