标签:

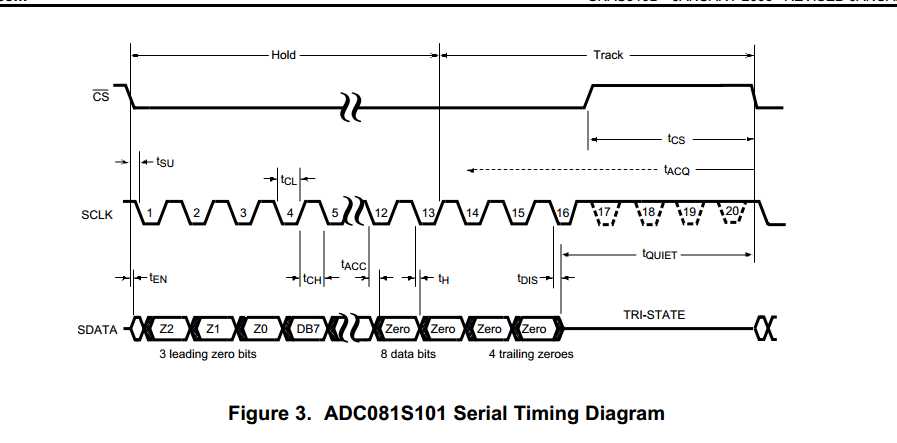

我用的是adc081sd的芯片,cpol:cs被拉为低电平时sclk是高,cpol为1,cs被拉为低电平时sclk为0时,cpol为0;

cpha:cs被拉为低电平后是第一个时钟沿为0,第二个时钟沿采集数据为1.

时钟上升沿对应的采集数据位稳定时就为上升沿采集,时钟下降沿对应的采集数据位稳定时就为下降沿沿采集,

如下图所示sclk的上升沿稳定,下降沿数据不稳定(那么时钟的下降沿送数据,上升沿采集数据即可)。上升沿采集。

module adc

(

input clk_in,//

input rst_n_in,//

input adc_data,//caiji

output reg cs,

output reg sclk,

output reg[7:0] led

);

//产生状态

reg[5:0] cnt=0;

always@(posedge clk_in or negedge rst_n_in)

begin

if(!rst_n_in)

cnt<=0;

else

begin

if(cnt>=35)cnt<=0;

else cnt<=cnt+1;

end

end

reg[15:0] data_reg=16‘b0;

always@(posedge clk_in or negedge rst_n_in)

begin

if(!rst_n_in)begin cs<=1;sclk<=1; end

else

begin

case(cnt)

0:begin sclk<=1; cs<=1; end

1:begin cs<=0; end

2:begin sclk<=0;end

3:begin sclk<=1;data_reg[15]<=adc_data;end //采集了数据最高位z2

4:begin sclk<=0;end

5:begin sclk<=1;data_reg[14]<=adc_data;end //采集了数据位z1

6:begin sclk<=0;end

7:begin sclk<=1;data_reg[13]<=adc_data;end//采集了数据z0

8:begin sclk<=0;end

9:begin sclk<=1;data_reg[12]<=adc_data;end//采集了数据DB7

10:begin sclk<=0;end

11:begin sclk<=1;data_reg[11]<=adc_data;end//采集了数据DB6

12:begin sclk<=0;end

13:begin sclk<=1;data_reg[10]<=adc_data;end//采集了数据DB5

14:begin sclk<=0;end

15:begin sclk<=1;data_reg[9]<=adc_data;end//采集了数据DB4

16:begin sclk<=0;end

17:begin sclk<=1;data_reg[8]<=adc_data; end//采集了数据DB3

18:begin sclk<=0;end ////采集了DB2

19:begin sclk<=1; data_reg[7]<=adc_data; end

20:begin sclk<=0;end //

21:begin sclk<=1;data_reg[6]<=adc_data;end//采集了数据DB1

22:begin sclk<=0;end //

23:begin sclk<=1;data_reg[5]<=adc_data;end//采集了数据DB0

24:begin sclk<=0;end //

25:begin sclk<=1;data_reg[4]<=adc_data;end//采集了数据ZERO 4

26:begin sclk<=0;end //

27:begin sclk<=1;data_reg[3]<=adc_data;end//采集了数据ZERO 3

28:begin sclk<=0;end //

29:begin sclk<=1;data_reg[2]<=adc_data;end//采集了数据ZERO 2

30:begin sclk<=0;end //

31:begin sclk<=1;data_reg[1]<=adc_data;end//采集了数据ZERO 1

32:begin sclk<=0;end //

33:begin sclk<=1;data_reg[0]<=adc_data;end //采集了数据ZERO 0

34:begin cs<=1; led<=data_reg[12:5]; end //将数据锁存,采下次数据时led的数据不会发生跳变

endcase

end

end

endmodule

标签:

原文地址:http://www.cnblogs.com/sgh69/p/5767675.html