标签:

1,什么是组合逻辑电路?

逻辑电路在任何时刻产生的稳定的输出信号仅仅取决于该时刻的输入信号,而与过去的输入信号无关,即与输入信号作用前的状态无关,这样的电路称为组合逻辑电路。

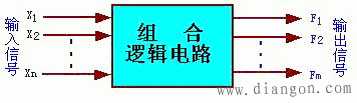

上图给出了一个典型的数字逻辑电路模型,其中的输入信号为X={X1,...,Xn},Y={Y1,...,Yn}为对应的输出信号,输入与输出的关系可以表示为:Y=F(X)。

上图给出了一个典型的数字逻辑电路模型,其中的输入信号为X={X1,...,Xn},Y={Y1,...,Yn}为对应的输出信号,输入与输出的关系可以表示为:Y=F(X)。

2,组合逻辑电路有哪些特点?

组合逻辑电路具有两个特点:

(1).由逻辑门电路组成,不含有任何的记忆元件;

(2).电路是单向传输的,电路中不存在任何反馈回路。

3,如何描述组合逻辑电路?

(1)真值表;

(2)逻辑表达式

(3)逻辑门电路图

(4)卡诺图

(具体描述略)

4,各种描述之间相互转换关系?

(1)真值表——逻辑表示

(2)逻辑表达式——逻辑电路图

(3)逻辑电路图——真值表

(具体描述略)

5,如何使用verilog描述组合逻辑电路,及注意事项?

(1)使用assign描述组合逻辑电路;

在verilog HDL,用assign描述的部分都是组合逻辑电路,下面对assign做简要的介绍:

assign:连续赋值语句是Verilog数据流建模的基本语句,用于对线网进行赋值,等价于门级描述,然而是从更高的抽象层次对电路进行描述。assign语法表示如下:

continuous_assign ::=assign [drive_stength] [delay] list_of_net_assignments;

list_of_net_assignment :: =net_assignment {, net_assignment}

net_assignment :: +net_lvalue =expression

drive_strength默认为strong1,strong0。

注意连续赋值语句只能对线网进行赋值,即等式左边一定是线网数据类型,右边可以是任意的数据类型。

(2)使用always描述组合逻辑电路;

always不仅可以用来描述时序逻辑电路,也可以用来描述组合逻辑电路,主要区别在于敏感列表和赋值方式。这里只介绍always在组合逻辑电路中的应用。

1)在敏感列表中使用电平敏感事件,而不用边沿敏感列表;

2),为变量赋值使用阻塞赋值,而不用非阻塞赋值;

3),在always块内被赋值的变量必须为寄存器型变量。

(3)使用门级原语描述组合逻辑。(具体描述略,可参考verilog相关书籍)

标签:

原文地址:http://www.cnblogs.com/rrttp/p/5929387.html