标签:配置 访问 经验 系统设计 dwr ssh speed structure 发送

1.FSMC机制

FSMC(Flexihie Static Memory Controller,可变静态存储控制器)是STM32系列中内部集成256 KB以上FlaSh,后缀为xC、xD和xE的高存储密度微控制器特有的存储控制机制。之所以称为“可变”,是由于通过对特殊功能寄存器的设置,FSMC能够根据不同的外部存储器类型,发出相应的数据/地址/控制信号类型以匹配信号的速度,从而使得STM32系列微控制器不仅能够应用各种不同类型、不同速度的外部静态存储器,而且能够在不增加外部器件的情况下同时扩展多种不同类型的静态存储器,满足系统设计对存储容量、产品体积以及成本的综合要求

1.1 FSMC技术优势

①支持多种静态存储器类型。STM32通过FSMC町以与SRAM、ROM、PSRAM、NOR Flash和NANDFlash存储器的引脚直接相连。

②支持丰富的存储操作方法。FSMC不仅支持多种数据宽度的异步读/写操作,而且支持对NOR/PSRAM/NAND存储器的同步突发访问方式。

③支持同时扩展多种存储器。FSMC的映射地址空间中,不同的BANK是独立的,可用于扩展不同类型的存储器。当系统中扩展和使用多个外部存储器时,FSMC会通过总线悬空延迟时间参数的设置,防止各存储器对总线的访问冲突。

④支持更为广泛的存储器型号。通过对FSMC的时间参数设置,扩大了系统中可用存储器的速度范围,为用户提供了灵活的存储芯片选择空间。

⑤支持代码从FSMC扩展的外部存储器中直接运行,而不需要首先调入内部SRAM。

1.2 FSMC内部结构

STM32微控制器之所以能够支持NOR Flash和NAND Flash这两类访问方式完全不同的存储器扩展,是因为FSMC内部实际包括NOR Flash和NAND/PC Card两个控制器,分别支持两种截然不同的存储器访问方式。在STM32内部,FSMC的一端通过内部高速总线AHB连接到内核Cortex-M3,另一端则是面向扩展存储器的外部总线。内核对外部存储器的访问信号发送到AHB总线后,经过FSMC转换为符合外部存储器通信规约的信号,送到外部存储器的相应引脚,实现内核与外部存储器之间的数据交互。FSMC起到桥梁作用,既能够进行信号类型的转换,又能够进行信号宽度和时序的调整,屏蔽掉不同存储类型的差异,使之对内核而言没有区别。

1.3 FSMC映射地址空间

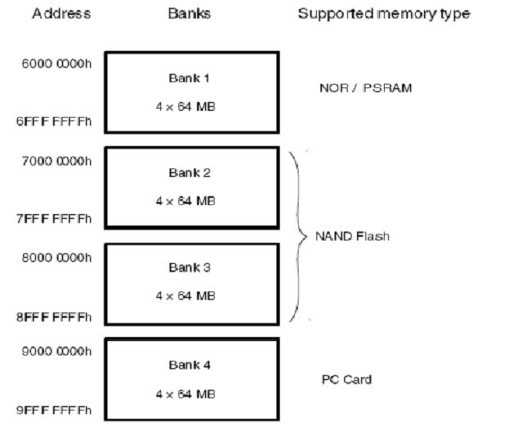

FSMC管理1 GB的映射地址空间。该空间划分为4个大小为256 MB的BANK,每个BANK又划分为4个64 MB的子BANK,如表1所列。FSMC的2个控制器管理的映射地址空间不同。NOR Flash控制器管理第1个BANK,NAND/PC Card控制器管理第2~4个BANK。由于两个控制器管理的存储器类型不同,扩展时应根据选用的存储设备类型确定其映射位置。其中,BANK1的4个子BANK拥有独立的片选线和控制寄存器,可分别扩展一个独立的存储设备,而BANK2~BANK4只有一组控制寄存器。

2 FSMC扩展NOR Flash配置

SRAM/ROM、NOR Flash和PSRAM类型的外部存储器都是由FSMC的NOR Flash控制器管理的,扩展方法基本相同,其中NOR Flash最为复杂。通过FSMC扩展外部存储器时,除了传统存储器扩展所需要的硬件电路外,还需要进行FSMC初始化配置。FSMC提供大量、细致的可编程参数,以便能够灵活地进行各种不同类型、不同速度的存储器扩展。外部存储器能否正常工作的关键在于:用户能否根据选用的存储器型号,对配置寄存器进行合理的初始化配置。

(1)确定映射地址空间

根据选用的存储器类型确定扩展使用的映射地址空间。NOR Flash只能选用BANK1中的4个子BANK。选定映射子BANK后,即可确定以下2方面内容:

①硬件电路中用于选中该存储器的片选线FSMC_NEi(i为子BANK号,i=1,…,4);

②FSMC配置中用于配置该外部存储器的特殊功能寄存器号(如表1所列)。

(2)配置存储器基本特征

通过对FSMC特殊功能寄存器FSMC_BCRi(i为子BANK号,i=1,…,4)中对应控制位的设置,FSMC根据不同存储器特征可灵活地进行工作方式和信号的调整。根据选用的存储器芯片确定需要配置的存储器特征,主要包括以下方面:

①存储器类型(MTYPE)是SRAM/ROM、PSRAM,还是NOR FlaSh;

②存储芯片的地址和数据引脚是否复用(MUXEN),FSMC可以直接与AD0~AD15复用的存储器相连,不需要增加外部器件;

③存储芯片的数据线宽度(MWID),FSMC支持8位/16位两种外部数据总线宽度;

④对于NOR Flash(PSRAM),是否采用同步突发访问方式(B URSTEN);

⑤对于NOR Flash(PSRAM),NWAIT信号的特性说明(WAITEN、WAITCFG、WAITPOL);

⑥对于该存储芯片的读/写操作,是否采用相同的时序参数来确定时序关系(EXTMOD)。

(3)配置存储器时序参数

FSMC通过使用可编程的存储器时序参数寄存器,拓宽了可选用的外部存储器的速度范围。FSMC的NORFlash控制器支持同步和异步突发两种访问方式。选用同步突发访问方式时,FSMC将HCLK(系统时钟)分频后,发送给外部存储器作为同步时钟信号FSMC_CLK。此时需要的设置的时间参数有2个:

①HCLK与FSMC_CLK的分频系数(CLKDIV),可以为2~16分频;

②同步突发访问中获得第1个数据所需要的等待延迟(DATLAT)。

对于异步突发访问方式,FSMC主要设置3个时间参数:地址建立时间(ADDSET)、数据建立时间(DATAST)和地址保持时间(ADDHLD)。FSMC综合了SRAM/ROM、PSRAM和NOR Flash产品的信号特点,定义了4种不同的异步时序模型。选用不同的时序模型时,需要设置不同的时序参数,如表2所列。在实际扩展时,根据选用存储器的特征确定时序模型,从而确定各时间参数与存储器读/写周期参数指标之间的计算关系;利用该计算关系和存储芯片数据手册中给定的参数指标,可计算出FSMC所需要的各时间参数,从而对时间参数寄存器进行合理的配置。

FSMC全称“静态存储器控制器”。

使用FSMC控制器后,可以把FSMC提供的FSMC_A[25:0]作为地址线,而把FSMC提供的FSMC_D[15:0]作为数据总线。

(1)当存储数据设为8位时,(FSMC_NANDInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_8b)

地址各位对应FSMC_A[25:0],数据位对应FSMC_D[7:0]

(2)当存储数据设为16位时,(FSMC_NANDInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b)

地址各位对应FSMC_A[24:0],数据位对应FSMC_D[15:0]

FSMC 包括4个模块:

(1)AHB接口(包括FSMC配置寄存器)

(2)NOR闪存和PSRAM控制器(驱动LCD的时候LCD就好像一个PSRAM的里面只有2个16位的存储空间,一个是DATA RAM 一个是CMD RAM)

(3)NAND闪存和PC卡控制器

(4)外部设备接口

注:FSMC可以请求AHB进行数据宽度的操作。如果AHB操作的数据宽度大于外部设(NOR或NAND或LCD)的宽度,此时FSMC将AHB操作分割成几个连续的较小的数据宽度,以适应外部设备的数据宽度。

FSMC对外部设备的地址映像从0x6000 0000开始,到0x9FFF FFFF结束,共分4个地址块,每个地址块256M字节。可以看出,每个地址块又分为4个分地址块,大小64M。对NOR的地址映像来说,我们可以通过选择HADDR[27:26]来确定当前使用的是哪个64M的分地址块,如下页表格。而这四个分存储块的片选,则使用NE[4:1]来选择。数据线/地址线/控制线是共享的。

NE1 ->Bank1 NE2->Bank2 NE3->Bank3 NE4->Bank4

若 NE1 连接, 则

每小块NOR/PSRAM 64M

第一块:6000 0000h--63ff ffffh (DATA长度为8位情况下,由地址线FSMC_A[25:0]决定;DATA长度为16位情况下,由地址线FSMC_A[24:0]决定)

第二块:6400 0000h--67ff ffffh

第二块:6800 0000h--6bff ffffh

第三块:6c00 0000h--6fff ffffh

注:这里的HADDR是需要转换到外部设备的内部AHB地址线,每个地址对应一个字节单元。因此,若外部设备的地址宽度是8位的,则HADDR[25:0]与STM32的CPU引脚FSMC_A[25:0]一一对应,最大可以访问64M字节的空间。若外部设备的地址宽度是16位的,则是HADDR[25:1]与STM32的CPU引脚FSMC_A[24:0]一一对应。在应用的时候,可以将FSMC_A总线连接到存储器或其他外设的地址总线引脚上。

例:STM32F10XX FCMS控制LCD的驱动

FSMC提供了所有的LCD控制器的信号:

FSMC_D[16:0] ?? 16bit的数据总线

FSMC NEx:分配给NOR的256M,再分为4个区,每个区用来分配一个外设,这四个外设的片选分为是NE1-NE4,对应的引脚为:PD7—NE1,PG9—NE2,PG10-NE3,PG12—NE4

FSMC NOE:输出使能,连接LCD的RD脚。

FSMC NWE:写使能,连接LCD的RW脚。

FSMC Ax:用在LCD显示RAM和寄存器之间进行选择的地址线,即该线用于选择LCD的RS脚,该线可用地址线的任意一根线,范围:FSMC_A[25:0]。

注:RS = 0时,表示读写寄存器;RS = 1表示读写数据RAM。

举例1:选择NOR的第一个存储区,并且使用FSMC_A16来控制LCD的RS引脚,则我们访问LCD显示RAM的基址为0x6002 0000,访问LCD寄存器的地址为:0x6000 0000。因为数据长度为16bit ,所以FSMC_A[24:0]对应HADDR[25:1] 所以显示RAM的基址=0x60000000+2^16*2=0x60000000+0x2 0000=0x60020000

举例2:选择NOR的第四个存储区,使用FSMC_A0控制LCD的RS脚,则访问LCD显示RAM的基址为0x6c00 0002,访问LCD寄存器的地址为:0x6c00 0000。

例:

FSMC_D[15:0],连16bit数据线;FSMC_NE1,连片选:只有bank1可用

FSMC NOE:输出使能

FSMC NEW:FSMC写使能

FSMC Ax:连接RS,可用范围FSMC_A[24:0]

一般使用模式B来做LCD的接口控制,不适用外扩模式。并且读写操作的时序一样。此种情况下,我们需要使用三个参数:ADDSET,DATAST,ADDHOLD。这三个参数在位域FSMC_TCRx中设置。

当HCLK的频率是72MHZ,使用模式B,则有如下时序:

地址建立时间:0x1

地址保持时间:0x0

数据建立时间:0x2

注:这里地址建立 地址保持 数据建立三个时间不知道怎么设出来的。。。。。我是根据别人的经验来设定的。高手知道这个设置不同有什么区别的话,请指教,谢谢:)

static void LCD_CtrlLinesConfig(void)

{

GPIO_InitTypeDef GPIO_InitStructure;

RCC_AHBPeriphClockCmd(RCC_AHBPeriph_FSMC, ENABLE);

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB | RCC_APB2Periph_GPIOD |RCC_APB2Periph_GPIOE |

RCC_APB2Periph_GPIOF | RCC_APB2Periph_GPIOG |

RCC_APB2Periph_AFIO, ENABLE);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0 | GPIO_Pin_1 | GPIO_Pin_4 | GPIO_Pin_5 |

GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10 | GPIO_Pin_14 |

GPIO_Pin_15; // | GPIO_Pin_7;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_Init(GPIOD, &GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7 | GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10 |

GPIO_Pin_11 | GPIO_Pin_12 | GPIO_Pin_13 | GPIO_Pin_14 |

GPIO_Pin_15 | GPIO_Pin_3 | GPIO_Pin_4 | GPIO_Pin_5 | GPIO_Pin_6;

GPIO_Init(GPIOE, &GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0;

GPIO_Init(GPIOF, &GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_12;

GPIO_Init(GPIOG, &GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_1;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(GPIOB, &GPIO_InitStructure);

GPIO_SetBits(GPIOB, GPIO_Pin_1);

}

static void LCD_FSMCConfig(void)

{

FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure;

FSMC_NORSRAMTimingInitTypeDef FSMC_NORSRAMTimingInitStructure;

FSMC_NORSRAMTimingInitStructure.FSMC_AddressSetupTime = 1;

FSMC_NORSRAMTimingInitStructure.FSMC_AddressHoldTime = 0;

FSMC_NORSRAMTimingInitStructure.FSMC_DataSetupTime = 2;

FSMC_NORSRAMTimingInitStructure.FSMC_BusTurnAroundDuration = 0;

FSMC_NORSRAMTimingInitStructure.FSMC_CLKDivision = 0;

FSMC_NORSRAMTimingInitStructure.FSMC_DataLatency = 0;

FSMC_NORSRAMTimingInitStructure.FSMC_AccessMode = FSMC_AccessMode_B;

FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM4;

FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable;

FSMC_NORSRAMInitStructure.FSMC_MemoryType = FSMC_MemoryType_SRAM;

FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b;

FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode = FSMC_BurstAccessMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;

FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive =FSMC_WaitSignalActive_BeforeWaitState;

FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable;

FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable;

FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct =&FSMC_NORSRAMTimingInitStructure;

FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &FSMC_NORSRAMTimingInitStructure;

FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure);

FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM4, ENABLE);

}

小结:这里使用的地址映射属于BANK1 NOR/PSRAM1 所以DATA数据基址为0x6c000000 又因为LCD的RS连接在FSMC_A0上 所以CMD地址为0x6c000002。配置好FSMC后,要写DATA或CMD时只要对这两个地址操作就可以了。

标签:配置 访问 经验 系统设计 dwr ssh speed structure 发送

原文地址:http://www.cnblogs.com/huangbaobaoi/p/6056866.html