标签:技术 lin 结束 size 逻辑 height code blog 代码

同步复位的优点:

同步复位的缺点:

异步复位优点:

异步复位缺点:

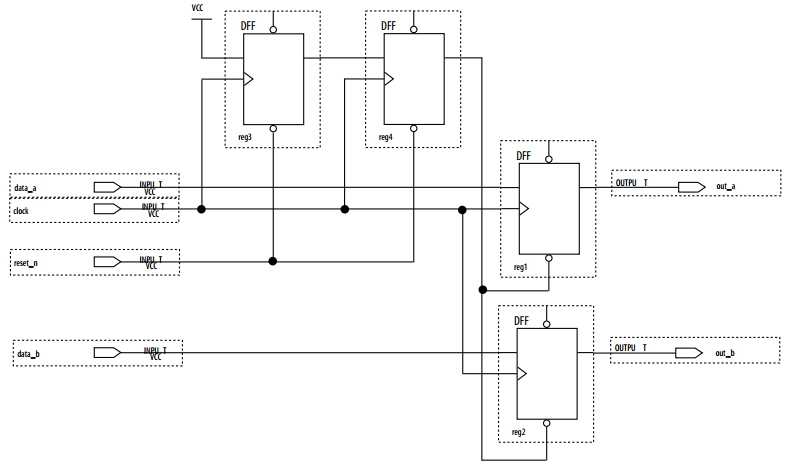

使用异步复位同步释放就可以消除上述缺点。所谓异步复位,同步释放就是在复位信号到来的时候不受时钟信号的同步,而是在复位信号释放的时候受到时钟信号的同步。异步复位同步释放的原理图和代码如下:

//Synchronized Asynchronous Reset module sync_async_reset ( input clock, input reset_n, input data_a, input data_b, output out_a, output out_b); reg reg1, reg2; reg reg3, reg4; assign out_a = reg1; assign out_b = reg2; assign rst_n = reg4; always @ (posedge clock, negedge reset_n) begin if (!reset_n) begin reg3 <= 1‘b0; reg4 <= 1‘b0; end else begin reg3 <= 1‘b1; reg4 <= reg3; end end always @ (posedge clock, negedge rst_n) begin if (!rst_n) begin reg1 <= 1‘b0; reg2 <= 1‘b0; end else begin reg1 <= data_a; reg2 <= data_b; end end endmodule // sync_async_reset

标签:技术 lin 结束 size 逻辑 height code blog 代码

原文地址:http://www.cnblogs.com/zhouzheng/p/6188809.html