标签:source advance bin ann -name drive 自动 1.5 network

Asynchronous Clocks :两个时钟不知道他们之间的相位关系

In most cases, primary clocks can be treated as asynchronous. When associated with their respective generated clocks, they form asynchronous clock groups.

Synchronous Clocks :

This is usually the case when their tree originates from the same root in the netlist, and when they have a common period.

Unexpandable Clocks:

Two clocks are not expandable when the timing engine cannot determine their common period over 1000 cycles.

This is typically the case between two clocks with an odd fractional period ratio. For example, consider two clocks, clk0 and clk1, generated by two MMCMs that share the same primary clock:

? clk0 has a 5.125ns period.

? clk1 has a 6.666ns period.

Asynchronous Clock Groups:

由于无法准确的获得时钟间的信息,通常忽略时钟之间路径延迟。用set_clock_groups组合。

set_clock_groups:If you need to constrain and report some paths between asynchronous clocks, you must use the timing exceptions only, and not set_clock_groups.

Use the -asynchronous option to create asynchronous groups.

set_clock_groups -name async_clk0_clk1 -asynchronous -group {clk0 usrclk itfclk} \

-group {clk1 gtclkrx gtclktx}

If the name of the generated clocks cannot be predicted in advance, use get_clocks

-include_generated_clocks to dynamically retrieve them. (如果不知道generated clock的名字,用-include_generated_clocks来索引??)

set_clock_groups -name async_clk0_clk1 -asynchronous -group [get_clocks -include_generated_clocks clk0] -group [get_clocks -include_generated_clocks clk1]

Clock Latency, Jitter, and Uncertainty:

Clock Latency :This delay is typically represented by:

? The source latency (delay before the clock source point, usually, outside the device)

? The network latency (Automatically estimated (pre-route design), or Accurately computed (post-route design))

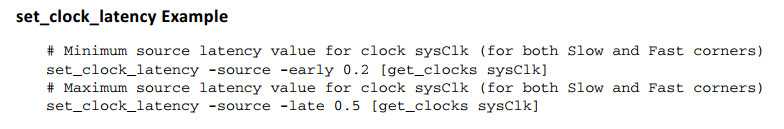

set_clock_latency :specify the clock latency outside the device

Clock Uncertainty

Clock Jitter :ASIC的clock jitter主要由于时钟的不确定因素决定,不能被预测,但是FPGA的时钟jitter能被预测。

input clock jitter: set_input_jitter 来设置primary clock的jitter,但是不能设置generated clock的jitter,vivado能够自动计算。

? For the case in which the generated clock is driven by a MMCM or a PLL, the input jitter

is replaced with a computed discrete jitter.

? For the case the generated clock is created by a combinatorial or sequential cell, the

generated clock jitter is the same as its master clock jitter.

systerm jitter:由Power supply noise,Board noise,Any extra jitter of the system Use the set_system_jitter command to set only one value for the whole design, that is, all the clocks.

Additional Clock Uncertainty :set_clock_uncertainty command to define

标签:source advance bin ann -name drive 自动 1.5 network

原文地址:http://www.cnblogs.com/crossover-r/p/6196133.html