标签:相对 重复 空间 加载 点击 tput 产生 结合 计算

FFT IP核有4种模式,分别为:

前3中模式运算速度依次增大,占用资源也依次增加,第4种模式(Variable Streaming)可以用于在线改变FFT的大小。速度和流模式差不多,资源占用更多。

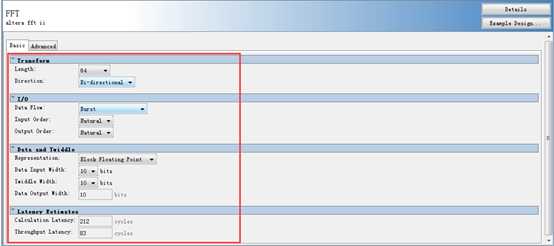

分为基本配置和高级配置两种,基本配置包括配置FFT ip核的变换长度,FFT还是IFFT,数据模式,输入、输出的顺序。数据精度等。高级配置包括FFT的结构,FFT的引擎数。

Length:是FFT的变换长度,只能选择指定长度,不能自定义。

Direction:指定该IP核完成的是FFT变换还是用户可控制的FFT变换或IFFT变换。

Data Flow:选择输入数据流的方式,共有4中方式,突发(Burst)、缓存突发(BufferedBurst)、流模式(Streaming)、可变长度流模式(Variable Streaming),其中前3种方式运算速度依次增加,消耗的资源也依次增加,第4种方式允许用户改变FFT的变换长度,速度和流模式(Streaming)差不多,但消耗更多资源。

Input Otder:输入数据的顺序

Output Order:输出数据的顺序

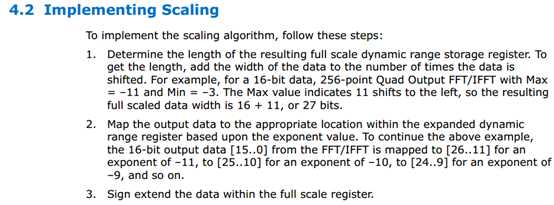

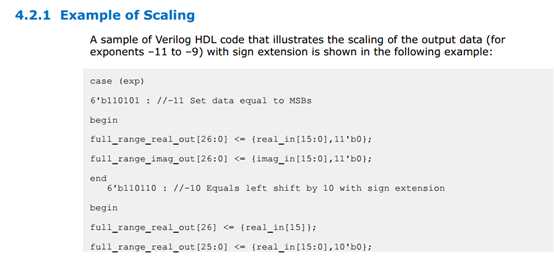

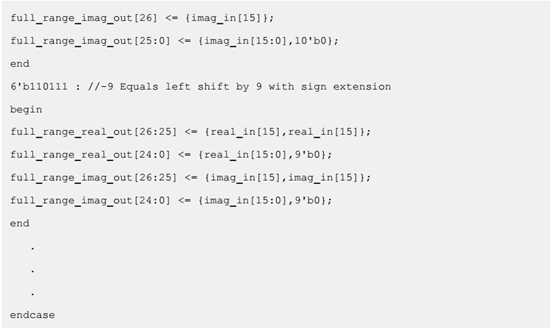

Representation:数据数据的结构,有三种分别是:

Fixed Point和Single Floating Point这两种方式只能用于可变流模式(Variable Streaming),对于突发(Burst)、缓存突发(Buffered Burst)、流模式(Streaming)这三种方式来说只能用(块浮点)Block Floating。块浮点就是在数据的一帧数据中有一个共同的缩放因子,这同时也带来了一个问题,当一帧数据中有大有小的时候,共用一个缩放因子会造成小数(比较小的数)误差增大。

Data Input Width:输入数据的数据宽度

Twiddle Width:旋转因子的数据宽度,旋转因子的数据宽度不能大于输入数据的数据宽度

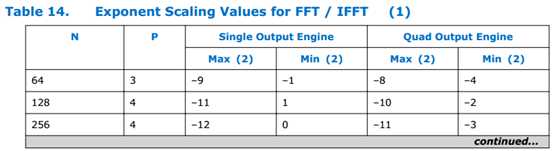

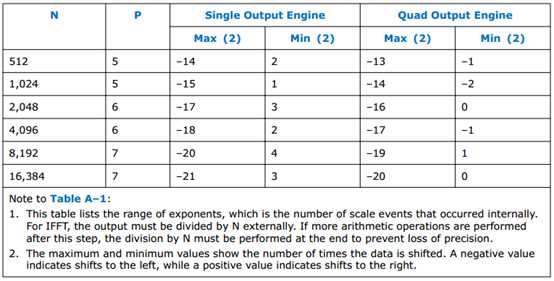

Data Output Width::输出数据的数据宽度,FFT的计算结果是输出的实部和虚部与缩放因子(EXP)的结合,缩放因子为负表示,输出数据需要左移(增大),为正则右移,输出的实部和虚部,缩放因子都是有符号数,这点需要注意。

Latency Estimaters:

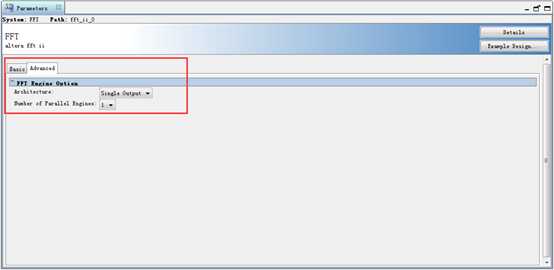

高级设置一共有两个选择,一个是选择运算的结构,一个是选择FFT的引擎数。

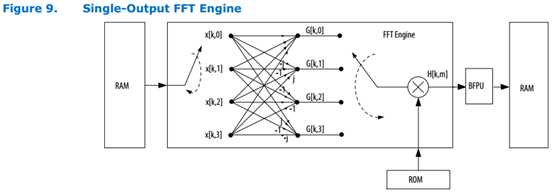

运算结构有两种:Single Output(单输出)和Qaud Output(四输出),单输出一个时钟周期只计算一个FFT的蝶形运算,四输出一个周期计算4个基4的蝶形运算。

FFT的引擎数越多,计算速度越快,当然也消耗更多的资源。默认是四输出,一个FFT引擎,默认设置即可。

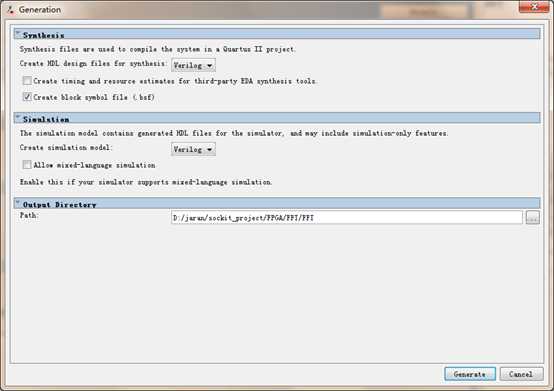

设置完参数后即可点击Generate HDL来产生HDL文件(综合文件和仿真文件)。

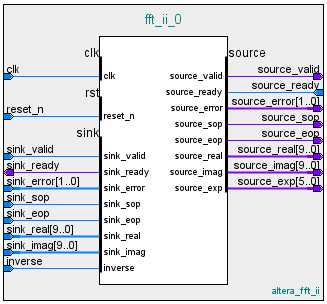

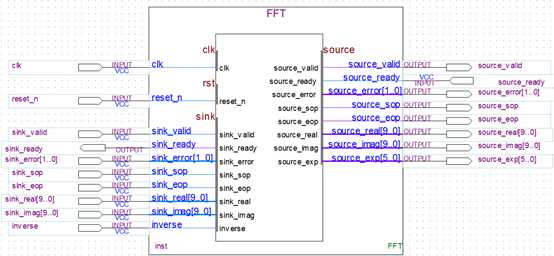

一个时钟,时钟就是FFT ip核运算的时钟;

一个复位,reset_n是FFT ip核复位信号,低电平有效,复位的时候sink_ready信号一直为低(无效);

一个FFT/IFFT控制线,inverser设置FFT变换还是IFFT变换,低电平表示FFT,高电平表示IFFT。一个sink,一个source 。

sink信号:

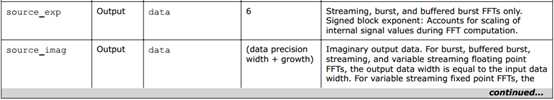

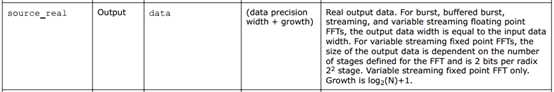

Source信号:

注:

流I/O数据流结构允许输入数据连续处理,并输出连续的复数数据流。这个过程不需要停止FFT函数数据流的进出。

注意:在每一帧数据传输时要注意sink_valide、sink_ready,inverse要同sink_sop同步。

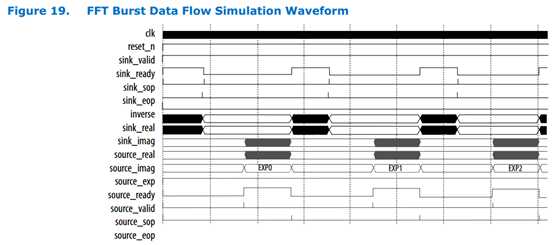

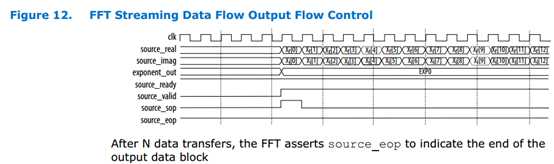

当完成数据转换后,FFT模块将source_valid置为有效,并以自然顺序输出变换域的数据,FFT模块输出source_sop表示第一个有效数据的输出。在N个数据(一帧)都变换结束之后即 N个时钟后,FFT模块将source_eop置为有效表示输出数据的结束。输出时序图如下。

FFT兆核函数采用Altera Atlantic接口I/0协议,输入接口为主设备汇端(Master Sink)而输出接口为主设备源端(Master Source)。

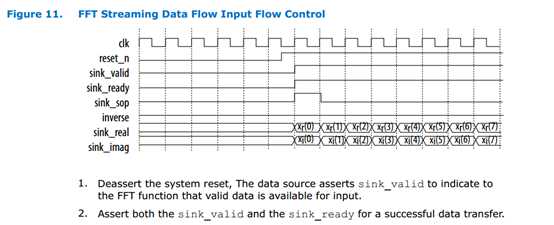

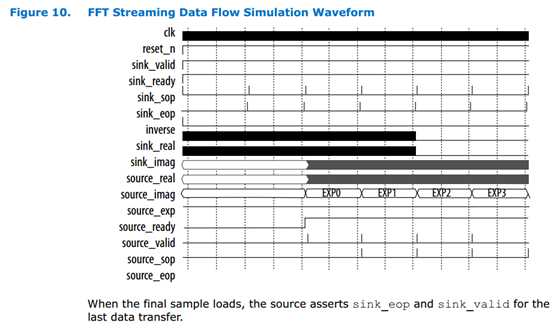

在reset信号无效后,数据源将sink_valide置为高有效,向FFT通知在输入端至少有N个复数据样点可以输入。FFT函数将sink_ready信号置高电平,表明有能力接收这些输入信号。当sink_ready(FFT核发出的)和sink_valide同时有效时,传输开始。数据源加载第一个复数据样点到FFT函数中,同时将sink_sop(start)信号置高电平,表示输入模块的开始,在下一个时钟周期,sink_sop信号被复位,并以自然顺序加载数据样点;当最后一个数据输入后,sink_eop 被置为有效 ,sink_valid仍处于有效,并完成这一帧数据的传输。然后在下一个时钟将sink_sop置为有效,并重复上一过程。

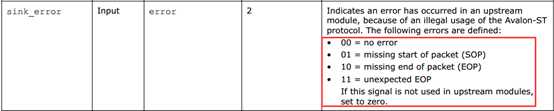

sink_sop必须与sink_valid同时有效并且是一个周期,否则相对于sink_valid滞后的话source _error 出现01错误,查手册发现是valid goes high, but there is no start of frame。sink_sop滞后多少周期01就出现多少周期。

Quartus II 与ModelSim-Altera联合仿真FFT IP核之FFT IP核分析

标签:相对 重复 空间 加载 点击 tput 产生 结合 计算

原文地址:http://www.cnblogs.com/logic3/p/6284911.html