标签:stat play 控制 path 模式 mmc 读取 repair data

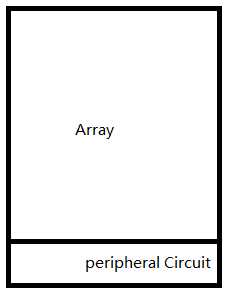

Nand Falsh外围电路:peripheral circuit

1.Nand flash里至少有2个state Machine(controller),即2个主控。

一个主控:负责处理前端事情。

一个主控:负责后端任务处理。

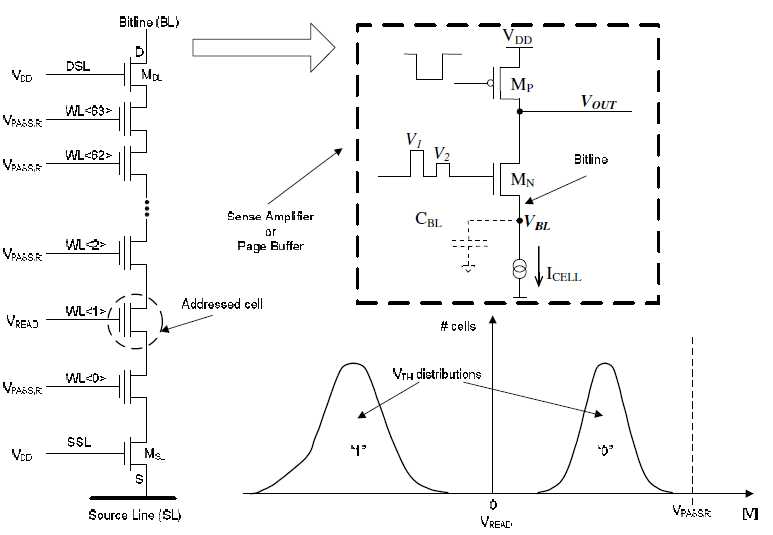

2.DDC:Dynamic Data cache(包括SDC,PDC,TDC,DDC1,DDC2),有的解析为Page buffer,或者sense Amps。

镁光的NAND flash:L94C:单die 8G,L95B:单die 16G

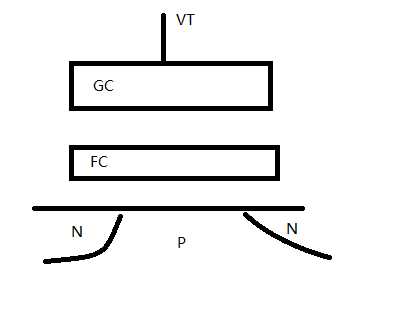

大致的物理结构图:

所以体积:2个L94C颗粒 > 1个L95B颗粒

3.Block Select Circuit

4.Data Path(把数据传送到接口的通路)

5.charge Pump(把外部供给的5V电压--->内部20V)

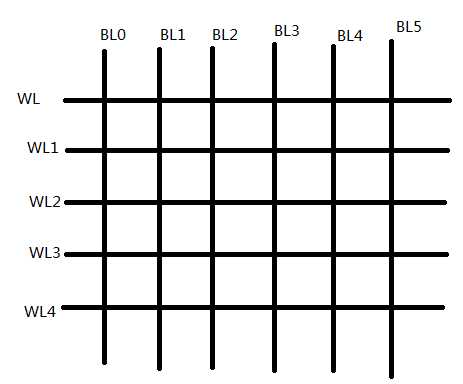

Bl:bitline又分为ABL(all bitline) SBL(Sheild bitline)

注意:16K的page:会有16384根bitline。

注意:L95B为SBL

1WL下有4个page:even lower page,odd lower page,even upper page,odd upper page

phsion emmc颗粒L94C。

open block:没写完的Block

a.slc open:写小数据

b.Mlc open:写大数据

c.slc backup:备份

一般一个颗粒中 bitline会保留一些余量,我们是看不到的。bitline如果坏了,是可以做替换repaire的。

一个颗粒中,Dummy wordline会有2个,最顶上一个和最底下一个。

NVDDR1模式:发cmd时,以clk的上升沿触发

Data Input时:NVDDR1和NVDDR2以DQS为准;Asy模式以WR信号为准

Data output时:Asy模式以RE为准,且在稳定期,发出数据。

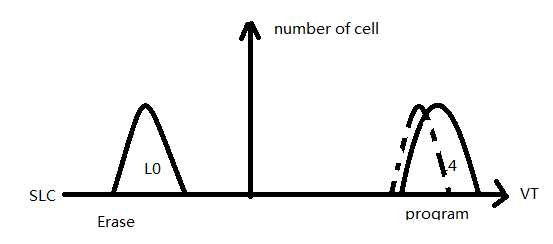

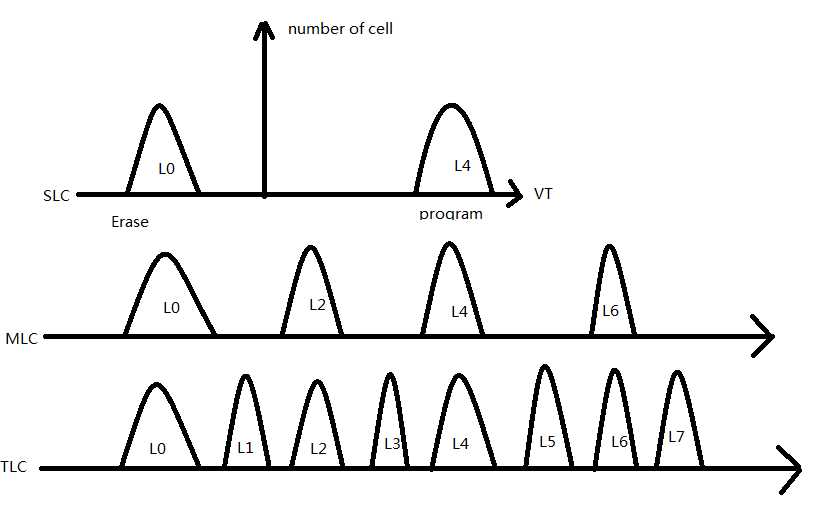

VT:阀值电压

VT(ER)< VT(pro)

program Distrub:会引起如右边的虚线,从而可能导致一次read读取的数据出错,需要read retray,而read retray次数,由你编程决定。

L0是少于0,其它L都是大于0

Write:FC中有电子 0

Erase:FC中无电子 1

注意:阀值电压:VT(ER)<VT(RD)< VT(Wr)

注意:Vpass>VT(write)>VT(Erase)

回流焊:最高温度260度,200度以10S

镁光/记忆:只能保证2次回流焊。

镁光的颗粒,Spec上说3K PEC,实际可达到5K~7K

东芝的颗粒,Spec上3K,那就3K。

one pass program:电压控制比较难

two pass program:2,8原理。

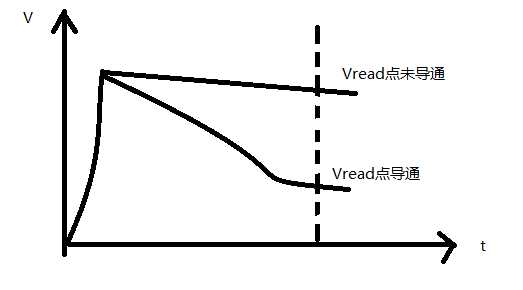

判断V(read)是P/E状态:

(1):先充电bitline===》Bl一个高电压VD。

(2):其它三极管加Vpass电压。

(3):给V(read)加0

状态图:

标签:stat play 控制 path 模式 mmc 读取 repair data

原文地址:http://www.cnblogs.com/Caden-liu8888/p/6492860.html