标签:转换器 dir 需求 dac 进制 系统 需要 技术 用户

直接数字频率合成( Dir ect Dig ital Frequency Synthesis,DDS) 是一种新型的频率合成技术,它把信号发生器的频率稳定度、准确度提高到与基准频率相同的水平,并且可以在很宽的频率范围内进行精细的频率调节。在现代通信领域中,DDS 的应用极其广泛。实现DDS 常用的方法是采用专用的DDS 芯片,控制部分采用独立的MCU ,这样设计出来的系统的集成度和扩展性不尽人意。随着大规模现场可编程门阵列的推出,SOPC 的不断发展,设计人员可以在FPGA 的嵌入式软核处理器上设计各种系统,满足用户需求。本文基于SOPC 技术设计直接数字频率合成器,选用A ltera公司的新一代FPGA( Cyclone Ⅱ) 为核心,利用FPGA的逻辑单元实现相位累加等数字逻辑功能,在ROM 中分别放入正弦表、方波表、三角波表、锯齿波表,用软核CPU 做控制,实现频率、相位、波形选择等。这样可以大大减小处理器外围扩展电路数目,还提高了系统的稳定性和抗干扰能力,节省了内部资源。

1 系统方案设计

系统采用SOPC 设计方案。整体系统框图如图1所示,它由频率预置电路、波形选择、波形频率控制、累加器、存储波形数据的存储器和D/ A 转换电路、滤波电路组成。累加器模块由10 位加法器与10 位寄存器级联而成。波形存储器中放入正弦波、方波、三角波、锯齿波的数据。

1. 1 DDS 基本工作原理

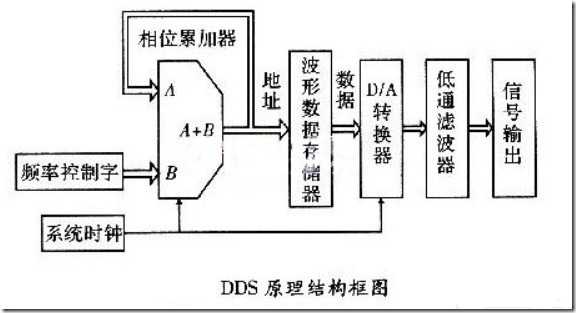

DDS 的基本原理是利用采样定理,通过查表法产生波形。一个完整DDS 结构图如图2 所示。

相位累加器在每一个时钟上升沿与频率控制字K累加一次,当累加器计数大于2N 时,相位累加器相当于进行一次取模运算。在每一个时钟周期内,根据送给ROM 的地址,取出ROM 中与该地址相对应的波形的数据,读取出ROM 中的数据后通过D/ A 转换器,将数字量转换成模拟量,通过低通滤波电路,可输出一个平滑的波形。

当K = 1 时,DDS 有最小频率输出,因此DDS 的步长为f clk / 2N ,最大输出频率为f clk / 2。在本设计中,将N 设定为10 位,M 设定为12 位,相位累加器在时钟的控制下,以步长K 进行累加,输出N 位二进制码,并以其作为波形ROM 的地址,对波形存储器ROM 寻址,波形存储器ROM 输出的数据经过D/ A 转换成阶梯波后,经过低通滤波器平滑后,便得到合成后的波形了,合成后的波形形状取决于波形选取和ROM 中的数据。

原理图如下:

1. 2 D/ A 转换器

从DDS 核输出的是一个数字信号,需要将数字信号转换成模拟信号,才能便于观察。DAC 有电压和电流输出两种,其输出的信号并不能真正连续可变,而是以其绝对分辨率为最小单位,所以它的输出实际上是一个阶梯模拟信号,所以需要将D/ A 输出的信号通过低通滤波器平滑后得到纯净的模拟信号。在该设计中用到型号为AD9742 的D/ A 转换器,AD9742 是具有12 位、低功耗、转换速度可达到100 Mb/ s 的D/ A 转换器。

标签:转换器 dir 需求 dac 进制 系统 需要 技术 用户

原文地址:http://www.cnblogs.com/bgd140206103/p/6602568.html