标签:百度 数码 计算 产生 部分 工业 sata 请求 发生器

一、实验背景

在消费者电子电讯和工业电子中看上去不相关的设计里经常有很多相似的地方例如几乎每个系统都包括一些智能控制通常是一个单片的微控制器,通用电路例如LCD驱动器远程I/O,RAM,EEPROM或数据转换器,面向应用的电路譬如收音机和视频系统的数字调谐和信号处理电路或者是音频拨号电话的DTM发生器,为了使这些相似之处对系统设计者和器件厂商都得益而且使硬件效益最大电路最简单Philips开发了一个简单的双向两线总线实现有效的IC之间控制这个总线就称为Inter IC或I2C总线现在Philips包括超过150种CMOS和双极性兼容I2C总线的IC可以执行前面提到的三种类型的功能所有符合I2C总线的器件组合了一个片上接口使器件之间直接通过I2C总线通讯这个设计概念解决了很多在设计数字控制电路时遇到的接口问题

二、实验目的

实现EEPROM 24LC64的随机读写和页面读写两种模式,掌握I2C时序驱动方式

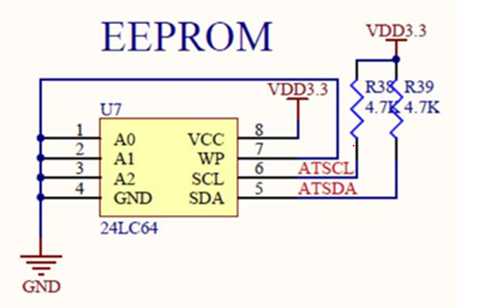

三、实验原理图

四、IIC总线特征

学习I2C,首先我们要知道I2C是一种串行接口,I2C通信是一种串行通信。在实际的数字系统中,我们的数据经常是以并行的方式产生及存储的。而将数据通过进行传输时,通常会是串行地发送和接收的。比如我们常见的SPI,UART,I2C,USB,SATA等接口,均是串行接口。因此,在数字系统中我们经常会遇到需要将串行数据接收下来转为并行数据存储,或者是将并行数据转换成串行数据发送出去的情况。说白了,就是发送端要将数据排个队,一个一个地往外蹦,接收端接收到了这些数据又要将它们像串糖葫芦一个一个串起来,成为并行的数据。

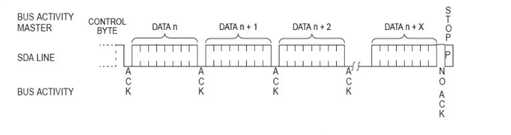

五、IIC总线读写时序

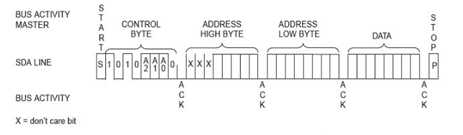

图1随机写

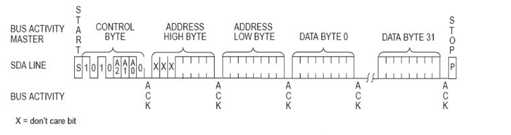

图2页面写

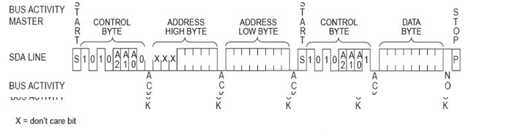

图3随机读

图4页面读

六、实验原理

实验1:写控制按键按下的时候,FPGA在EEPROM中某一个固定的地址写入一个固定的数据,然后当读请求按键按下的时候,FPGA从该固定地址读出这一个字节的数据并发送到数码管显示。

实验2:写控制按键按下的时候,FPGA在EEPROM中某一个固定的地址开始连续写入两个固定的数据,然后当读请求按键按下的时候,FPGA从该固定地址开始连续读出这两个字节的数据同时将这两个数的和值计算出来并发送到数码管显示。

七、实验分析

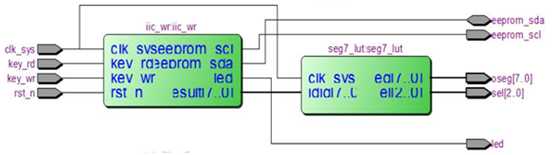

a)建立相应模块

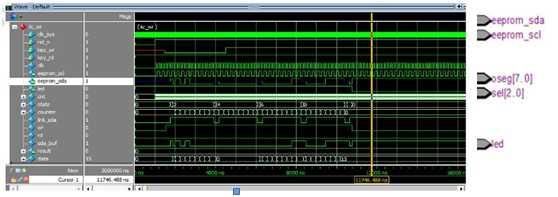

b)随机读写实验仿真写时序

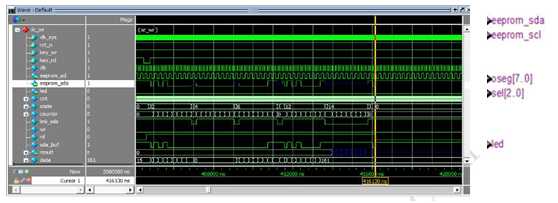

c)随机读写实验仿真读时序

八、实验结果

1:随机读写

初始状态,Led点亮说明写入完成读出数据,

2:页面读写

读出两个数的和值

九、仿真注意事项

由于我们的仿真测试代码中没有提供ACK的逻辑,所以仿真的时候,在控制器代码中涉及到检测ACK的部分必须跳过去,状态直接向下跳转才可以运行,而且我们时钟分频计数到250,这对仿真来说时间太长了,也需要改短。

百度贴吧视频分享链接:http://tieba.baidu.com/p/5016391594?ie=utf-8

v3学院作为国内最专业的FPGA培训机构,秉承授业解惑,打造匠人精神的宗旨为全国的fpga爱好者提供短期技能指导、长期职前培训!

标签:百度 数码 计算 产生 部分 工业 sata 请求 发生器

原文地址:http://www.cnblogs.com/Y---L----/p/6610645.html