标签:发展 family img 数据 芯片 pre cache 规律 提升

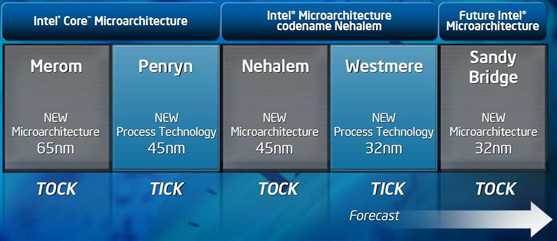

Tick-Tock是Intel发展微处理器芯片设计制造业务的一种战略模式。Intel指出,每一次处理器微架构的更新和每一次芯片制程的更新遵循“Tick-Tock”规律,名称源于时钟秒针行走时所发出的声响。每一次“Tick”代表着一代微架构的处理器芯片制程的更新,而每一次“Tock”代表着在上一次“Tick”的芯片制程的基础上,更新微处理器架构提升性能。一般一次“Tick-Tock”的周期为两年,“Tick”占一年,“Tock”占一年。

一个例子,下面loop1和loop2 哪个执行快

int []arr = new int[64 * 1024 * 1024]; // Loop 1 for (int i = 0; i < arr.Length; i++) arr[i] *= 3; // Loop 2 for (int i = 0; i < arr.Length; i += 16) arr[i] *= 3;

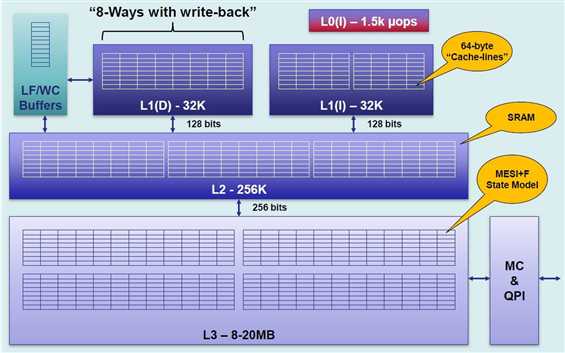

第二个循环只执行了第一个1/16的计算量,但是两个循环在计算机上的耗时是差不多的70-80ms;造成这个问题的原因在于cpu cache line是64bytes,每次从内存加载64Bytes数据到cache;

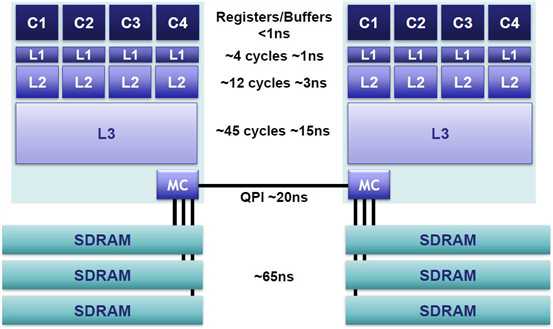

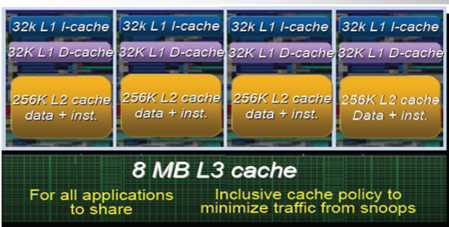

3.1 Nehalem(三级)结构

L1(每核独有) 数据32k 指令32K分开

L2(每核独有) 256K

L3(共享) 8M

标签:发展 family img 数据 芯片 pre cache 规律 提升

原文地址:http://www.cnblogs.com/happyliu/p/6683927.html