标签:类型 技术分享 之间 detail 技术 分享 时钟 www bsp

转载自: http://www.chipsbank.com/news_detail/newsId=124.html

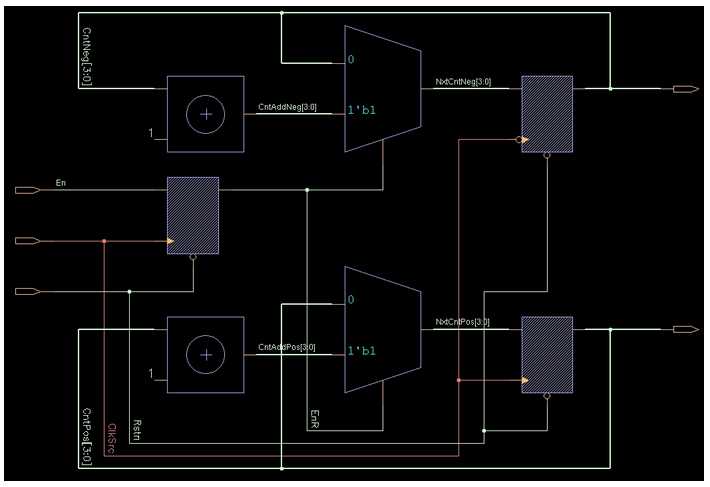

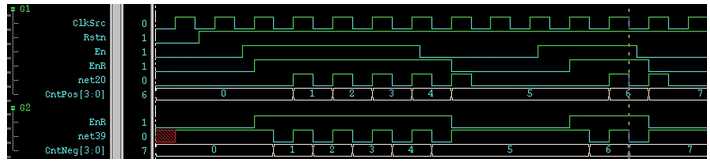

4bit带使能计数器,包括正沿触发与负沿触发;

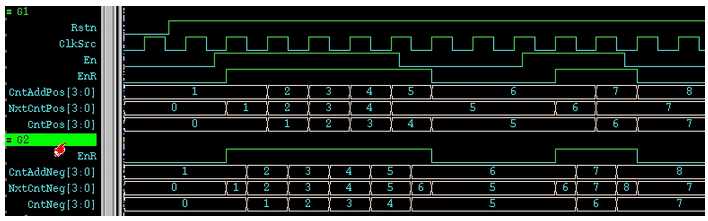

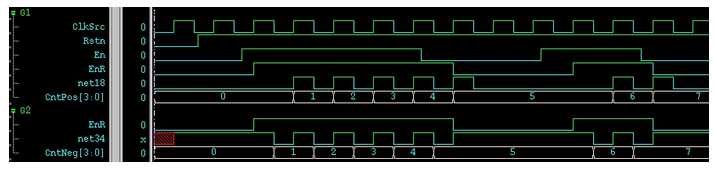

1.功能仿真:

1.电路结构与仿真波形:

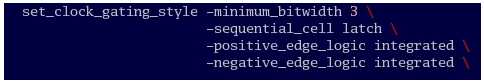

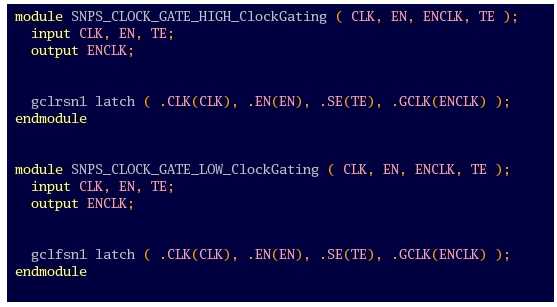

2. 插入带latch的ICG(集成门控):

1.综合脚本:

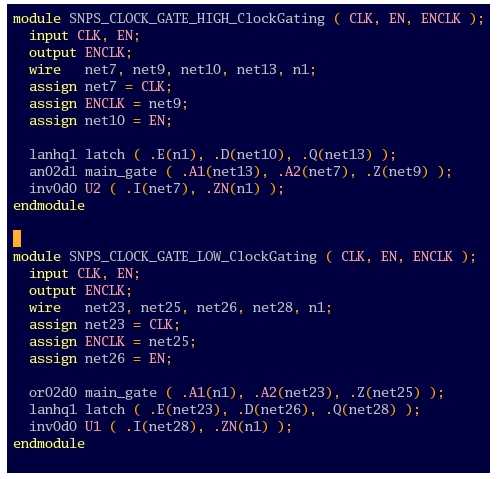

2. 门控综合结果:

3.仿真波形:

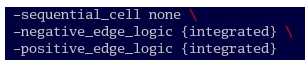

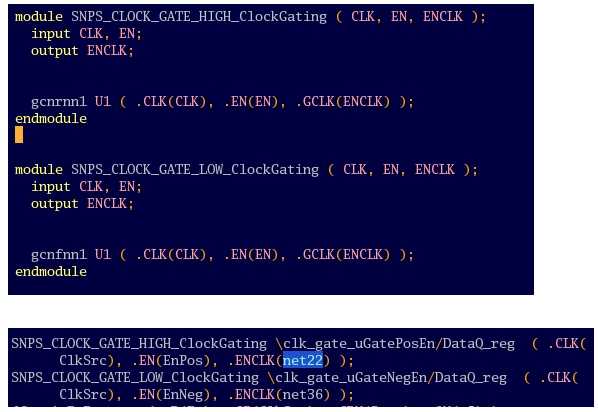

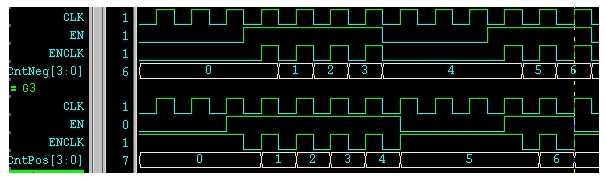

3.插入不带latch的ICG:

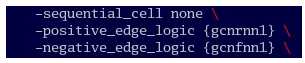

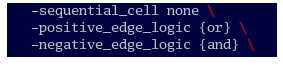

1. 综合脚本:

1.需要查找库中是否存在不带Latch的ICG;

2. 需要分别选择上升沿触发寄存器和下降沿触发寄存器的对应门控单元;

3.脚本:

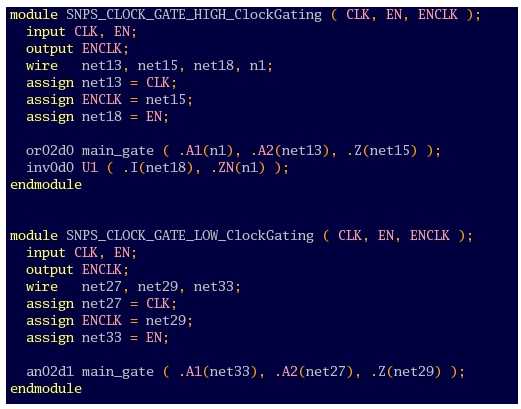

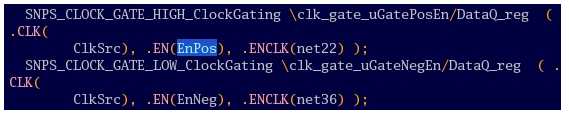

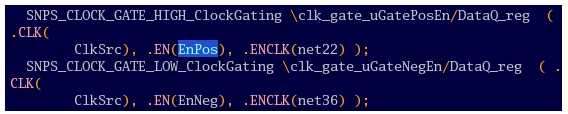

2.综合结果:

3.仿真时序图:

4. 注意点:

1.有上升沿输出的使能(这个使能只要是通一个时钟输出的上升沿信号组合出来的都可以)控制上升沿促发的寄存器才可以插入上升沿类型的ICG;

2.只有下降沿输出的使能(这个使能只要是通一个时钟输出的上升沿信号组合出来的都可以)控制下降沿促发的寄存器才可以插入下降沿类型的ICG;

3.如果要使用上升沿组合成的使能来门控下降沿的门控或反之,则需要手工例化ICG,或写门控逻辑来门控。

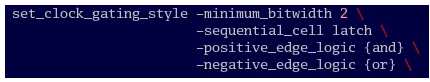

4. 如果在综合脚本改成下面的脚本,综合会保持,结果会插入带latch结构的ICG;

4.插入带latch的分立门控:

1.门控综合脚本:

2.门控综合结果:

3. 仿真波形:

5. 插入不带latch的分立门控:

1.综合脚本:

2.综合结果:

3.仿真波形:

4. 注意点:

1.只有上升沿输出的使能(这个使能只要是通一个时钟输出的上升沿信号组合出来的都可以)控制上升沿促发的寄存器才可以插入上升沿类型的CG;

2.只有下降沿输出的使能(这个使能只要是通一个时钟输出的上升沿信号组合出来的都可以)控制下降沿促发的寄存器才可以插入下降沿类型的CG;

3. 如果要使用上升沿组合成的使能来门控下降沿的门控或反之,则需要手工例化CG,或写门控逻辑来时序。

6.遗留问题

1.门控cell的选择加上路径看看。

2. DC会保证En在上升沿和下降沿之间?

标签:类型 技术分享 之间 detail 技术 分享 时钟 www bsp

原文地址:http://www.cnblogs.com/hxing/p/6720823.html