标签:alt .com style images ima http class 定时 技术分享

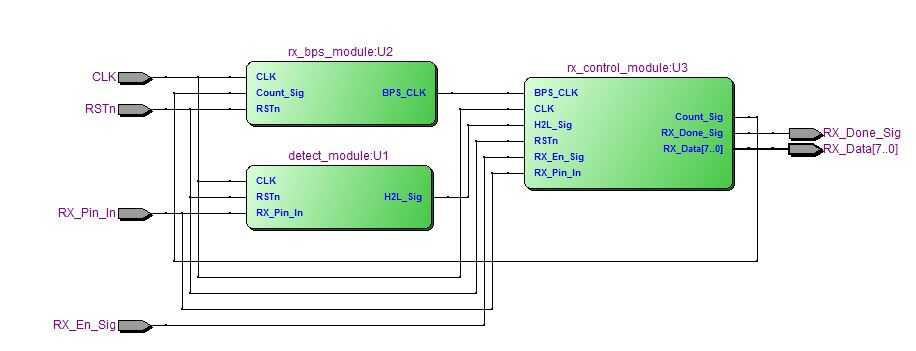

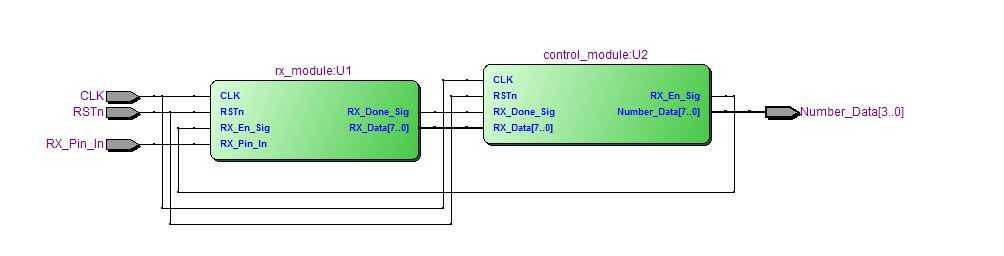

FPGA学习之串口接收模块

原文弊端,串口每次只能接受一个,再接受需要先关闭串口再打开才有效。(可能是软件问题,换一个之后OK)

首先是改波特率,例程为9600,改成115200.

115200 bps 传输速度使一位数据的周期是 0.0000086805s 。以 50Mhz 时钟频率

要得到上述的定时需要:

N = 0.0000086805 / ( 1 / 50Mhz ) = 434

1 module rx_bps_module 2 ( 3 CLK, RSTn,Count_Sig, BPS_CLK 4 5 ); 6 input CLK; 7 input RSTn; 8 input Count_Sig; 9 output BPS_CLK; 10 11 /******************************/ 12 13 reg [12:0]Count_BPS; 14 15 /******************************/ 16 17 always @ ( posedge CLK or negedge RSTn ) 18 if( !RSTn ) 19 Count_BPS <= 13‘d0; 20 // else if(Count_BPS == 13‘d5207 )// 9600 bps 传输一位数据时间 21 else if(Count_BPS == 13‘d433 )// 115200 bps 传输一位数据时间 22 Count_BPS <= 13‘d0; 23 else if( Count_Sig ) //计数信号使能 24 Count_BPS <= Count_BPS + 1‘b1; 25 else 26 Count_BPS <= 13‘d0;//计数信号no使能 27 28 /********************************/ 29 assign BPS_CLK = ( Count_BPS == 12‘d217 ) ? 1‘b1 : 1‘b0;//一个周期的二分之一时间时,产生一个高脉冲 30 31 /*********************************/ 32 33 34 35 36 endmodule

标签:alt .com style images ima http class 定时 技术分享

原文地址:http://www.cnblogs.com/gym-2017/p/6792455.html