标签:style blog http color 使用 ar 数据 2014 art

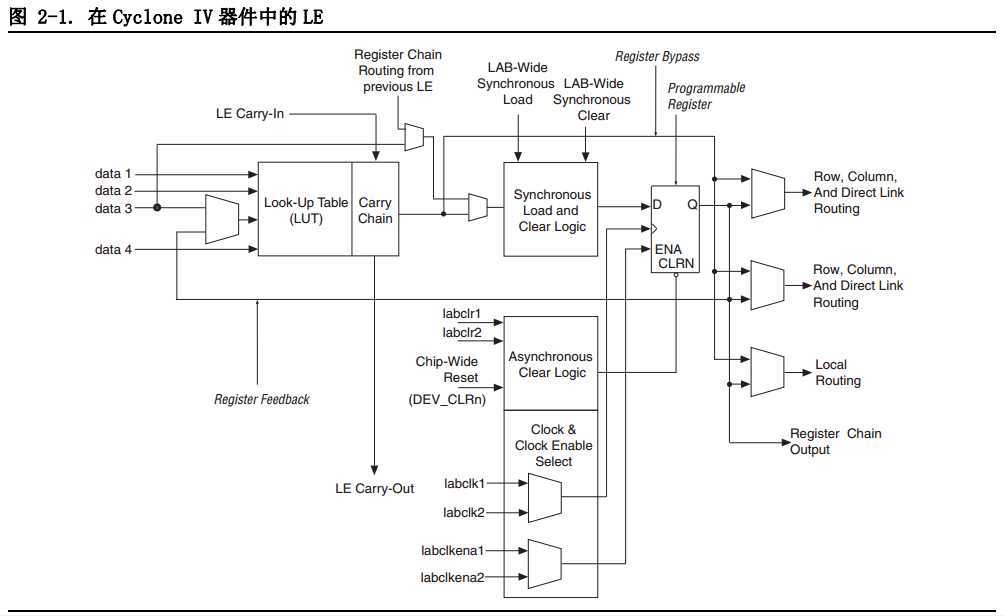

逻辑单元 (LE) 在 Cyclone IV 器件结构中是最小的逻辑单位。LE 紧密且有效的提供了高级功能的逻辑使用。每个 LE 有以下特性

■ 一个四口输入的查找表 (LUT),以实现四种变量的任何功能

■ 一个可编程的寄存器

■ 一个进位链连接

■ 一个寄存器链连接

■ 可驱动以下的相互连接:

■ 本地

■ 行

■ 列

■ 寄存器链

■ 直联

■ 寄存器套包支持

■ 寄存器反馈支持

您可以对每个 LE 配置可编程的寄存器为 D、 T、 JK, 或 SR 触发器操作。每个寄存器上有数据,时钟,时钟使能和清零输入。全局时钟网络,通用 I/O 管脚,任何内部逻辑

都可以驱动时钟和清零寄存器控制信号。通用 I/O 管脚或内部逻辑都可以驱动时钟使能。对于组合功能,LUT 输出端旁路寄存器直接驱动到 LE 输出端。

每个 LE 有三个输出端分别驱动本地,行和列的布线资源。LUT 或寄存器输出独立地驱动这三个输出端。两个 LE 输出端驱动列或行以及直接链接布线连接,而另一个 LE 则

驱动本地互联资源。这允许 LUT 驱动一个输出端,当寄存器驱动另一个输出端时。这个特性称为寄存器套包,由于器件可以使用寄存器和 LUT 在不相关的功能,增加了器件的利用率。LAB-wide 同步加载控制信号在使用寄存器套包时是不可用的。(寄存器套包是个啥啊)

每个 LAB 包括以下特性:

■ 16 LE

■ LAB 控制信号

■ LE 进位链

■ 寄存器链

■ 本地互联

每个 LAB 都包含专用的逻辑以驱动控制信号各自 LE。控制信号包括:

■ 两个时钟

■ 两个时钟使能

■ 两个异步清零

■ 一个同步清零

■ 一个同步加载

您可以一次使用多达 8 个的控制信号。寄存器套包和同步加载不能被同时使用。

时钟和时钟使能信号在各个 LAB 上是相连接的。例如,在一特定的 LAB 上的任何一个 LE 中使用labclk1信号时也在使用labclkena1。如果 LAB 同时使用上升沿和下降沿时钟,也使用 LAB-wide 时钟信号。释放时钟使能信号关闭 LAB-wide 时钟。(不明白有什么作用)

LAB-wide 信号控制寄存器上清零信号的逻辑。LE 直接支持一个异步清零功能。每个LAB 支持多达两个异步清零信号 (labclr1和labclr2)。一个 LAB-wide 异步加载信号不可被用为寄存器的预置信号控制逻辑。寄存器预置是用NOT 门推回 (push-back)的技术完成的。Cyclone IV 器件仅支持预置或异步清零信号。

除了清零端口外,Cyclone IV 器件提供一个芯片级重置管脚 (DEV_CLRn) 对器件中所有的寄存器重置。在编辑 Quartus II 软件之前设置一个选项以控制这个管脚。这个芯

片级重置覆盖了所有其他的控制信号。(这个端口在)

DEV_CLRn复位管脚对整个FPGA板子上的寄存器都有复位功能。在Enable device-wide reset (DEV_CLRn)选项on的情况下,可以不用设置复位管脚,如果是off,就需要设置复位管脚。一般DEV_CLRn也可以做复位管脚的。

笔记之Cyclone IV 第一卷第二章Cyclone IV器件的逻辑单元和逻辑阵

标签:style blog http color 使用 ar 数据 2014 art

原文地址:http://www.cnblogs.com/sepeng/p/3940587.html