标签:lock image 名称 科学 lin uri please 成功 led

? 最新消息请看最后~

我的任务是分析Verilog程序中的算法...于是自然搭配Xilinx(赛灵思)发布的vivado集成开发环境进行分析.我用的版本是vivado 2017.1版本,在这之前,2014.4版本总是会出现各种奇怪的错误...比如编译时出现:

[Vivado 12-1345] Error(s) found during DRC.Bitgen not run.

[USF-XSim 62] ‘compile‘ step failed witherror(s). Please check the Tcl console output or ‘‘ file for more information.

‘compile‘步骤失败并出现错误。 请查看Tcl控制台输出或“‘文件以获取更多信息。

然而在2017.1中就不会出现这个问题...

不过2017.1版本也有一些缺点.

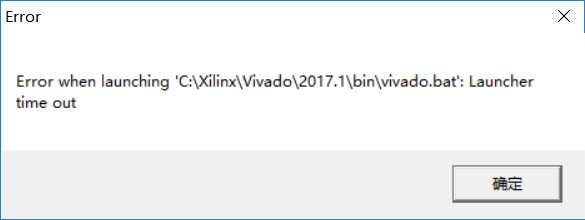

首先,它和VS2017不兼容(VS2015没有问题),所以我在win7虚拟机上运行的.其次,它在虚拟机中运行地太慢了...经常会等个一两分钟,才慢悠悠地显示主界面.在这期间会跳出

不用担心,最后还是会正常运行的...(也有可能是因为我电脑配置太低)

作为一个穷学生,我用的是webpack版本,即下即安.不过下载可能需要科学上网...我也不懂为什么...

最新消息...在学长的帮助下,我终于可以同时安装VS2017和vivado2017.1了...

其实方法也不难,只要在它的路径中C:\Xilinx\Vivado\2017.1\tps\win64将两个文件的名称改了就可以了,分别是vcredist_x64.exe和xvcredist.exe...谁知道这是为什么呢?好像是因为vivado以为VC安装包没有安装成功,所以会不断调用这个安装包?

标签:lock image 名称 科学 lin uri please 成功 led

原文地址:http://www.cnblogs.com/qrzbing/p/6940290.html