标签:des style blog http os 使用 io ar for

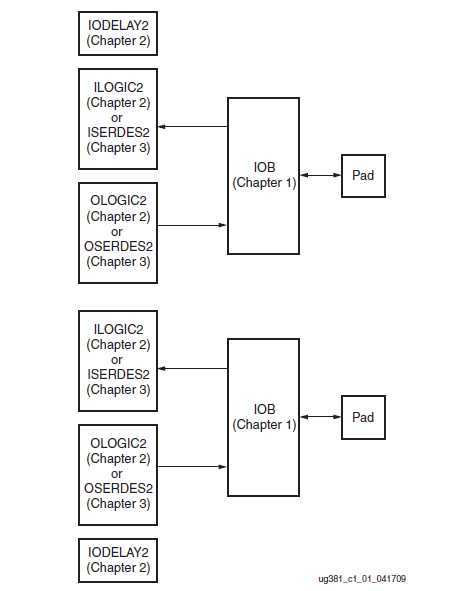

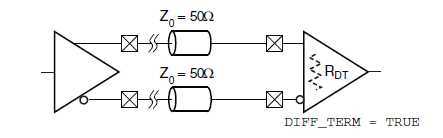

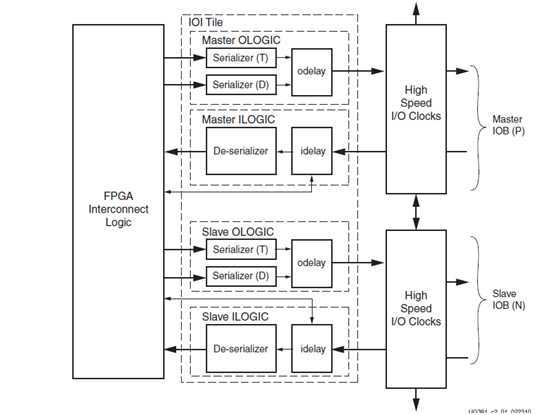

对Spartan-6系列FPGA来说,一个IO Tile包括2个IOB、2个ILOGIC、2个OLOGIC、2个IODELAY。

图 1Spartan-6系列IO Tile结构图

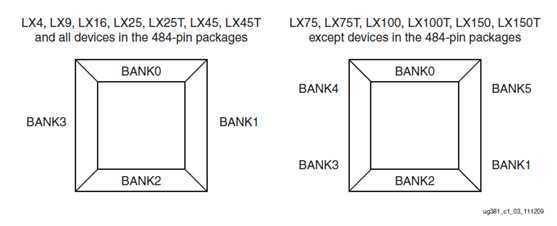

图 2Spartan-6 FPGA I/O Banks

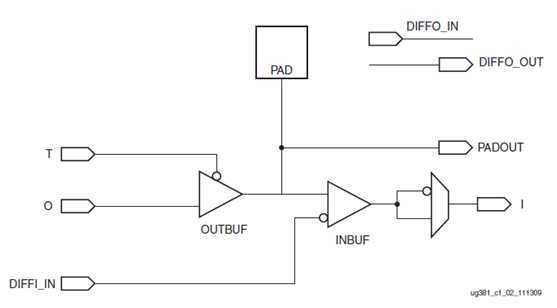

每个IOB包含了输入、输出、三态驱动器;这些驱动器可以配置为不同的电平标准如LVTTL、LVCMOS等;差分IO会用到1个IO Tile里的两个IOB。

每个IOB都被直接连接到了ILOGIC和OLOGIC,ILOGIC和OLOGIC可以被配置成ISERDES或OSERDES,。

图 3基本IOB结构图

高速IO电平标准的使用可以优化电平转换特性和信号完整性,在高速IO电平标准中往往需要使用终端电阻。终端电阻的位置应该距离接收器越近越好。

Spartan-6 FPGA为差分IO和单端IO提供了片内终端电阻,这个终端电阻位于IOB内部,使用这些终端电阻,可以避免FPGA外部再引脚处再接电阻。

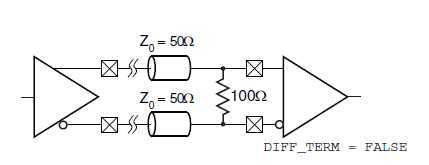

Spartan-6系列为差分IO提供了100Ω的终端电阻,差分引脚的终端电阻可以通过约束文件使之使能或不使能。

图 4差分引脚使能终端电阻

图 5差分引脚不使能终端电阻

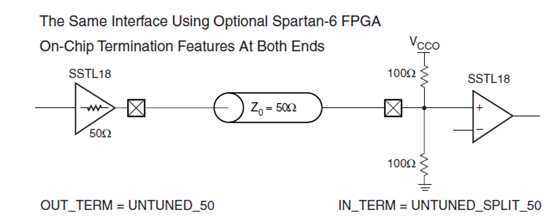

单端引脚的输入终端电阻和输出阻抗都是可编程控制的,如下图所示:左边FPGA的输出使能了50Ω的输出阻抗,右边的FPGA使能了输入50%分压电阻;在高速接口应用中,使能输出阻抗可以减少电磁反射,Spartan-6系列FPGA输出阻抗可选值为None、25Ω、50Ω、75Ω;输入阻抗可设置为25%、50%、75%分压。

图 6单向SSTL接口使用片上终端电阻

IOB内部有多种输入输出缓冲资源(buffer resource),他们可以原语的形式调用,在Spartan-6系列里,单端IO标准的原语如下5个:

|

原语 |

功能 |

|

IBUF |

输入缓冲 |

|

IBUFG |

时钟输入缓冲 |

|

OBUF |

输出缓冲 |

|

OBUFT |

输出三态缓冲 |

|

IOBUF |

输入输出缓冲 |

同时有7个差分IO标准的原语

|

原语 |

功能 |

|

IBUFDS |

输入缓冲 |

|

IBUFGDS |

时钟输入缓冲 |

|

IBUFDS_DIFF_OUT |

取反输出缓冲 |

|

IBUFGDS_DIFF_OUT |

时钟取反输出缓冲 |

|

OBUFDS |

输出缓冲 |

|

OBUFTDS |

三态输出缓冲 |

|

IOBUFDS |

输入输出IO缓冲 |

IOB支持多种电平标准,用户可以自由灵活地为自己的设计选择合适的IO电平标准,Spartan-6系列支持的IO电平标准如下

|

标准 |

解释 |

用途及厂商 |

输入缓冲 |

输出缓冲 |

|

单端IO电平标准 |

||||

|

LVTTL |

Low Voltage TTL |

General purpose 3.3V |

LVTTL |

Push-Pull |

|

LVCMOS |

Low Voltage CMOS |

General purpose |

CMOS |

Push-Pull |

|

PCI |

Peripheral Component Interconnect |

PCI bus |

LVTTL |

Push-Pull |

|

I2C |

Inter Integrated Circuit |

NXP |

CMOS |

Open drain |

|

SMBUS |

System Management Bus |

Intel |

CMOS |

Open drain |

|

SDIO |

Secure Digital Input Output |

SD Card Assoc, Memory Card |

CMOS |

Push-Pull |

|

Mobile DDR |

Low Power DDR |

|

CMOS |

Push-Pull |

|

HSTL |

High-Speed Transceiver Logic |

Hitachi SRAM; IBM; three of four classes supported |

Vref based |

Push-Pull |

|

HSTL18 |

High-Speed Transceiver Logic |

Hitachi SRAM; IBM; three of four classes supported |

Vref based |

Push-Pull |

|

SSTL3 |

Stub Series Terminated Logic for 3.3V |

SDRAM bus; Hitachi and IBM; two classes |

Vref based |

Push-Pull |

|

SSTL2 |

SSTL for 2.5V |

DDR SDRAM |

Vref based |

Push-Pull |

|

SSTL18 |

SSTL for 1.8V |

DDR SDRAM |

Vref based |

Push-Pull |

|

SSTL15 |

SSTL for 1.5V |

DDR SDRAM |

Vref based |

Push-Pull |

|

差分IO电平标准 |

||||

|

LVDS25 LVDS33 |

Low Voltage Differential Signaling |

High-speed interface, backplane, video; National, TI |

Differential Pair |

Differential Pair |

|

BLVDS |

Bus LVDS |

Bidirectional, multipoint LVDS |

Differential Pair |

Pseudo Differential Pair |

|

DISPLAY PORT |

Auxiliary channel interface for DISPLAY PORT |

Flat panel displays |

Differential Pair |

Pseudo Differential Pair |

|

LVPECL |

Low Voltage Positive ECL |

High-speed clocks |

Differential Pair |

N/A |

|

MINI_LVDS |

mini-LVDS |

Flat panel displays |

Differential Pair |

Differential Pair |

|

RSDS |

Reduced Swing Differential Signaling |

Flat panel displays |

Differential Pair |

Differential Pair |

|

TMDS |

Transition Minimized Differential Signaling |

Silicon Image; DVI/HDMI |

Differential Pair |

Differential Pair |

|

PPDS |

Point-to-Point Differential Signaling |

LCDs |

Differential Pair |

Differential Pair |

|

Differential Mobile DDR |

Differential LPDDR for CK/CK# |

|

Differential Pair |

Pseudo Differential Pair |

|

DIFF_HSTL_I DIFF_HSTL_III DIFF_HSTL_IV DIFF_HSTL_I_18 DIFF_HSTL_III_18 DIFF_HSTL_IV_18 |

Pseudo Differential HSTL |

SRAM |

Differential Pair |

Pseudo Differential Pair |

|

DIFF_SSTL3_I DIFF_SSTL3_II DIFF_SSTL2_I DIFF_SSTL2_II DIFF_SSTL18_I DIFF_SSTL18_II DIFF_SSTL15_II |

Pseudo Differential SSTL |

DDR, DDR2, DDR3 SDRAM |

Differential Pair |

Pseudo Differential Pair |

在默认情况下,在FPGA配置完成后,所有未使用的引脚将被配置成输入,并在IOB内部经下拉电阻接地,这种未使用引脚在配置后的状态可以通过UnusedPin BitGen option进行设定。

SelectIO的逻辑资源包括基本资源和高级资源,其中,基本资源包括:

高级资源包括:

selectIOn逻辑资源被组合在一个IO Tile内部,如下图所示,在单端模式中,master I/O buffer驱动P Pad,slave I/O buffer驱动N Pad;在差分模式中,master I/O buffer和slave I/O buffer组合起来使用,可以完成串并或者并串转换。

图 7一个I/OTile里的selectIO逻辑资源

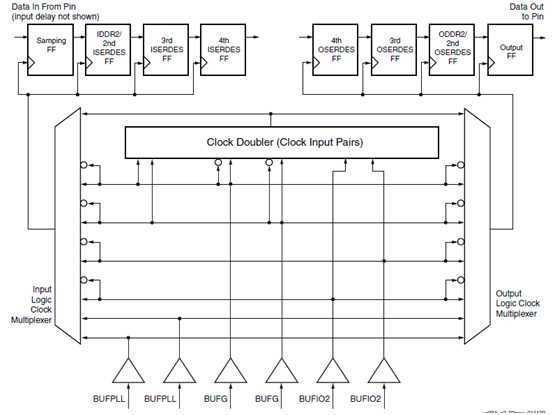

所有IO的数据采集和转换(包括串并转换和并串转换)、DDR传输等都需要一个内部SDR时钟,为了实现这些功能,I/O接口Tile需要一个本地的时钟倍频器来获取SDR时钟。

进行DDR传输的倍频器需要两个输入时钟,这两个输入时钟必须是下面三种情况之一:

图 8IO接口逻辑的时钟资源

Spartan6系列之SelectIO深入详解及高级应用简介

标签:des style blog http os 使用 io ar for

原文地址:http://www.cnblogs.com/dhyc/p/3947101.html