标签:nop tcl gen ifd pix int define val standard

参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形。

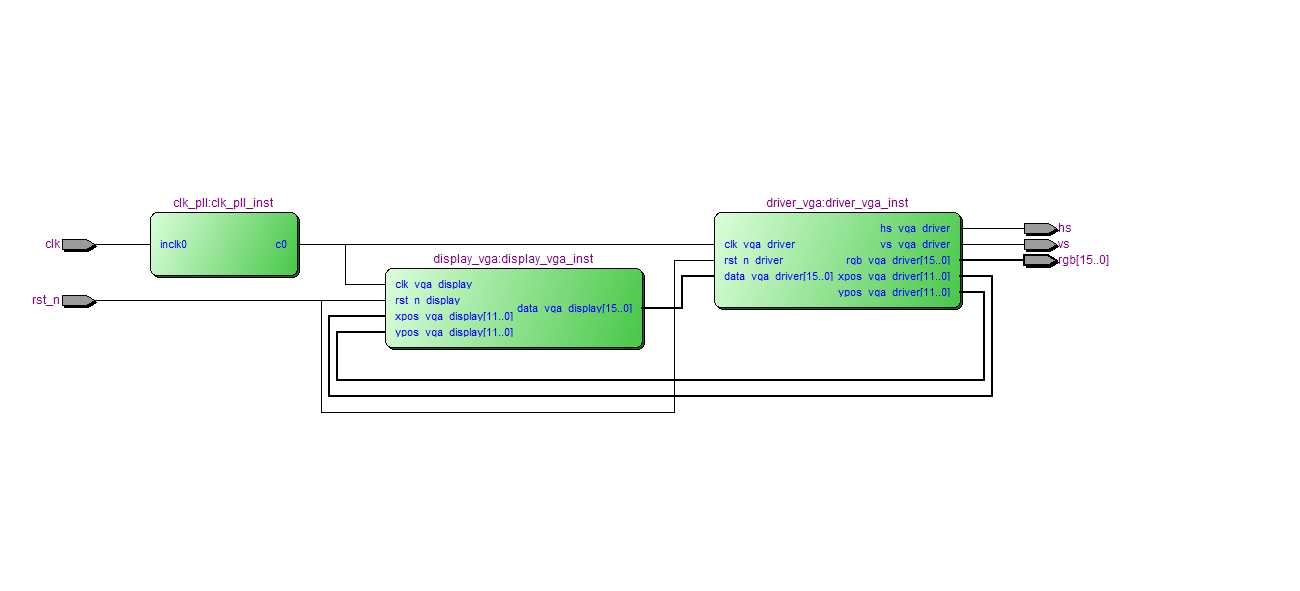

1 /**************************************************** 2 * Module Name : VGA_color_all.v 3 * Author : yllinux 博客:http://www.cnblogs.com/yllinux/ 4 * Target Device : Cyclone IV E ( EP4CE6F17C8 ) 5 * Tool versions : Quartus II 12.1 6 * Create Date : 2017-7-29 7 * Revision : v1.0 8 * Description : 彩条显示模块化,并增加几种显示模式 9 *****************************************************/ 10 11 module VGA_color_all 12 ( 13 input clk, 14 input rst_n, 15 16 output hs, 17 output vs, 18 output [15:0] rgb 19 ); 20 21 /***************************************************** 22 分辨率选择,取消注释的有效 23 ******************************************************/ 24 //`define resolution_1280_1024_60FPS_108MHz 25 //`define resolution_1024_768_60FPS_65MHz 26 `define resolution_1920_1080_60FPS_148MHz 27 //`define resolution_ 28 //`define resolution_ 29 //`define resolution_800_600_72FPS_50MHz 30 //`define resolution_640_480_60FPS_25MHz 31 32 /**************************************************** 33 参数配置,其中的 DELAY 项可调 [0, 31] 34 ****************************************************/ 35 `ifdef resolution_1280_1024_60FPS_108MHz 36 parameter 37 DELAY = 5‘d3, //模式切换延时 38 DUTY_CYCLE = 50, //PLL占空比 39 DIVIDE_DATA = 25, //PLL除 40 MULTIPLY_DATA = 54, //PLL乘 41 PIXEL_FREQUENCY = 28‘d108_000000, //像素时钟,1秒 42 H_DISP = 12‘d1280, //行显示 Hor Addr Time 43 H_FRONT = 12‘d48, //行同步前 H Front Porch 44 H_SYNC = 12‘d112, //行同步 Hor Sync Time 45 H_BACK = 12‘d248, //行同步后 H Back Porch 46 H_TOTAL = 12‘d1688, //行总计 Hor Total Time 47 V_DISP = 12‘d1024, //场 Ver Addr Time 48 V_FRONT = 12‘d1, // V Front Porch 49 V_SYNC = 12‘d3, // Ver Sync Time 50 V_BACK = 12‘d38, // V Back Porch 51 V_TOTAL = 12‘d1066; // Ver Total Time 52 `endif 53 54 `ifdef resolution_800_600_72FPS_50MHz 55 parameter 56 DELAY = 5‘d3, 57 DUTY_CYCLE = 50, 58 DIVIDE_DATA = 1, 59 MULTIPLY_DATA = 1, 60 PIXEL_FREQUENCY = 28‘d50_000000, 61 H_DISP = 12‘d800, 62 H_FRONT = 12‘d56, 63 H_SYNC = 12‘d120, 64 H_BACK = 12‘d64, 65 H_TOTAL = 12‘d1040, 66 V_DISP = 12‘d600, 67 V_FRONT = 12‘d37, 68 V_SYNC = 12‘d6, 69 V_BACK = 12‘d23, 70 V_TOTAL = 12‘d666; 71 `endif 72 73 `ifdef resolution_640_480_60FPS_25MHz 74 parameter 75 DELAY = 5‘d3, 76 DUTY_CYCLE = 50, 77 DIVIDE_DATA = 2, 78 MULTIPLY_DATA = 1, 79 PIXEL_FREQUENCY = 28‘d25_000000, 80 H_DISP = 12‘d640, 81 H_FRONT = 12‘d16, 82 H_SYNC = 12‘d96, 83 H_BACK = 12‘d48, 84 H_TOTAL = 12‘d800, 85 V_DISP = 12‘d480, 86 V_FRONT = 12‘d10, 87 V_SYNC = 12‘d2, 88 V_BACK = 12‘d33, 89 V_TOTAL = 12‘d525; 90 `endif 91 92 `ifdef resolution_1024_768_60FPS_65MHz 93 parameter 94 DELAY = 5‘d3, 95 DUTY_CYCLE = 50, 96 DIVIDE_DATA = 10, 97 MULTIPLY_DATA = 13, 98 PIXEL_FREQUENCY = 28‘d65_000000, 99 H_DISP = 12‘d1024, 100 H_FRONT = 12‘d24, 101 H_SYNC = 12‘d136, 102 H_BACK = 12‘d160, 103 H_TOTAL = 12‘d1344, 104 V_DISP = 12‘d768, 105 V_FRONT = 12‘d3, 106 V_SYNC = 12‘d6, 107 V_BACK = 12‘d29, 108 V_TOTAL = 12‘d806; 109 `endif 110 111 `ifdef resolution_1920_1080_60FPS_148MHz 112 parameter 113 DELAY = 5‘d3, 114 DUTY_CYCLE = 50, 115 DIVIDE_DATA = 100, 116 MULTIPLY_DATA = 297, 117 PIXEL_FREQUENCY = 28‘d1485_00000, 118 H_DISP = 12‘d1920, 119 H_FRONT = 12‘d88, 120 H_SYNC = 12‘d44, 121 H_BACK = 12‘d148, 122 H_TOTAL = 12‘d2200, 123 V_DISP = 12‘d1080, 124 V_FRONT = 12‘d4, 125 V_SYNC = 12‘d5, 126 V_BACK = 12‘d36, 127 V_TOTAL = 12‘d1125; 128 `endif 129 130 `ifdef resolution 131 parameter 132 DELAY = 5‘d3, 133 DUTY_CYCLE = 134 DIVIDE_DATA = 135 MULTIPLY_DATA = 136 PIXEL_FREQUENCY = 28‘d 137 H_DISP = 12‘d 138 H_FRONT = 12‘d 139 H_SYNC = 12‘d 140 H_BACK = 12‘d 141 H_TOTAL = 12‘d 142 V_DISP = 12‘d 143 V_FRONT = 12‘d 144 V_SYNC = 12‘d 145 V_BACK = 12‘d 146 V_TOTAL = 12‘d 147 `endif 148 149 /************************************************ 150 clk_pll instantiation (PLL核实例化) 151 *************************************************/ 152 wire clk_vga; 153 clk_pll //模块名 154 #( 155 .DUTY_CYCLE ( DUTY_CYCLE ), 156 .DIVIDE_DATA ( DIVIDE_DATA ), 157 .MULTIPLY_DATA ( MULTIPLY_DATA ) 158 ) 159 clk_pll_inst //实例化名 160 ( 161 .inclk0 ( clk ), 162 .c0 ( clk_vga ) 163 ); 164 165 /************************************************ 166 display_vga instantiation (显示模块实例化) 167 *************************************************/ 168 //wire [11:0] xpos_vga_driver; 169 //wire [11:0] ypos_vga_driver; 170 //wire [15:0] data_vga_driver; 171 wire [11:0] xpos_vga; //例化括号里代表连线的名称,上面注释的三条是错的 172 wire [11:0] ypos_vga; 173 wire [15:0] data_vga; 174 display_vga //模块名 175 #( //参数传递 176 .H_DISP ( H_DISP ), 177 .V_DISP ( V_DISP ), 178 .PIXEL_FREQUENCY ( PIXEL_FREQUENCY ), 179 .DELAY ( DELAY ) 180 ) 181 display_vga_inst //实例化名 182 ( 183 .clk_vga_display ( clk_vga ), 184 .rst_n_display ( rst_n ), 185 .xpos_vga_display ( xpos_vga ), 186 .ypos_vga_display ( ypos_vga ), 187 188 .data_vga_display ( data_vga ) 189 ); 190 191 /************************************************ 192 driver_vga instantiation (驱动模块实例化) 193 *************************************************/ 194 driver_vga 195 #( 196 .H_DISP ( H_DISP ), 197 .H_FRONT ( H_FRONT ), 198 .H_SYNC ( H_SYNC ), 199 .H_BACK ( H_BACK ), 200 .H_TOTAL ( H_TOTAL ), 201 .V_DISP ( V_DISP ), 202 .V_FRONT ( V_FRONT ), 203 .V_SYNC ( V_SYNC ), 204 .V_BACK ( V_BACK ), 205 .V_TOTAL ( V_TOTAL ) 206 ) 207 driver_vga_inst 208 ( 209 .clk_vga_driver ( clk_vga ), 210 .rst_n_driver ( rst_n ), 211 .data_vga_driver ( data_vga ), 212 213 .rgb_vga_driver ( rgb ), 214 .hs_vga_driver ( hs ), 215 .vs_vga_driver ( vs ), 216 .xpos_vga_driver ( xpos_vga ), 217 .ypos_vga_driver ( ypos_vga ) 218 ); 219 220 endmodule

1 module driver_vga 2 #( 3 /*********************************************** 4 1280 x 1024 @ 60 Hz 5 ***********************************************/ 6 parameter 7 H_DISP = 12‘d1280, //行显示 Hor Addr Time 8 H_FRONT = 12‘d48, //行同步前 H Front Porch 9 H_SYNC = 12‘d112, //行同步 Hor Sync Time 10 H_BACK = 12‘d248, //行同步后 H Back Porch 11 H_TOTAL = 12‘d1688, //行总计 Hor Total Time 12 13 V_DISP = 12‘d1024, //场 Ver Addr Time 14 V_FRONT = 12‘d1, // V Front Porch 15 V_SYNC = 12‘d3, // Ver Sync Time 16 V_BACK = 12‘d38, // V Back Porch 17 V_TOTAL = 12‘d1066 // Ver Total Time 18 ) 19 ( 20 input clk_vga_driver, //VGA像素时钟 21 input rst_n_driver, //异步复位信号,低电平有效 22 input [15:0] data_vga_driver, //RGB565格式 23 24 output [15:0] rgb_vga_driver, //接收要显示的色彩 25 output reg hs_vga_driver, //VGA管脚 行同步 26 output reg vs_vga_driver, //VGA管脚 场同步 27 output [11:0] xpos_vga_driver, //像素横坐标位置 28 output [11:0] ypos_vga_driver //像素纵坐标位置 29 ); 30 31 /***************************************************** 32 驱动核心,行场同步信号发生器与同步 33 *****************************************************/ 34 reg [11:0] hcnt; //定义行计数器 35 always @ (posedge clk_vga_driver or negedge rst_n_driver) 36 begin 37 if (!rst_n_driver) 38 hcnt <= 12‘d0; 39 else 40 begin 41 if (hcnt <= H_TOTAL - 12‘d1) //行计数取值区间【0, H_TOTAL - 1】 42 hcnt <= hcnt + 12‘d1; 43 else 44 hcnt <= 12‘d0; 45 end 46 end 47 always @ (posedge clk_vga_driver or negedge rst_n_driver) 48 begin 49 if (!rst_n_driver) 50 hs_vga_driver <= 1‘b0; 51 else 52 begin 53 // 像素点区间【H_DISP + H_FRONT, H_DISP +H_FRONT + H_SYNC -1】 54 if (hcnt >= H_DISP + H_FRONT - 12‘d1 && hcnt < H_DISP +H_FRONT + H_SYNC - 12‘d1) 55 hs_vga_driver <= 1‘b1; 56 else 57 hs_vga_driver <= 1‘b0; 58 end 59 end 60 61 reg [11:0] vcnt; 62 always @ (posedge clk_vga_driver or negedge rst_n_driver) 63 begin 64 if (!rst_n_driver) 65 vcnt <= 12‘d0; 66 else 67 begin 68 if (hcnt == H_DISP - 12‘d1) 69 begin 70 if (vcnt < V_TOTAL - 12‘d1) 71 vcnt <= vcnt + 12‘d1; 72 else 73 vcnt <= 12‘d0; 74 end 75 else 76 vcnt <= vcnt; 77 end 78 end 79 always @ (posedge clk_vga_driver or negedge rst_n_driver) 80 begin 81 if (!rst_n_driver) 82 vs_vga_driver <= 1‘b0; 83 else 84 begin 85 if (vcnt >= V_DISP + V_FRONT - 12‘d1 && vcnt < V_DISP + V_FRONT + V_SYNC - 12‘d1) 86 vs_vga_driver <= 1‘b1; 87 else 88 vs_vga_driver <= 1‘b0; 89 end 90 end 91 92 /************************************************************ 93 输出横竖坐标和有效区域数据 94 ************************************************************/ 95 assign xpos_vga_driver = (hcnt < H_DISP) ? hcnt : 12‘d0; //把显示期的行计数值赋给横坐标变量 96 assign ypos_vga_driver = (vcnt < V_DISP) ? vcnt : 12‘d0; //把显示期的场计数值赋给纵坐标变量 97 assign rgb_vga_driver = (hcnt < H_DISP && vcnt < H_DISP) ? data_vga_driver : 16‘d0; //显示期进行图像输出 98 99 endmodule

1 module display_vga 2 #( 3 /*********************************************** 4 1280 x 1024 @ 60 Hz 5 ***********************************************/ 6 parameter 7 H_DISP = 12‘d1280, 8 V_DISP = 12‘d1024, 9 PIXEL_FREQUENCY = 28‘d108_000000, 10 DELAY = 5‘d3 11 ) 12 ( 13 input clk_vga_display, 14 input rst_n_display, 15 input [11:0] xpos_vga_display, //输入横坐标 16 input [11:0] ypos_vga_display, //输入纵坐标 17 18 output reg [15:0] data_vga_display //输出产生的图像数据 19 ); 20 21 /**************************************************************** 22 定义本地参数颜色,RGB565 23 ****************************************************************/ 24 localparam 25 RED = 16‘hF800, //11111_000000_00000 红 26 GREEN = 16‘h07E0, //00000_111111_00000 绿 27 BLUE = 16‘h001F, //00000_000000_11111 蓝 28 WHITE = 16‘hFFFF, //11111_111111_11111 白 29 BLACK = 16‘h0000, //00000_000000_00000 黑 30 YELLOW = 16‘hFFE0, //11111_111111_00000 黄 31 MAGENTA= 16‘hF81F, //11111_000000_11111 紫(品红、洋红) 32 CYAN = 16‘h07FF; //00000_111111_11111 青(蓝绿) 33 34 /**************************************************************** 35 延时,产生模式选择信号 36 ****************************************************************/ 37 reg [27:0] cnt_display; //在像素频率下计数,计满为1秒 38 reg [2:0] mod_display; //显示模式 39 reg [4:0] delay_display; //延时,秒为单位,最多31秒 40 always @ (posedge clk_vga_display or negedge rst_n_display) 41 begin 42 if (!rst_n_display) 43 begin 44 cnt_display <= 28‘d0; 45 mod_display <= 3‘d0; 46 end 47 else 48 begin 49 if (cnt_display < PIXEL_FREQUENCY) //判断是否计到1秒 50 begin 51 if (delay_display < DELAY) //延时 DELAY 秒 52 delay_display <= delay_display + 5‘d1; 53 else 54 begin 55 if (mod_display < 3‘d7) //模式选择 56 mod_display <= mod_display + 3‘d1; 57 else 58 begin 59 mod_display <= 3‘d0; 60 end 61 delay_display <= 5‘d0; 62 end 63 cnt_display <= cnt_display + 28‘d1; 64 end 65 else 66 cnt_display <= 28‘d0; 67 end 68 end 69 70 /************************************************************* 71 方格1 小 72 *************************************************************/ 73 reg [15:0] grid1_data_display; 74 always @ (posedge clk_vga_display or negedge rst_n_display) 75 if (!rst_n_display) 76 grid1_data_display <= BLACK; 77 else 78 if (xpos_vga_display[4] == 1 ^ ypos_vga_display[4] == 1) 79 grid1_data_display <= WHITE; 80 else 81 grid1_data_display <= BLACK; 82 83 /************************************************************* 84 方格2 大 85 *************************************************************/ 86 reg [15:0] grid2_data_display; 87 always @ (posedge clk_vga_display or negedge rst_n_display) 88 if (!rst_n_display) 89 grid2_data_display <= BLACK; 90 else 91 if (xpos_vga_display[6] == 1 ^ ypos_vga_display[6] == 1) 92 grid2_data_display <= WHITE; 93 else 94 grid2_data_display <= BLACK; 95 96 /************************************************************* 97 彩条1 横 98 *************************************************************/ 99 reg [15:0] color_bar1_display; 100 always @ (posedge clk_vga_display or negedge rst_n_display) 101 if (!rst_n_display) 102 color_bar1_display <= BLACK; 103 else 104 begin 105 if (ypos_vga_display >= 0 && ypos_vga_display < (V_DISP >> 3)) 106 color_bar1_display <= RED; 107 else if (ypos_vga_display >= (V_DISP >> 3)*1 && ypos_vga_display < (V_DISP >> 3)*2) 108 color_bar1_display <= GREEN; 109 else if (ypos_vga_display >= (V_DISP >> 3)*2 && ypos_vga_display < (V_DISP >> 3)*3) 110 color_bar1_display <= BLUE; 111 else if (ypos_vga_display >= (V_DISP >> 3)*3 && ypos_vga_display < (V_DISP >> 3)*4) 112 color_bar1_display <= WHITE; 113 else if (ypos_vga_display >= (V_DISP >> 3)*4 && ypos_vga_display < (V_DISP >> 3)*5) 114 color_bar1_display <= BLACK; 115 else if (ypos_vga_display >= (V_DISP >> 3)*5 && ypos_vga_display < (V_DISP >> 3)*6) 116 color_bar1_display <= YELLOW; 117 else if (ypos_vga_display >= (V_DISP >> 3)*6 && ypos_vga_display < (V_DISP >> 3)*7) 118 color_bar1_display <= MAGENTA; 119 else if (ypos_vga_display >= (V_DISP >> 3)*7 && ypos_vga_display < (V_DISP >> 3)*8) 120 color_bar1_display <= CYAN; 121 else 122 color_bar1_display <= BLACK; 123 end 124 125 /************************************************************* 126 彩条2 竖 127 *************************************************************/ 128 reg [15:0] color_bar2_display; 129 always @ (posedge clk_vga_display or negedge rst_n_display) 130 if (!rst_n_display) 131 color_bar2_display <= BLACK; 132 else 133 begin 134 if (xpos_vga_display >= 0 && xpos_vga_display < (H_DISP >> 3)) 135 color_bar2_display <= RED; 136 else if (xpos_vga_display >= (H_DISP >> 3)*1 && xpos_vga_display < (H_DISP >> 3)*2) 137 color_bar2_display <= GREEN; 138 else if (xpos_vga_display >= (H_DISP >> 3)*2 && xpos_vga_display < (H_DISP >> 3)*3) 139 color_bar2_display <= BLUE; 140 else if (xpos_vga_display >= (H_DISP >> 3)*3 && xpos_vga_display < (H_DISP >> 3)*4) 141 color_bar2_display <= WHITE; 142 else if (xpos_vga_display >= (H_DISP >> 3)*4 && xpos_vga_display < (H_DISP >> 3)*5) 143 color_bar2_display <= BLACK; 144 else if (xpos_vga_display >= (H_DISP >> 3)*5 && xpos_vga_display < (H_DISP >> 3)*6) 145 color_bar2_display <= YELLOW; 146 else if (xpos_vga_display >= (H_DISP >> 3)*6 && xpos_vga_display < (H_DISP >> 3)*7) 147 color_bar2_display <= MAGENTA; 148 else if (xpos_vga_display >= (H_DISP >> 3)*7 && xpos_vga_display < (H_DISP >> 3)*8) 149 color_bar2_display <= CYAN; 150 else 151 color_bar2_display <= BLACK; 152 end 153 154 /************************************************************* 155 花型矩阵 156 **************************************************************/ 157 reg [15:0] flower_matrix_display; 158 wire [21:0] flower_result = xpos_vga_display * ypos_vga_display; 159 always @ (posedge clk_vga_display or negedge rst_n_display) 160 if (!rst_n_display) 161 flower_matrix_display <= BLACK; 162 else 163 flower_matrix_display <= flower_result[15:0]; 164 165 /************************************************************* 166 选择显示模式 167 *************************************************************/ 168 always @ (posedge clk_vga_display or negedge rst_n_display) 169 if (!rst_n_display) 170 data_vga_display <= 16‘d0; 171 else 172 case (mod_display) 173 3‘d0 : data_vga_display <= grid1_data_display; 174 3‘d1 : data_vga_display <= grid2_data_display; 175 3‘d2 : data_vga_display <= color_bar1_display; 176 3‘d3 : data_vga_display <= color_bar2_display; 177 3‘d4 : data_vga_display <= RED; 178 3‘d5 : data_vga_display <= GREEN; 179 3‘d6 : data_vga_display <= BLUE; 180 3‘d7 : data_vga_display <= flower_matrix_display; 181 default : data_vga_display <= BLACK; 182 endcase 183 184 endmodule 185

1 // megafunction wizard: %ALTPLL% 2 // GENERATION: STANDARD 3 // VERSION: WM1.0 4 // MODULE: altpll 5 6 // ============================================================ 7 // File Name: clk_pll.v 8 // Megafunction Name(s): 9 // altpll 10 // 11 // Simulation Library Files(s): 12 // altera_mf 13 // ============================================================ 14 // ************************************************************ 15 // THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE! 16 // 17 // 12.1 Build 177 11/07/2012 SJ Full Version 18 // ************************************************************ 19 20 21 //Copyright (C) 1991-2012 Altera Corporation 22 //Your use of Altera Corporation‘s design tools, logic functions 23 //and other software and tools, and its AMPP partner logic 24 //functions, and any output files from any of the foregoing 25 //(including device programming or simulation files), and any 26 //associated documentation or information are expressly subject 27 //to the terms and conditions of the Altera Program License 28 //Subscription Agreement, Altera MegaCore Function License 29 //Agreement, or other applicable license agreement, including, 30 //without limitation, that your use is for the sole purpose of 31 //programming logic devices manufactured by Altera and sold by 32 //Altera or its authorized distributors. Please refer to the 33 //applicable agreement for further details. 34 35 36 // synopsys translate_off 37 `timescale 1 ps / 1 ps 38 // synopsys translate_on 39 module clk_pll #( 40 parameter //提取参数,方便例化时参数传递 41 DUTY_CYCLE = 50, 42 DIVIDE_DATA = 25, 43 MULTIPLY_DATA = 54 44 ) 45 ( 46 inclk0, 47 c0 48 ); 49 50 input inclk0; 51 output c0; 52 53 wire [4:0] sub_wire0; 54 wire [0:0] sub_wire4 = 1‘h0; 55 wire [0:0] sub_wire1 = sub_wire0[0:0]; 56 wire c0 = sub_wire1; 57 wire sub_wire2 = inclk0; 58 wire [1:0] sub_wire3 = {sub_wire4, sub_wire2}; 59 60 altpll altpll_component ( 61 .inclk (sub_wire3), 62 .clk (sub_wire0), 63 .activeclock (), 64 .areset (1‘b0), 65 .clkbad (), 66 .clkena ({6{1‘b1}}), 67 .clkloss (), 68 .clkswitch (1‘b0), 69 .configupdate (1‘b0), 70 .enable0 (), 71 .enable1 (), 72 .extclk (), 73 .extclkena ({4{1‘b1}}), 74 .fbin (1‘b1), 75 .fbmimicbidir (), 76 .fbout (), 77 .fref (), 78 .icdrclk (), 79 .locked (), 80 .pfdena (1‘b1), 81 .phasecounterselect ({4{1‘b1}}), 82 .phasedone (), 83 .phasestep (1‘b1), 84 .phaseupdown (1‘b1), 85 .pllena (1‘b1), 86 .scanaclr (1‘b0), 87 .scanclk (1‘b0), 88 .scanclkena (1‘b1), 89 .scandata (1‘b0), 90 .scandataout (), 91 .scandone (), 92 .scanread (1‘b0), 93 .scanwrite (1‘b0), 94 .sclkout0 (), 95 .sclkout1 (), 96 .vcooverrange (), 97 .vcounderrange ()); 98 defparam 99 altpll_component.bandwidth_type = "AUTO", 100 altpll_component.clk0_divide_by = DIVIDE_DATA, 101 altpll_component.clk0_duty_cycle = DUTY_CYCLE, 102 altpll_component.clk0_multiply_by = MULTIPLY_DATA, 103 altpll_component.clk0_phase_shift = "0", 104 altpll_component.compensate_clock = "CLK0", 105 altpll_component.inclk0_input_frequency = 20000, 106 altpll_component.intended_device_family = "Cyclone IV E", 107 altpll_component.lpm_hint = "CBX_MODULE_PREFIX=clk_pll", 108 altpll_component.lpm_type = "altpll", 109 altpll_component.operation_mode = "NORMAL", 110 altpll_component.pll_type = "AUTO", 111 altpll_component.port_activeclock = "PORT_UNUSED", 112 altpll_component.port_areset = "PORT_UNUSED", 113 altpll_component.port_clkbad0 = "PORT_UNUSED", 114 altpll_component.port_clkbad1 = "PORT_UNUSED", 115 altpll_component.port_clkloss = "PORT_UNUSED", 116 altpll_component.port_clkswitch = "PORT_UNUSED", 117 altpll_component.port_configupdate = "PORT_UNUSED", 118 altpll_component.port_fbin = "PORT_UNUSED", 119 altpll_component.port_inclk0 = "PORT_USED", 120 altpll_component.port_inclk1 = "PORT_UNUSED", 121 altpll_component.port_locked = "PORT_UNUSED", 122 altpll_component.port_pfdena = "PORT_UNUSED", 123 altpll_component.port_phasecounterselect = "PORT_UNUSED", 124 altpll_component.port_phasedone = "PORT_UNUSED", 125 altpll_component.port_phasestep = "PORT_UNUSED", 126 altpll_component.port_phaseupdown = "PORT_UNUSED", 127 altpll_component.port_pllena = "PORT_UNUSED", 128 altpll_component.port_scanaclr = "PORT_UNUSED", 129 altpll_component.port_scanclk = "PORT_UNUSED", 130 altpll_component.port_scanclkena = "PORT_UNUSED", 131 altpll_component.port_scandata = "PORT_UNUSED", 132 altpll_component.port_scandataout = "PORT_UNUSED", 133 altpll_component.port_scandone = "PORT_UNUSED", 134 altpll_component.port_scanread = "PORT_UNUSED", 135 altpll_component.port_scanwrite = "PORT_UNUSED", 136 altpll_component.port_clk0 = "PORT_USED", 137 altpll_component.port_clk1 = "PORT_UNUSED", 138 altpll_component.port_clk2 = "PORT_UNUSED", 139 altpll_component.port_clk3 = "PORT_UNUSED", 140 altpll_component.port_clk4 = "PORT_UNUSED", 141 altpll_component.port_clk5 = "PORT_UNUSED", 142 altpll_component.port_clkena0 = "PORT_UNUSED", 143 altpll_component.port_clkena1 = "PORT_UNUSED", 144 altpll_component.port_clkena2 = "PORT_UNUSED", 145 altpll_component.port_clkena3 = "PORT_UNUSED", 146 altpll_component.port_clkena4 = "PORT_UNUSED", 147 altpll_component.port_clkena5 = "PORT_UNUSED", 148 altpll_component.port_extclk0 = "PORT_UNUSED", 149 altpll_component.port_extclk1 = "PORT_UNUSED", 150 altpll_component.port_extclk2 = "PORT_UNUSED", 151 altpll_component.port_extclk3 = "PORT_UNUSED", 152 altpll_component.width_clock = 5; 153 154 155 endmodule 156 157 // ============================================================ 158 // CNX file retrieval info 159 // ============================================================ 160 // Retrieval info: PRIVATE: ACTIVECLK_CHECK STRING "0" 161 // Retrieval info: PRIVATE: BANDWIDTH STRING "1.000" 162 // Retrieval info: PRIVATE: BANDWIDTH_FEATURE_ENABLED STRING "1" 163 // Retrieval info: PRIVATE: BANDWIDTH_FREQ_UNIT STRING "MHz" 164 // Retrieval info: PRIVATE: BANDWIDTH_PRESET STRING "Low" 165 // Retrieval info: PRIVATE: BANDWIDTH_USE_AUTO STRING "1" 166 // Retrieval info: PRIVATE: BANDWIDTH_USE_PRESET STRING "0" 167 // Retrieval info: PRIVATE: CLKBAD_SWITCHOVER_CHECK STRING "0" 168 // Retrieval info: PRIVATE: CLKLOSS_CHECK STRING "0" 169 // Retrieval info: PRIVATE: CLKSWITCH_CHECK STRING "0" 170 // Retrieval info: PRIVATE: CNX_NO_COMPENSATE_RADIO STRING "0" 171 // Retrieval info: PRIVATE: CREATE_CLKBAD_CHECK STRING "0" 172 // Retrieval info: PRIVATE: CREATE_INCLK1_CHECK STRING "0" 173 // Retrieval info: PRIVATE: CUR_DEDICATED_CLK STRING "c0" 174 // Retrieval info: PRIVATE: CUR_FBIN_CLK STRING "c0" 175 // Retrieval info: PRIVATE: DEVICE_SPEED_GRADE STRING "8" 176 // Retrieval info: PRIVATE: DIV_FACTOR0 NUMERIC "1" 177 // Retrieval info: PRIVATE: DUTY_CYCLE0 STRING "50.00000000" 178 // Retrieval info: PRIVATE: EFF_OUTPUT_FREQ_VALUE0 STRING "108.000000" 179 // Retrieval info: PRIVATE: EXPLICIT_SWITCHOVER_COUNTER STRING "0" 180 // Retrieval info: PRIVATE: EXT_FEEDBACK_RADIO STRING "0" 181 // Retrieval info: PRIVATE: GLOCKED_COUNTER_EDIT_CHANGED STRING "1" 182 // Retrieval info: PRIVATE: GLOCKED_FEATURE_ENABLED STRING "0" 183 // Retrieval info: PRIVATE: GLOCKED_MODE_CHECK STRING "0" 184 // Retrieval info: PRIVATE: GLOCK_COUNTER_EDIT NUMERIC "1048575" 185 // Retrieval info: PRIVATE: HAS_MANUAL_SWITCHOVER STRING "1" 186 // Retrieval info: PRIVATE: INCLK0_FREQ_EDIT STRING "50.000" 187 // Retrieval info: PRIVATE: INCLK0_FREQ_UNIT_COMBO STRING "MHz" 188 // Retrieval info: PRIVATE: INCLK1_FREQ_EDIT STRING "100.000" 189 // Retrieval info: PRIVATE: INCLK1_FREQ_EDIT_CHANGED STRING "1" 190 // Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_CHANGED STRING "1" 191 // Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_COMBO STRING "MHz" 192 // Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone IV E" 193 // Retrieval info: PRIVATE: INT_FEEDBACK__MODE_RADIO STRING "1" 194 // Retrieval info: PRIVATE: LOCKED_OUTPUT_CHECK STRING "0" 195 // Retrieval info: PRIVATE: LONG_SCAN_RADIO STRING "1" 196 // Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE STRING "Not Available" 197 // Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE_DIRTY NUMERIC "0" 198 // Retrieval info: PRIVATE: LVDS_PHASE_SHIFT_UNIT0 STRING "deg" 199 // Retrieval info: PRIVATE: MIG_DEVICE_SPEED_GRADE STRING "Any" 200 // Retrieval info: PRIVATE: MIRROR_CLK0 STRING "0" 201 // Retrieval info: PRIVATE: MULT_FACTOR0 NUMERIC "1" 202 // Retrieval info: PRIVATE: NORMAL_MODE_RADIO STRING "1" 203 // Retrieval info: PRIVATE: OUTPUT_FREQ0 STRING "108.00000000" 204 // Retrieval info: PRIVATE: OUTPUT_FREQ_MODE0 STRING "1" 205 // Retrieval info: PRIVATE: OUTPUT_FREQ_UNIT0 STRING "MHz" 206 // Retrieval info: PRIVATE: PHASE_RECONFIG_FEATURE_ENABLED STRING "1" 207 // Retrieval info: PRIVATE: PHASE_RECONFIG_INPUTS_CHECK STRING "0" 208 // Retrieval info: PRIVATE: PHASE_SHIFT0 STRING "0.00000000" 209 // Retrieval info: PRIVATE: PHASE_SHIFT_STEP_ENABLED_CHECK STRING "0" 210 // Retrieval info: PRIVATE: PHASE_SHIFT_UNIT0 STRING "deg" 211 // Retrieval info: PRIVATE: PLL_ADVANCED_PARAM_CHECK STRING "0" 212 // Retrieval info: PRIVATE: PLL_ARESET_CHECK STRING "0" 213 // Retrieval info: PRIVATE: PLL_AUTOPLL_CHECK NUMERIC "1" 214 // Retrieval info: PRIVATE: PLL_ENHPLL_CHECK NUMERIC "0" 215 // Retrieval info: PRIVATE: PLL_FASTPLL_CHECK NUMERIC "0" 216 // Retrieval info: PRIVATE: PLL_FBMIMIC_CHECK STRING "0" 217 // Retrieval info: PRIVATE: PLL_LVDS_PLL_CHECK NUMERIC "0" 218 // Retrieval info: PRIVATE: PLL_PFDENA_CHECK STRING "0" 219 // Retrieval info: PRIVATE: PLL_TARGET_HARCOPY_CHECK NUMERIC "0" 220 // Retrieval info: PRIVATE: PRIMARY_CLK_COMBO STRING "inclk0" 221 // Retrieval info: PRIVATE: RECONFIG_FILE STRING "clk_pll.mif" 222 // Retrieval info: PRIVATE: SACN_INPUTS_CHECK STRING "0" 223 // Retrieval info: PRIVATE: SCAN_FEATURE_ENABLED STRING "1" 224 // Retrieval info: PRIVATE: SELF_RESET_LOCK_LOSS STRING "0" 225 // Retrieval info: PRIVATE: SHORT_SCAN_RADIO STRING "0" 226 // Retrieval info: PRIVATE: SPREAD_FEATURE_ENABLED STRING "0" 227 // Retrieval info: PRIVATE: SPREAD_FREQ STRING "50.000" 228 // Retrieval info: PRIVATE: SPREAD_FREQ_UNIT STRING "KHz" 229 // Retrieval info: PRIVATE: SPREAD_PERCENT STRING "0.500" 230 // Retrieval info: PRIVATE: SPREAD_USE STRING "0" 231 // Retrieval info: PRIVATE: SRC_SYNCH_COMP_RADIO STRING "0" 232 // Retrieval info: PRIVATE: STICKY_CLK0 STRING "1" 233 // Retrieval info: PRIVATE: SWITCHOVER_COUNT_EDIT NUMERIC "1" 234 // Retrieval info: PRIVATE: SWITCHOVER_FEATURE_ENABLED STRING "1" 235 // Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0" 236 // Retrieval info: PRIVATE: USE_CLK0 STRING "1" 237 // Retrieval info: PRIVATE: USE_CLKENA0 STRING "0" 238 // Retrieval info: PRIVATE: USE_MIL_SPEED_GRADE NUMERIC "0" 239 // Retrieval info: PRIVATE: ZERO_DELAY_RADIO STRING "0" 240 // Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all 241 // Retrieval info: CONSTANT: BANDWIDTH_TYPE STRING "AUTO" 242 // Retrieval info: CONSTANT: CLK0_DIVIDE_BY NUMERIC "25" 243 // Retrieval info: CONSTANT: CLK0_DUTY_CYCLE NUMERIC "50" 244 // Retrieval info: CONSTANT: CLK0_MULTIPLY_BY NUMERIC "54" 245 // Retrieval info: CONSTANT: CLK0_PHASE_SHIFT STRING "0" 246 // Retrieval info: CONSTANT: COMPENSATE_CLOCK STRING "CLK0" 247 // Retrieval info: CONSTANT: INCLK0_INPUT_FREQUENCY NUMERIC "20000" 248 // Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone IV E" 249 // Retrieval info: CONSTANT: LPM_TYPE STRING "altpll" 250 // Retrieval info: CONSTANT: OPERATION_MODE STRING "NORMAL" 251 // Retrieval info: CONSTANT: PLL_TYPE STRING "AUTO" 252 // Retrieval info: CONSTANT: PORT_ACTIVECLOCK STRING "PORT_UNUSED" 253 // Retrieval info: CONSTANT: PORT_ARESET STRING "PORT_UNUSED" 254 // Retrieval info: CONSTANT: PORT_CLKBAD0 STRING "PORT_UNUSED" 255 // Retrieval info: CONSTANT: PORT_CLKBAD1 STRING "PORT_UNUSED" 256 // Retrieval info: CONSTANT: PORT_CLKLOSS STRING "PORT_UNUSED" 257 // Retrieval info: CONSTANT: PORT_CLKSWITCH STRING "PORT_UNUSED" 258 // Retrieval info: CONSTANT: PORT_CONFIGUPDATE STRING "PORT_UNUSED" 259 // Retrieval info: CONSTANT: PORT_FBIN STRING "PORT_UNUSED" 260 // Retrieval info: CONSTANT: PORT_INCLK0 STRING "PORT_USED" 261 // Retrieval info: CONSTANT: PORT_INCLK1 STRING "PORT_UNUSED" 262 // Retrieval info: CONSTANT: PORT_LOCKED STRING "PORT_UNUSED" 263 // Retrieval info: CONSTANT: PORT_PFDENA STRING "PORT_UNUSED" 264 // Retrieval info: CONSTANT: PORT_PHASECOUNTERSELECT STRING "PORT_UNUSED" 265 // Retrieval info: CONSTANT: PORT_PHASEDONE STRING "PORT_UNUSED" 266 // Retrieval info: CONSTANT: PORT_PHASESTEP STRING "PORT_UNUSED" 267 // Retrieval info: CONSTANT: PORT_PHASEUPDOWN STRING "PORT_UNUSED" 268 // Retrieval info: CONSTANT: PORT_PLLENA STRING "PORT_UNUSED" 269 // Retrieval info: CONSTANT: PORT_SCANACLR STRING "PORT_UNUSED" 270 // Retrieval info: CONSTANT: PORT_SCANCLK STRING "PORT_UNUSED" 271 // Retrieval info: CONSTANT: PORT_SCANCLKENA STRING "PORT_UNUSED" 272 // Retrieval info: CONSTANT: PORT_SCANDATA STRING "PORT_UNUSED" 273 // Retrieval info: CONSTANT: PORT_SCANDATAOUT STRING "PORT_UNUSED" 274 // Retrieval info: CONSTANT: PORT_SCANDONE STRING "PORT_UNUSED" 275 // Retrieval info: CONSTANT: PORT_SCANREAD STRING "PORT_UNUSED" 276 // Retrieval info: CONSTANT: PORT_SCANWRITE STRING "PORT_UNUSED" 277 // Retrieval info: CONSTANT: PORT_clk0 STRING "PORT_USED" 278 // Retrieval info: CONSTANT: PORT_clk1 STRING "PORT_UNUSED" 279 // Retrieval info: CONSTANT: PORT_clk2 STRING "PORT_UNUSED" 280 // Retrieval info: CONSTANT: PORT_clk3 STRING "PORT_UNUSED" 281 // Retrieval info: CONSTANT: PORT_clk4 STRING "PORT_UNUSED" 282 // Retrieval info: CONSTANT: PORT_clk5 STRING "PORT_UNUSED" 283 // Retrieval info: CONSTANT: PORT_clkena0 STRING "PORT_UNUSED" 284 // Retrieval info: CONSTANT: PORT_clkena1 STRING "PORT_UNUSED" 285 // Retrieval info: CONSTANT: PORT_clkena2 STRING "PORT_UNUSED" 286 // Retrieval info: CONSTANT: PORT_clkena3 STRING "PORT_UNUSED" 287 // Retrieval info: CONSTANT: PORT_clkena4 STRING "PORT_UNUSED" 288 // Retrieval info: CONSTANT: PORT_clkena5 STRING "PORT_UNUSED" 289 // Retrieval info: CONSTANT: PORT_extclk0 STRING "PORT_UNUSED" 290 // Retrieval info: CONSTANT: PORT_extclk1 STRING "PORT_UNUSED" 291 // Retrieval info: CONSTANT: PORT_extclk2 STRING "PORT_UNUSED" 292 // Retrieval info: CONSTANT: PORT_extclk3 STRING "PORT_UNUSED" 293 // Retrieval info: CONSTANT: WIDTH_CLOCK NUMERIC "5" 294 // Retrieval info: USED_PORT: @clk 0 0 5 0 OUTPUT_CLK_EXT VCC "@clk[4..0]" 295 // Retrieval info: USED_PORT: c0 0 0 0 0 OUTPUT_CLK_EXT VCC "c0" 296 // Retrieval info: USED_PORT: inclk0 0 0 0 0 INPUT_CLK_EXT GND "inclk0" 297 // Retrieval info: CONNECT: @inclk 0 0 1 1 GND 0 0 0 0 298 // Retrieval info: CONNECT: @inclk 0 0 1 0 inclk0 0 0 0 0 299 // Retrieval info: CONNECT: c0 0 0 0 0 @clk 0 0 1 0 300 // Retrieval info: GEN_FILE: TYPE_NORMAL clk_pll.v TRUE 301 // Retrieval info: GEN_FILE: TYPE_NORMAL clk_pll.ppf TRUE 302 // Retrieval info: GEN_FILE: TYPE_NORMAL clk_pll.inc TRUE 303 // Retrieval info: GEN_FILE: TYPE_NORMAL clk_pll.cmp TRUE 304 // Retrieval info: GEN_FILE: TYPE_NORMAL clk_pll.bsf TRUE 305 // Retrieval info: GEN_FILE: TYPE_NORMAL clk_pll_inst.v TRUE 306 // Retrieval info: GEN_FILE: TYPE_NORMAL clk_pll_bb.v TRUE 307 // Retrieval info: LIB_FILE: altera_mf 308 // Retrieval info: CBX_MODULE_PREFIX: ON

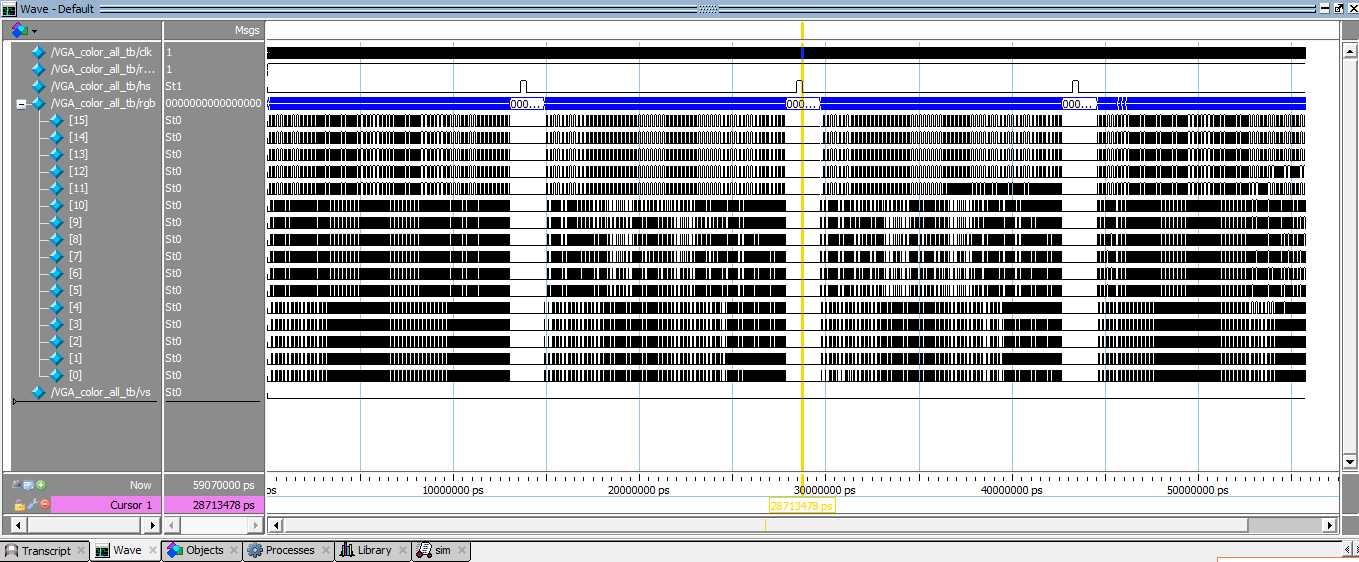

1 `timescale 10 ns/ 1 ps 2 module VGA_color_all_tb(); 3 reg clk; 4 reg rst_n; 5 // wires 6 wire hs; 7 wire [15:0] rgb; 8 wire vs; 9 10 // assign statements (if any) 11 VGA_color_all i1 ( 12 // port map - connection between master ports and signals/registers 13 .clk(clk), 14 .hs(hs), 15 .rgb(rgb), 16 .rst_n(rst_n), 17 .vs(vs) 18 ); 19 initial 20 begin 21 clk = 0; 22 rst_n = 1; 23 #2 rst_n = 0; 24 #2 rst_n = 1; 25 end 26 always 27 begin 28 #1 clk = ~clk; 29 end 30 endmodule

如有错误还请指出,如有侵权还请告知,如需转载请注明出处!

本人博客:http://www.cnblogs.com/yllinux/

标签:nop tcl gen ifd pix int define val standard

原文地址:http://www.cnblogs.com/yllinux/p/7256523.html