标签:需要 verify 验证 输入 擦除 alt www. 还需要 还需

注明来自 http://www.ssdfans.com/?p=5589

以MLC为例:

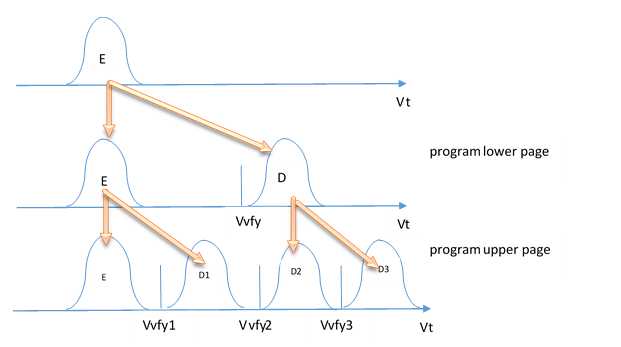

对FGF(Floating Gate Flash)技术的,MLC programming一般分两步走:先program Lower page,然后program Upper Page。

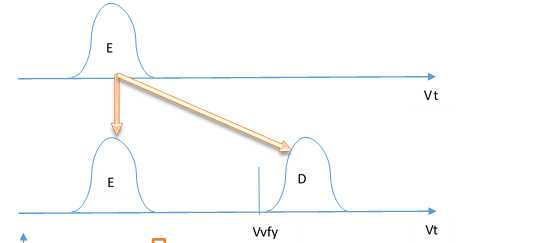

对某个Cell来说,当写入1时,无需Programming,阈值电压保持不变,还是处于E状态;当写入0时,必须进行Programming,使它的阈值电压落到D范围 ,即E->D。

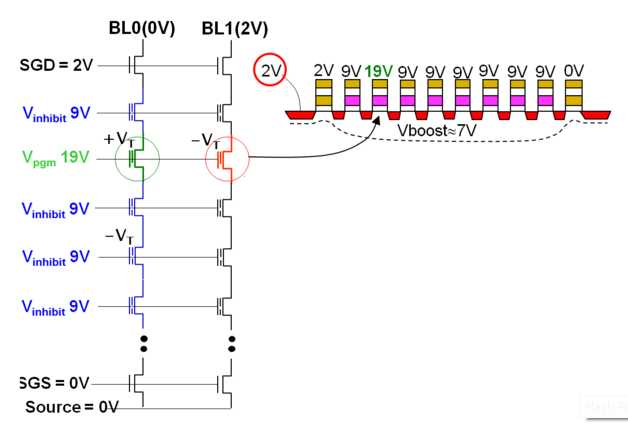

Programming某个page时,往其所在的WL控制极上施加高电平,衬底接地,对需要Programming的存储单元(如上图绿色圈起来的cell):1->0,其bitline接地;对不需要Programming的存储单元(如上图红色圈起来的cell):1->1,bitline拉高,就能抑制其Programming。

由于每个存储单元的体质不一样,有些cell很快就能让其阈值电压跳到D范围,而有些存储单元需要若干次Programming,才能使其到达D。flash采用Program + Verify的方式进行Programming,即开始在WL控制极上施加一个电压,如上图所示,假设Vpgm =19V,让这个电压持续一段时间,然后撤掉,对每个Programming的存储单元进行验证,看其阈值电压是否超过验证电压Vvfy,如果超过,说明达到D状态,这些存储单元的bitline从接地到拉高,让其不再继续Programming,而对那些没有达到D状态的存储单元,还需要继续Programming。Vpgm会加大,比如增加0.5V,Vpgm = 19.5V,继续Programming,verify,直到达到D状态。

在Programming upper page之前,flash需要读取该Page,获取page中所有cell的当前状态,然后根据输入,Programming cell到相应的目标状态。

如果当前cell状态处于E,如果写入1,无需Programming,E状态保持不变;如果写入0,则需要Programming该cell到状态D1; 如果当前cell状态处于D,如果写入1,program该cell到D2;如果写入0,则需要Programming该cell到状态D3;

比较一下lower page programming和upper page programming,有以下几个不同:

1.Program upper page时,需先知道当前cell的状态,在programming之前需要读所有的cells; Program lower page时候无需此操作,因为所有cell都处于擦除状态;

2.Program upper page时,需要verify好几个电平,而program lower page时,只需verify一个电平;

3.Program lower page时,E状态和D状态可以隔得比较远,因此program时候可以加更大的初始program电压和更大的步进(step)电压;而Program Upper page时,E,D1,D2,D3之间的间隔比较小,因此program需要更精细的控制电压,不然一下program过头了。比如本来期望从E状态跳跃到D1状态,不小心电压加大了,直接就跳到D2,那就麻烦了。

分两次写最大的问题是,如果在programming upper page时发生异常掉电,那么之前Lower page的数据也丢失。

标签:需要 verify 验证 输入 擦除 alt www. 还需要 还需

原文地址:http://www.cnblogs.com/Caden-liu8888/p/7366774.html