标签:always 基于 mod 技术 es2017 verilog 基本 技术分享 2.3

任务安排:基于Cyclone IV的基本代码编写及硬件实现;

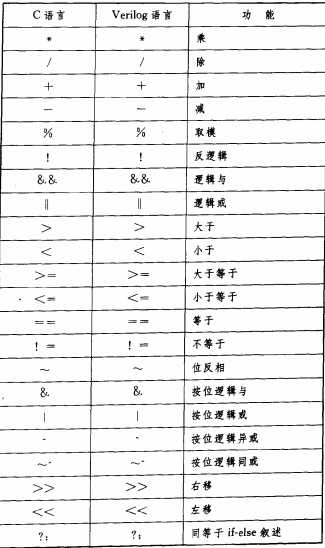

1:Verilog hdl的运算符

2.简单程序编写;(输入利用接口key,ckey,输出利用led可以直接观测到输出结果)

2.1与门

module ND(a,b,c); input a,b; output c; assign c=a&b; endmodule

2.2与非门

module NAND(a,b,c) input a,b; output c; assign c=~(a&b); endmodule

2.3二选一

module mux1_2(a,b,c,d); input a,b,sel; output d; assign d=sel?a:b; endmodule

2.4解码器

1 module decoder(I,enable,Y); 2 input [1:0] I; 3 input enable; 4 output [3:0] Y; 5 reg [3:0] Y; 6 7 always@(I,enable) 8 begin 9 if (enable) Y=4‘b1111; 10 else 11 case(I) 12 2‘b00: Y=4‘b1110; 13 2‘b01: Y=4‘b1101; 14 2‘b10: Y=4‘b1011; 15 2‘b11: Y=4‘b0111; 16 default: Y=4‘b1111; 17 endcase 18 end 19 endmodule

标签:always 基于 mod 技术 es2017 verilog 基本 技术分享 2.3

原文地址:http://www.cnblogs.com/assassinn/p/7440861.html