标签:数据流 read 但我 是你 视频解码 targe get 二进制 步骤

步骤1

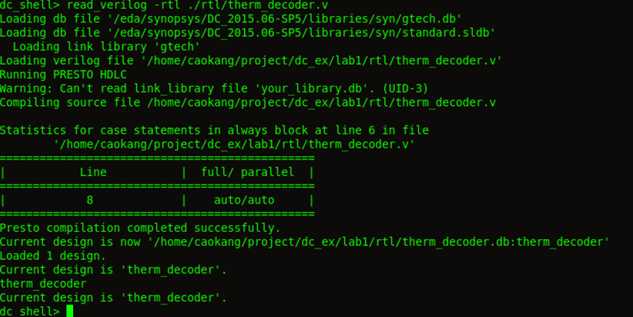

命令: read_verilog –rtl + 路径/文件名

结果: load gtech.db库、standard.sldb库。

Load .v文件

Load your_library,但我们这里没有指定,所以报出了Warning。

Compile .v文件,统计always ,不知道是干啥. 中间这些分析信息,现不看。

步骤2

Source 一把 scr约束文件。这个source到底是shell的还是tcl的?

步骤3

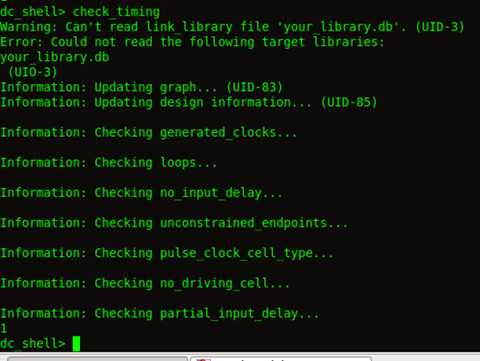

进行依次check_timing ,发现会报错。Erorr,找不到 your_library。 这个your_library是什么,是你想要映射的库。

比如umc0.11f 、 TSMC0.11库。所以我们得告诉DC,我们到底要用什么。

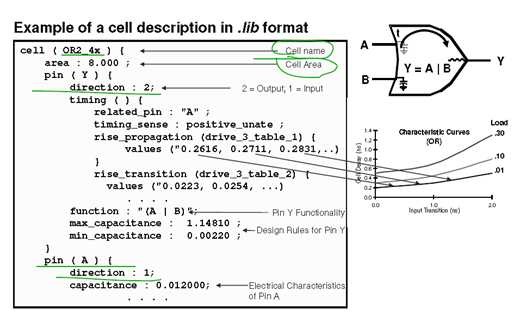

步骤4 : 这个库是什么?有什么信息?

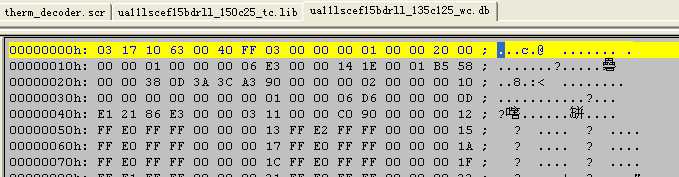

工艺厂提供这个文件: 主要有standcell、mem库两个。 文件格式是 .lib .我们用UE能打开.lib文件。

首先有各种的standcell的 名字、面积、时序、功能function、RC估计值。等等信息。因为它是 .lib可视化的文件,方便我们了设计师,

但却加重了DC工具的负担,因为.lib文件吃进入、不如二进制文件迅速。所以DC提供了内部的文件转化机制、把lib转为db文件。

这个文件,设计师是看不懂的,但是DC工具认识。就跟jpeg数据流一样,我们单独看不懂,但图片视频解码器看的懂,因为它内部有解码器。

转换过程: 详细参考library compile工具。(DC内嵌了)

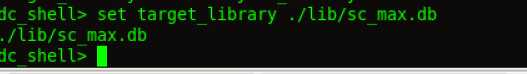

步骤5: 指定target_library

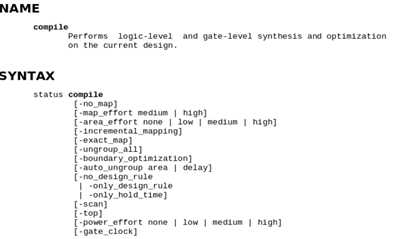

步骤6 : 进行compile

我们查了下compile的作用-----进行逻辑层、门级综合优化。其中带了一些option选项。可以先不管。

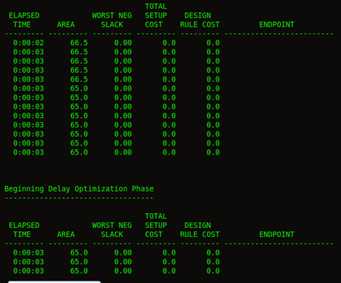

同时呢,echo除了一大堆的数据信息,这应该是综合信息。我们现在还不知道具体代表什么信息,可以先不管。

只要知道,这一步进行了综合就可以了先。

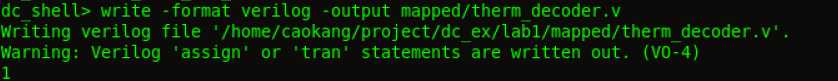

步骤7 保存结果

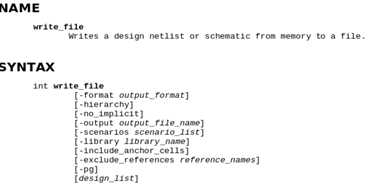

使用命令: write – format verilog –output 路径+名字 ,将综合结果保存起来。

我们可以使用 man write。 能得到相关选项的信息。

步骤8 Exit退出。

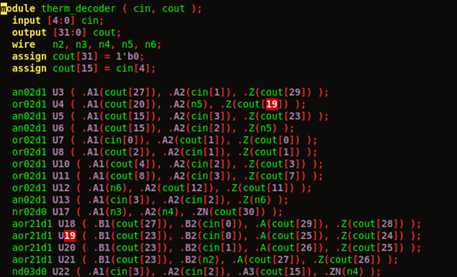

我们去mapped里面,可以去看下我们所保存的netlist.v文件。

标签:数据流 read 但我 是你 视频解码 targe get 二进制 步骤

原文地址:http://www.cnblogs.com/mokang0421/p/7582192.html