标签:ide evel tab sim tool str manager pll 时钟

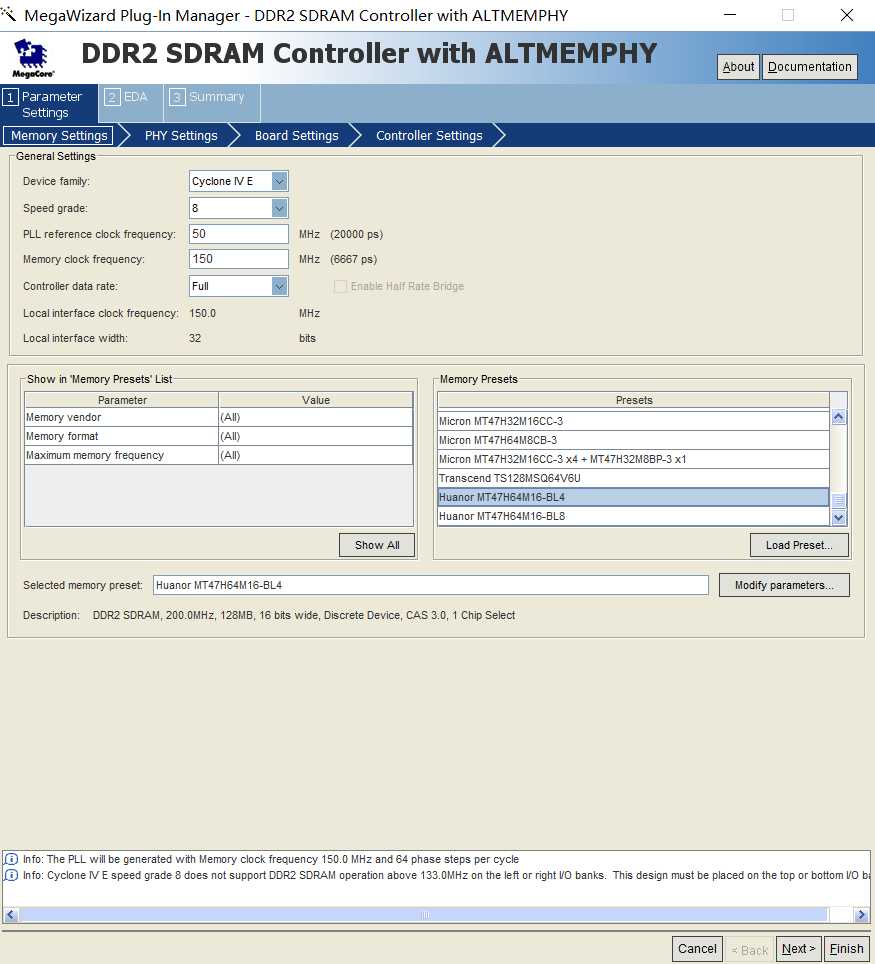

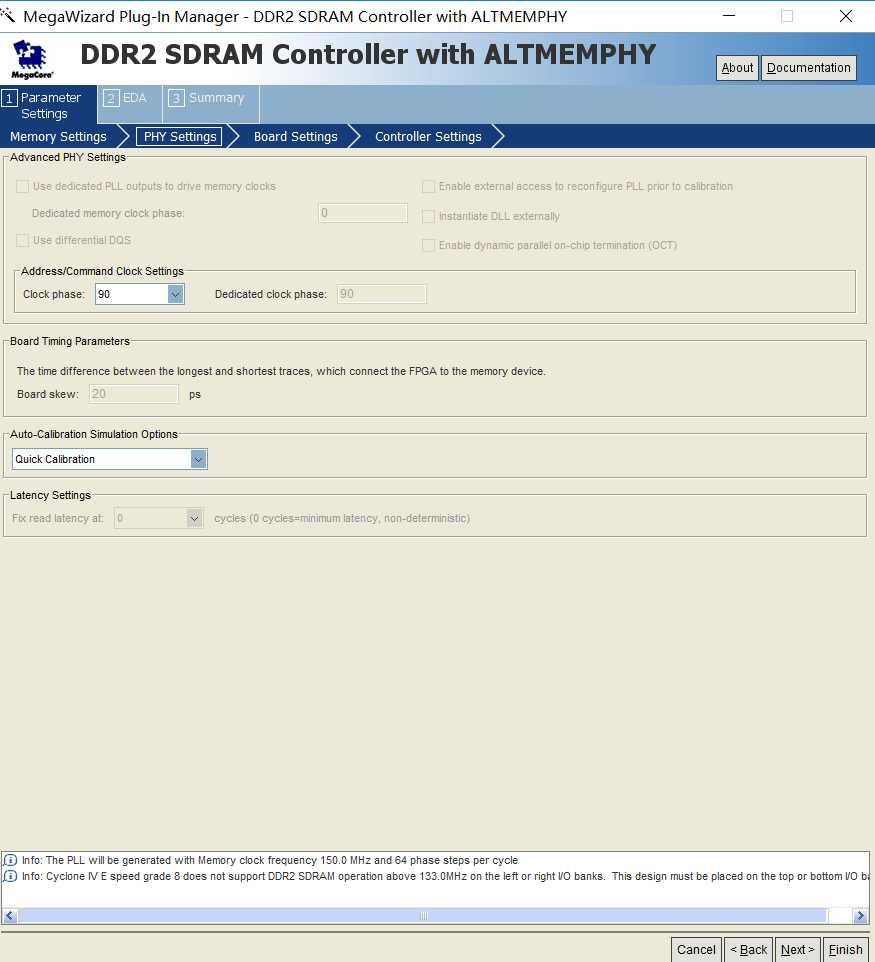

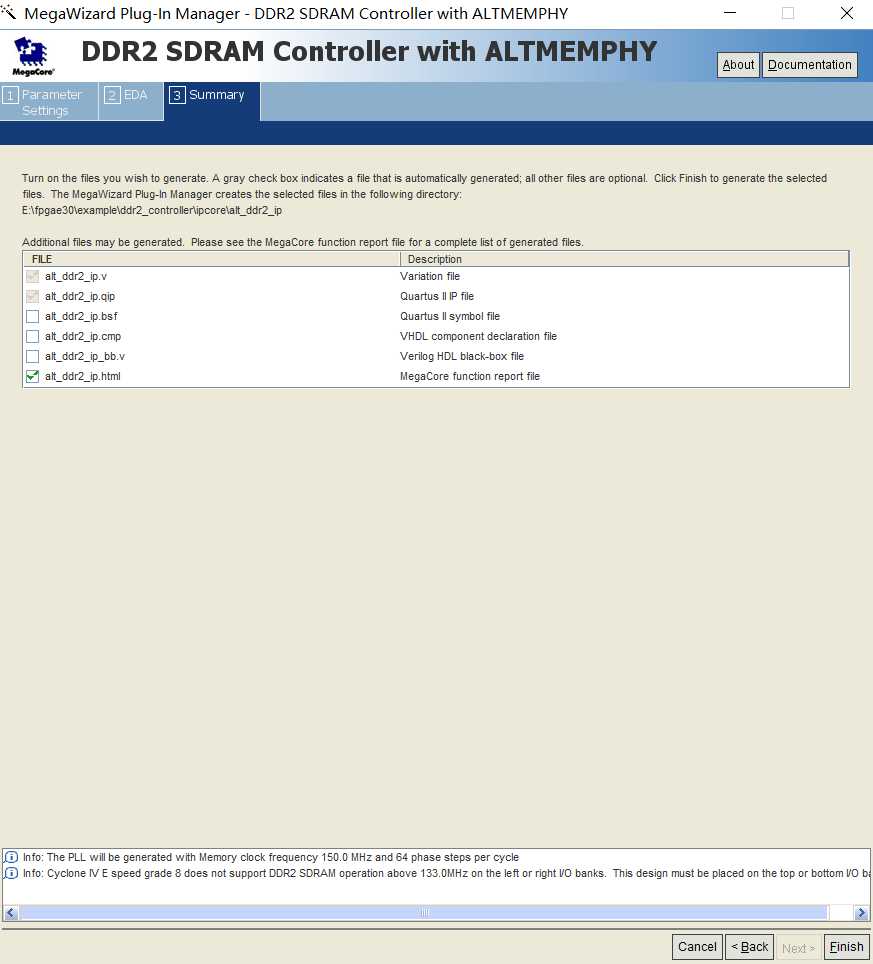

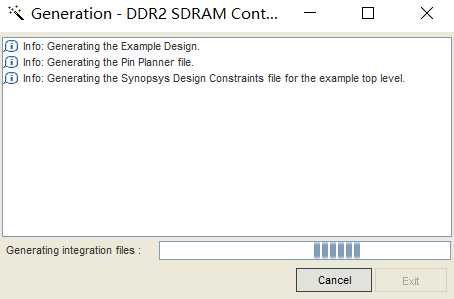

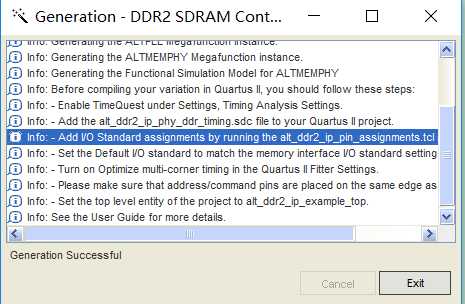

| Info: Generating the Example Design. Info: Generating the Pin Planner file. Info: Generating the Synopsys Design Constraints file for the example top level. Info: Generating the Synopsys Design Constraints file. Info: Generating the Timing Report script. Info: Generating the ALTPLL Megafunction instance. Info: Generating the ALTMEMPHY Megafunction instance. Info: Generating the Functional Simulation Model for ALTMEMPHY Info: Before compiling your variation in Quartus II, you should follow these steps: Info: - Enable TimeQuest under Settings, Timing Analysis Settings. Info: - Add the alt_ddr2_ip_phy_ddr_timing.sdc file to your Quartus II project. Info: - Add I/O Standard assignments by running the alt_ddr2_ip_pin_assignments.tcl script. Info: - Set the Default I/O standard to match the memory interface I/O standard setting. Info: - Turn on Optimize multi-corner timing in the Quartus II Fitter Settings. Info: - Please make sure that address/command pins are placed on the same edge as the CK/CK# pins. Info: - Set the top level entity of the project to alt_ddr2_ip_example_top. Info: See the User Guide for more details. |

标签:ide evel tab sim tool str manager pll 时钟

原文地址:http://www.cnblogs.com/xinlukk/p/7587670.html