标签:des style blog http color os io ar for

A computer system is described having one or more host processors, a host chipset and an input/output (I/O) subsystem. The host processors are connected to the host chipset by a host bus. The host chipset is connected to the input/output subsystem by a primary personal computer interface (PCI) bus. The I/O subsystem is connected to I/O devices by a secondary PCI bus. The I/O subsystem includes?advanced?programmable?interrupt?controller?(APIC) functionality typically provided within an I/O APIC chip within a host chipset. The APIC functionality of the I/O subsystem is primarily implemented in software executing on a core processor of the I/O subsystem. The software creates and accesses various APIC registers and tables, such as a redirection table, within a memory of the I/O subsystem. A single 3-wire APIC bus interconnects the host processors with the I/O subsystem. With this arrangement, non-PCI?interrupt?lines from the I/O devices are connected only into the I/O subsystem, rather than into the host chipset.

The invention generally relates to computer systems and in particular to computer systems incorporating a personal computer interface (PCI) bus, an input/output (I/O) subsystem and an input/output?advanced?programmable interrupt?controller?(APIC).

Many state of the art personal computer systems employ one or more PCI buses configured in accordance with protocols as established by the PCI special interest group. A PCI bus is a high performance, high bandwidth bus well suited for handling transference of data between a host processor bus and I/O devices such as asynchronous transfer mode (ATM) chips or small computer system interface (SCSI) interface chips.

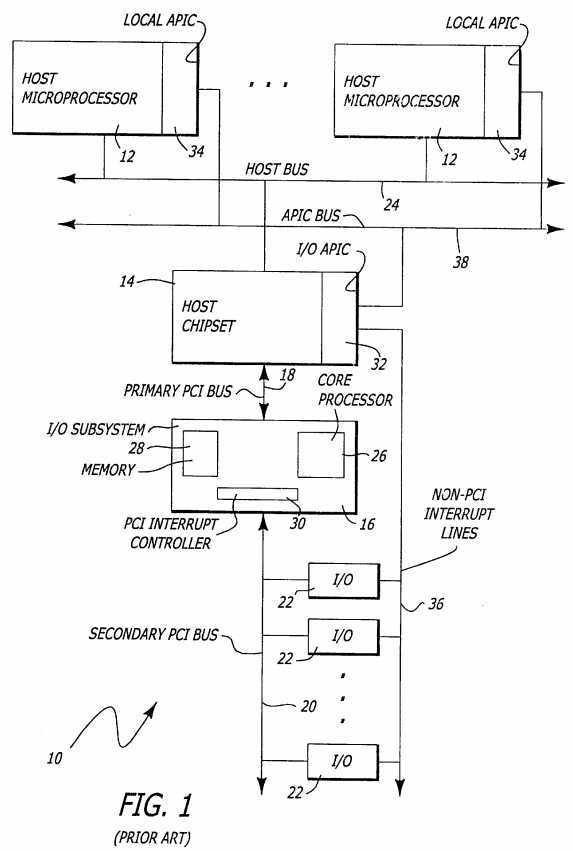

An example of a computer system configured to incorporate PCI buses is set forth in FIG. 1. More specifically, FIG. 1 illustrates a computer system 10 having set of a host microprocessors 12, a host chipset 14 and an I/O subsystem 16. A primary PCI bus 18 interconnects the host chipset and the input/output subsystem. A secondary PCI bus 20 interconnects the I/O subsystem and a set of I/O devices 22 which may include the aforementioned SCSI chips, ATM chips, or other I/O devices. The host chipset is connected to the host processor by a host bus 24 which, typically, is not a PCI bus. With this arrangement, the host chipset provides a bridge between the host bus and the primary PCI bus. The I/O subsystem provides a bridge between the primary PCI bus and the secondary PCI bus. The I/O subsystem is provided, in part, to handle I/O operations which would otherwise need to be handled by the host processor. The I/O subsystem may include a core processor 26 and a memory 28 to facilitate I/O operations. Exemplary specific components which may be configured in accordance with the architecture of FIG. 1 are Pentium or Pentium Pro host processor chips, Triton or Orion host chipsets and i960 I/O subsystems incorporating one of the 80960 family of I/O co-processor chips. Each of the foregoing are components provided by?Intel Corporation, the assignee of rights to the present application, and each component name is a trademark thereof.

By incorporating an I/O subsystem with a processor and memory and by utilizing PCI buses, high speed throughput of data is achieved between the I/O devices and the host chipset. Although such high speed data throughput is useful for many applications, computer systems arranged as in FIG. 1 are particularly useful as file servers. One disadvantage, however, of utilizing PCI buses is that the PCI protocol provides for only four?interrupt?lines. In FIG. 1, the four PCI interrupt?lines are not separately shown but are part of primary bus 18 and secondary PCI bus 20. I/O subsystem 16 includes a PCI?interrupt?controller?30 which receives the PCI interrupts and routes the interrupts, as needed, into core processor 26 for further processing. For many applications, particularly file server applications, four PCI interrupts is insufficient. To partially remedy this problem, computer system 10 incorporates an I/O APIC 32 within the host chipset and a local APIC unit 34 within each host processor. Additional non-PCI interrupt?lines 36 are connected directly from input ports of the I/O devices 22 to the I/O APIC of the host chipset. The I/O APIC of the host chipset communicates directly with the local APICs of the host processors over a dedicated 3-wire APIC bus 38. With this arrangement,?interrupt?signals generated by the I/O devices are routed directly to the I/O APIC of the host chipset which, in turn, converts the interrupts to APIC standard interrupts for routing to the host processors over the APIC bus.

Thus, the use of an I/O APIC within the host chipset allows for additional interrupt?signals to be accommodate beyond those provided by the PCI buses. The APIC architecture provides many additional features and advantages, particularly directed towards handling of interrupts within a multi-processor system. APIC is a proprietary?interrupt?processing technology provided by?Intel Corporation. The APIC?interrupt?architecture is specified within the multiprocessor specification (MPS) document version 1.1 which available from Intel Corporation?(Order No. 242016-003).

To handle interrupts, the I/O APIC includes a redirection table, several storage registers and various state machines. The state machine controls storage and processing of values within the redirection table and the various registers. Two of the registers of the I/O APIC, namely an APIC register select register and an APIC window register, are directly accessible by the local APICs of the host processors. Other registers of the I/O APIC are internally accessed by the I/O APIC only. The redirection table, the various registers and the values stored therein, as well as the operations performed by the state machines, are defined by the APIC specification. The redirection table, the registers, the state machines and any other necessary components of the I/O APIC are all formed within a single integrated chip which forms part of the host chipset.

Thus, by employing an APIC architecture, far more interrupts are accommodated than the four interrupts provided with PCI. Moreover, intelligent processing of the interrupts can be performed both within the I/O APIC and within the local APIC. As such, a computer system employing the aforementioned APIC architecture has significant advantages over a system merely using PCI interrupts. However, room for improvement remains. One problem with the arrangement of FIG. 1 is that individual?interrupt?lines must be connected directly from ports of the I/O devices to the I/O APIC within the motherboard of the computer system. Routing interrupt?lines along the motherboard is difficult, particularly for state of the art computer systems wherein components may be required to run at 200 MHz. Another disadvantage of the architecture of FIG. 1 is that the I/O APIC is hard-wired in silicon and is therefore limited in flexibility. Hence, once configured, the I/O APIC cannot merely be reprogrammed to perform additional or different APIC functions. Moreover, because the I/O APIC is configured in silicon, there are significant practical constraints on the size of the redirection table incorporated therein. As a result, practical systems incorporating an I/O APIC often include a relatively small redirection table which lacks flexibility otherwise available with a larger redirection table.

In view of the foregoing, it would desirable to provide an improved APIC architecture, particularly one which does not require?interrupt?lines to be physically connected to the host chipset from the I/O device ports and which does not have the physical and practical limitations imposed by a hard-wired I/O APIC system.

In accordance with one aspect of the invention, an improved APIC architecture is provided wherein I/O APIC functions are emulated in software running within the core processor of an I/O subsystem. In other words, rather than providing an integrated circuit I/O APIC as part of the host chipset and routing?interrupt signals from I/O device ports to the host chipset,?interrupt?lines are connected directly from the I/O device ports to the I/O subsystem which emulates an I/O APIC. A 3-wired APIC bus is connected directly from the I/O subsystem to the host processors.

In one exemplary embodiment, the foregoing is implemented within the computer system having a host processor containing a local APIC and a host chipset connected to the host processor by a host bus. An I/O subsystem is connected to the host chipset by a primary PCI bus and is connected to the local APIC of the host processor by an APIC bus. Means are provided within the I/O subsystem for receiving?interrupt?signals from I/O devices, for emulating APIC functionality, and for communicating with the local APIC of the host processor over the local APIC bus. The means for emulating the APIC functionality may be a core processor running an APIC emulation program and utilizing random access memory to configure a redirection table and utilizing a pair of registers within a messaging unit for implementing an APIC register select register and an APIC window register.

Within the exemplary embodiment, a single?interrupt?controller?is provided within the core processor of the I/O subsystem for receiving either PCI interrupts or APIC interrupts thereby allowing dual use of?interrupt?pins. Moreover, a set of multiplexers are connected between the?interrupt?pins and the?interrupt?controller?for selectively directing interrupts either to the?interrupt?controller?or directly onto?interrupt?lines of the primary PCI bus. With this multiplexer arrangement, PCI interrupts may be routed directly to the primary PCI bus or maybe routed into the?interrupt?controller?for further processing within the core processor of the I/O subsystem. The multiplexer directs all APIC interrupts into the?interrupt?controller?for processing the APIC emulation software within the core processor. Thereafter, the core processor utilizes an APIC bus interface unit, which is connected to the APIC bus, for forwarding the APIC interrupts to the host processors of the computer system.

With this arrangement, APIC functionality is integrated into the I/O subsystem thereby eliminating the need to route numerous individual?interrupt?lines to the host chipset. Moreover, by integrating APIC functionality within the I/O subsystem, interrupt processing intelligence is added at the lowest level of the?interrupt?structure to perform the most amount of work where it is required, i.e., within the I/O subsystem itself. By utilizing?interrupt?pins to handle both PCI interrupts and APIC interrupts, a considerable savings in pin count is achieved along with savings in package real state and silicon. The dual use of processor interrupts also allows for the aforementioned?programmable?routing of?interrupt?signals. By using a portion of the I/O subsystem memory to represent the redirection table, a substantially larger redirection table can be defined than is practical within a hard-wired silicon redirection table as required with previous APIC configurations. The larger redirection table allows for greater flexibility in tracking and redirecting?interrupt?signals. Since many I/O subsystems already employ or require memories, the APIC redirection table is implemented without a significant increase in required resources. Various APIC registers are also mapped into the I/O subsystem memory thereby saving further silicon real state. Only the aforementioned APIC register select register and APIC window register, which are defined by the APIC architect specification to be directly accessible by host processors over the APIC bus, need to be configured as actual physical registers. As noted, these registers are implemented within a messaging unit which is normally provided within state of the art I/O subsystems of computers employing APIC.

Thus, significant advantages are achieved without requiring additional resources. Indeed, resources which would otherwise need to be provided within the host chipset can be eliminated therefrom, including the entire I/O APIC IC.

FIG. 1 is a block diagram of a computer system incorporating an I/O APIC within a host chipset and configured in accordance with the prior art.

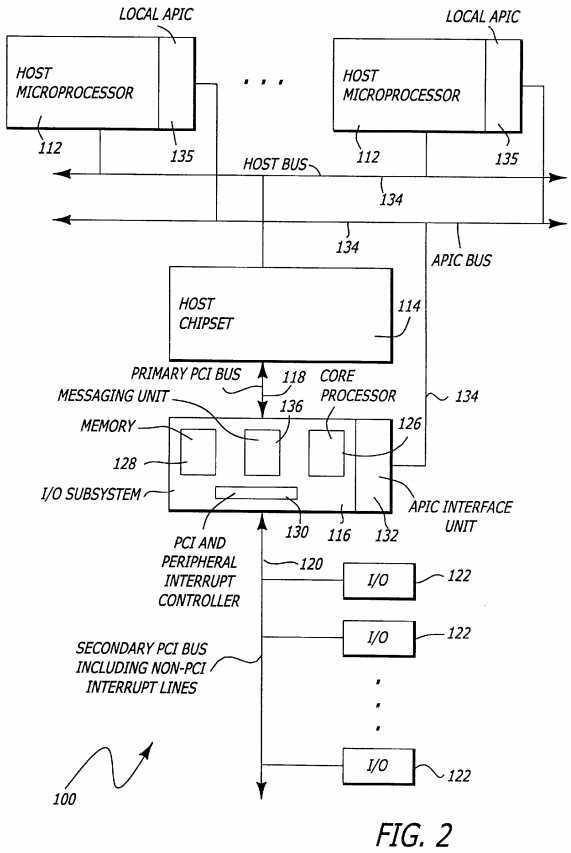

FIG. 2 is a block diagram of a computer system having I/O APIC functionality integrated within an I/O subsystem and partially emulated by software therein, in accordance with an exemplary embodiment of the invention.

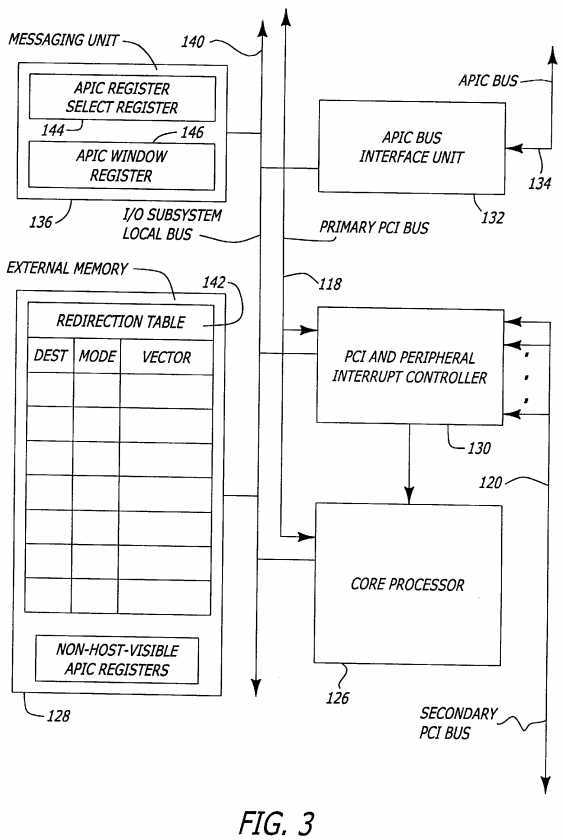

FIG. 3 is a block diagram of selected internal components of the I/O subsystem of FIG. 2.

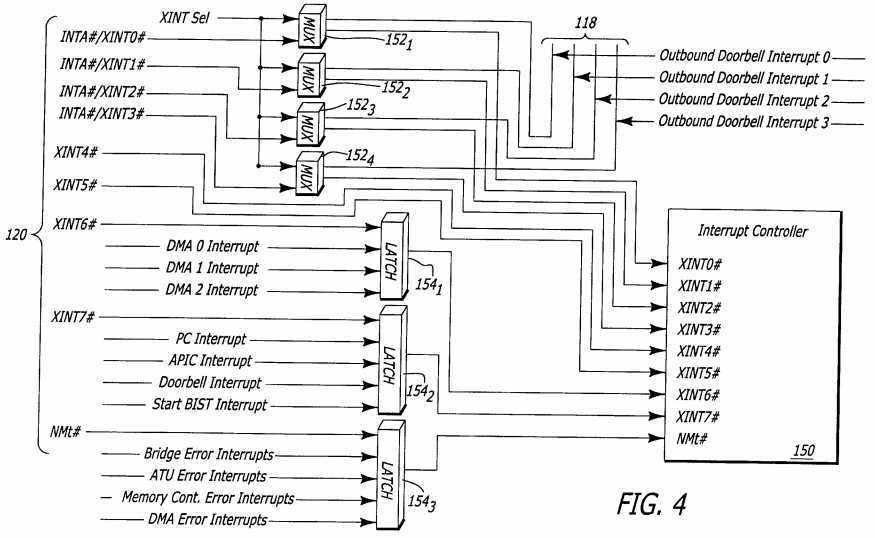

FIG. 4 is a block diagram illustrating a PCI and peripheral?interrupt?controller?of FIG. 3.

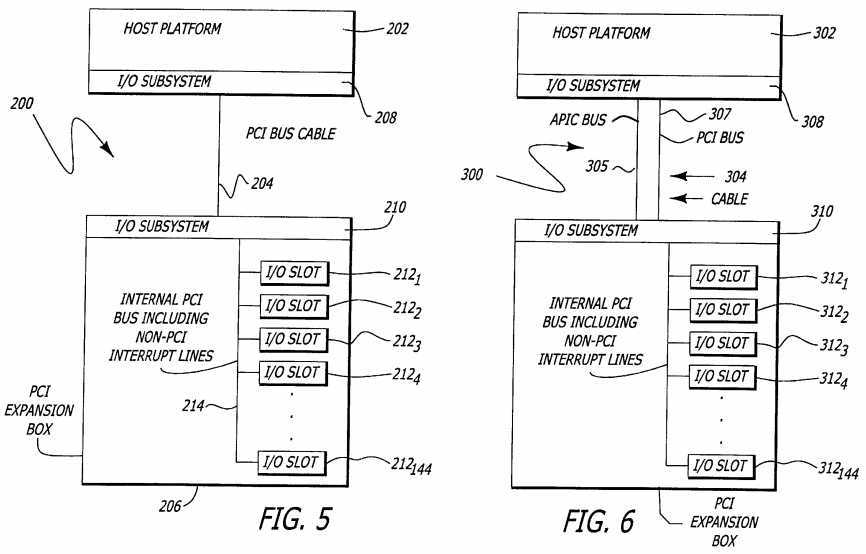

FIG. 5 is a block diagram of a computer system having a host platform connected to a PCI expansion box by a PCI cable connection line wherein APIC interrupts are transmitted over the PCI cable as encoded PCI data signals.

FIG. 6 is a block diagram of a computer system having a host platform connected to a PCI expansion box by a PCI cable connection line having separate APIC connection lines.

FIG. 2 illustrates a computer system 100 having a set of host processors, generally denoted 112, a host chipset 114 and an I/O subsystem 116. A primary PCI bus 118 interconnects the host chipset and the I/O subsystem. A secondary PCI bus 120 interconnects the I/O subsystem with I/O ports 122 of I/O devices. The host microprocessors are interconnected to the host chipset by a host bus 124. Although not separately shown, additional devices may be connected to the host bus. For example, an additional host chipset in combination with an additional I/O subsystem and additional PCI buses may be provided. A cluster attachment may also be connected to the host bus to allow for additional microprocessors to be interconnected in a multi-processing arrangement.

I/O subsystem 116 includes, as principal components, a core processor 126, a memory 128, a PCI and peripheral?interrupt controller?130 and an APIC bus interface unit 132. The APIC bus interface unit of the I/O subsystem is connected by a 3-wire APIC bus 134 to local APIC units of each of the host processors. I/O subsystem 116 also includes a messaging unit 136 which facilitates transmission of data between the PCI buses to the core processor 126. As will be described below, messaging unit 136 also includes two host-visible APIC registers--an APIC register select register and an APIC window register within the messaging unit.

PCI and peripheral?interrupt?controller?130 receives PCI interrupts and non-PCI interrupts and routes the interrupts, in a manner to be described below, either to core processor 126 or to primary PCI bus 118. Core processor 126 runs software configured to emulate APIC functionality. The software emulates APIC functions that would otherwise be performed by a separate I/O APIC chip within the host chipset. In this regard, the emulation software creates and accesses all non-host-visible APIC registers and a redirection table within memory 128 and accesses the host-visible registers the messaging unit. The APIC emulation software forwards non-PCI interrupts to the APIC bus through APIC bus interface unit 132 as APIC interrupts. Likewise, the emulation software receives responsive end of?interrupt?(EOI) signals from host processors over the APIC bus for routing to the individual I/O devices connected to the I/O ports.

Thus, FIG. 2 illustrates a computer system wherein APIC functionality is integrated within an I/O subsystem rather than provided as a separate chip within a host chipset. APIC integration is achieved, in part, by the emulation software running within the core processor and by the registers and tables of the messaging unit and the memory. The manner by which APIC emulation is achieved will be described in more detail with reference to the remaining figures.

FIG. 3 illustrates, in block diagram form, primary components of the I/O subsystem configured for APIC emulation. More specifically, FIG. 3 illustrates the aforementioned core processor 126, APIC bus interface unit 132, PCI and peripheral interrupt?controller?130, memory 128 and messaging unit 136. These components are interconnected by an I/O subsystem local bus 140. Memory 128 is configured to include a redirection table 142 having, for each of a number of?interrupt?entries, a destination value, a mode value and a vector value. Memory 128 is also employed to store values corresponding to all APIC registers other than the APIC register select register and the APIC window register which must be accessible to the local APICs of the host processors over the 3-wire APIC bus. Messaging unit 136 includes an APIC register select register 144 and an APIC window register 146.

Interrupt?signals, including both PCI and non-PCI interrupts, are received from external I/O devices either along the secondary PCI bus (FIG. 2) or along separate?interrupt?lines by the PCI and peripheral?interrupt?controller.?Controller?130 routes all non-PCI interrupts directly to core processor 126. Core processor 126 processes the non-PCI interrupts in accordance with APIC processing protocols and forwards the APIC interrupts, as needed, over the local bus to the APIC bus interface unit for further transmission onto to the APIC bus. In this regard, the core processor accesses the registers and the redirection table of memory 128 and the registers of messaging unit 136. In general, the manner by which the registers and the redirection table are accessed and utilized may be the same with conventional APIC architectures other than any modifications necessary to accommodate access via a local bus rather than direct access as with a separate I/O APIC integrated circuit. Additional details may be found within Appendix A entitled "APIC Bus Interface Unit" which is attached hereto and incorporated by reference herein. Additional details of the overall operation of the I/O subsystem may be found within a patent application entitled, "Architecture for an I/O Processor that Integrates a PCI to PCI Bridge," filed Jun. 5, 1997, having Ser. No. 08/870,141, which is a continuation of application filed Jun. 15, 1995, having Ser. No. 08/490,654, now abandoned, and assigned to the assignee of the rights of the present application. The aforementioned patent application is also incorporated by reference herein. Both Appendix A and the above-referenced patent application describe a specific implementation of the I/O subsystem identified as the i960(R) P2P microprocessor which incorporates an Intel 80960JF processor as the core processor of the I/O subsystem. However, principles of the invention may be incorporated in other computer systems incorporating other specific I/O subsystem components and sub-components.

Thus, non-PCI interrupts are routed into the core processor, then ultimately rerouted, if necessary, onto the APIC bus for processing by the host processors. (Many of the non-PIC interrupts may be processed by the core processor without requiring forwarding to the host processors. In general, only those non-PCI interrupts requiring processing by the host processors will be forwarded on the PIC bus.) PCI interrupts, on the other hand, received by the PCI and peripheral interrupt?controller?are either directed to core processor 126 or are retransmitted directly onto primary PCI bus 118. If processed by core processor 126, the PCI interrupts may either be retransmitted onto primary bus 118 or, if desirable, processed internally by the core processor without requiring transmission onto the primary PCI bus. The manner by which both PCI and non-PCI interrupts are processed by the core is further described in the above-referenced patent application and within Appendix A.

Thus, FIG. 3 illustrates one exemplary implementation wherein APIC functionality may be emulated within an I/O subsystem. Important features of the exemplary implementation include the use of memory to represent an I/O redirection table. By using memory, rather than integrated circuit registers, the redirection table may be made as large as desired affording considerably greater flexibility than can be achieved in hard-wired redirection tables. Likewise, by emulating APIC functionality with the software, rather than using hard-wired state machines and the like, considerable processing flexibility is achieved. Software can be modified and updated to incorporate additional functionality without requiring design of a new APIC integrated circuit chip. Moreover, the APIC emulation software may be designed to perform far more functions than could be performed within a practical integrated circuit implementation subject to significant physical and cost constraints. The foregoing is achieved without requiring additional significant I/O subsystem resources. As noted above in the Description of Related Art section, many conventional state of the art I/O systems already incorporate a core processor, memory, and the like.

As to the emulation software for running within the core processor, the actual design and configuration of such software depends upon the specific hardware employed within the I/O subsystem including the core processor hardware, the messaging unit hardware and the memory hardware. Those of ordinary skill in the art, given the description provided herein and the APIC specifications set forth in the above-referenced documents, can develop appropriate software for use with a suitable hardware components for emulating APIC functionality.

FIG. 4 illustrates an example of one possible implementation of the PCI and peripheral?interrupt?controller. More specifically, FIG. 4 illustrates an?interrupt?controller?150 (which may form the portion of the core processor of FIG. 3), a set of?interrupt redirection multiplexers 1521?-1524?and a set of?interrupt?input latches 1541?-1542.?Interrupt?controller?150 includes nine inputs corresponding to eight?interrupt?inputs (XINT0-XINT7) and one NMI?interrupt. Outputs of latches 1541, 1542, and 1543?are connected, respectively, to?controller?inputs MNT6, XINT7 and NMI. Inputs to the latches include, as shown in FIG. 4, non-PCI?interrupt?signals INT6, INT7 and NMI as well as various DMA interrupts, doorbell interrupts, bridge area interrupts and the like. Each of the latches includes a binary value (not separately shown) which identifies the origin of the interrupt?signal held therein. The additional interrupts (i.e., those interrupts other than PCI interrupts INTA-INTD and the non-PCI interrupts INT0-INT7) are not pertinent to the present invention and will not be further described.

Each of multiplexers 152 is connected to a single corresponding input pin for receiving a PCI?interrupt?(i.e., INTA-INTD) or a non-PCI?interrupt?(i.e., XINT0-XINT3). Outputs of multiplexers 1521?-1524?are connected, respectively, to inputs XINT0-XINT3 of?controller?150. A second output of each of multiplexers 152 are connected to?interrupt?lines of the primary PCI bus. With this arrangement, input signals received by the multiplexers may be directed either onto the primary PCI bus or into the?interrupt?controller. Selection is achieved using an XINT select signal which is generated by the core processor. In use, non-PCI interrupts are always directed into the core processor to the?interrupt?controller?for processing therein, perhaps as APIC interrupts. PCI interrupts may either be directed onto the primary PCI bus or directed into the core processor for processing therein.

With this arrangement, both PCI and non-PCI interrupts are accommodated without requiring a separate input pin for each interrupt. The use of multiplexers allows greater flexibility and routing PCI?interrupt?signals. Of course, other arrangements may be provided for receiving and routing?interrupt?signals within the I/O subsystem and the embodiment of FIG. 4 is merely one example.

As thus far described, the integrated APIC architecture of the present invention allows multiple?interrupt?signals to be received and processed by a single I/O subsystem then forwarded to host computers over a single 3-wire APIC bus. The elimination of the need to route separate?interrupt?lines for each separate non-PCI?interrupt?to a host chipset is a significant advantage. One implementation exploiting this advantage is illustrated in FIG. 5. More specifically, FIG. 5 illustrates a computer system 200 having a host platform 202 connected by a cable 204 to a PCI expansion box 206. The host platform 202 includes components illustrated in FIG. 3 including one or more host processors, a host chipset and an I/O subsystem. Within FIG. 5, only I/O subsystem 208 of host platform 202 is illustrated. PCI expansion box 206 also includes an I/O subsystem 210. Expansion box 206 includes individual I/O device connection slots 212 all interconnected to an internal PCI bus 214. In exemplary embodiments, as many as 144, or more, slots may be provided. Bus 214 also includes non-PCI interrupt?lines connecting each of the?interrupt?slots to I/O subsystem 210.

I/O subsystem 210 includes an integrated APIC emulation arrangement, such as set forth in FIG. 3, wherein non-PCI interrupts are received and converted to APIC interrupts. Emulation software within I/O subsystem 210, however, also converts or encodes the APIC interrupts to PCI data signals for transmission over PCI bus 204. I/O subsystem 208 incorporates APIC emulation software which detects the encoded APIC interrupts, extracts the interrupts from the PCI data signals, and recreates APIC?interrupt?signals for transmitting over an internal 3-wire APIC bus (not separately shown) to host processors of the host platform 202. Thus, with this arrangement, non-PCI interrupts generated by the I/O devices are received by I/O subsystem 210, converted to PCI data packets and transmitted over PCI bus 204, then reconverted to interrupt?signals by I/O subsystem 208. Without such an arrangement, the expansion box of FIG. 5 would not likely be feasible. Either separate?interrupt?lines for each of the input/output ports would need to be separately routed into the host platform or the I/O devices would need to rely on only the four dedicated PCI?interrupt?lines. Neither is a practical option, particularly for a PCI expansion box having up to 144 expansion slots. Although not separately shown in FIG. 5, to accommodate a 144 expansion slots, PCI expansion box 206 may require a number of PCI buses interconnected in a hierarchical arrangement through a number of PCI to PCI bridges such as I/O subsystem 210. For clarity in FIG. 5, only a single internal PCI bus is illustrated in connection with only a single I/O subsystem.

An alternative arrangement, illustrated in FIG. 6, provides a 3-wire APIC bus along with the PCI cable. The embodiment of FIG. 6 is similar to that of FIG. 5 with like components represented by like reference numerals incremented by 100. Only pertinent differences will be described. Cable 304 includes a 3-wire APIC bus 305 in addition to a PCI bus 307. APIC emulation software within subsystem 210 receives non-PCI interrupts from the I/O slots and converts those interrupts to APIC interrupts for forwarding over APIC bus 305 of cable 304. As such, the APIC interrupts need not be encoded as PCI data. Within the host platform, the 3-wire APIC bus may be directly connected into local APICs of host processors (not separately shown) or may be connected into an I/O subsystem of the type illustrated above in FIG. 3. Other arrangements for transmitting APIC interrupts from the PCI expansion box to the host platform may be provided in a manner consistent with the principles of the invention.

What has been described is a computer system having APIC functionality integrated within an I/O subsystem rather than having a separate I/O APIC chip formed as portion of a host chipset. The integrated APIC architecture has been described with reference to specific exemplary embodiments. These embodiments are provided to merely illustrate the principles of the invention and should not be construed as limiting the scope of the invention.

SRC=https://www.google.com.hk/patents/US5857090

标签:des style blog http color os io ar for

原文地址:http://www.cnblogs.com/coryxie/p/3963396.html