标签:有一个 ges tps 时钟 交流群 区域 fifo 好的 同步

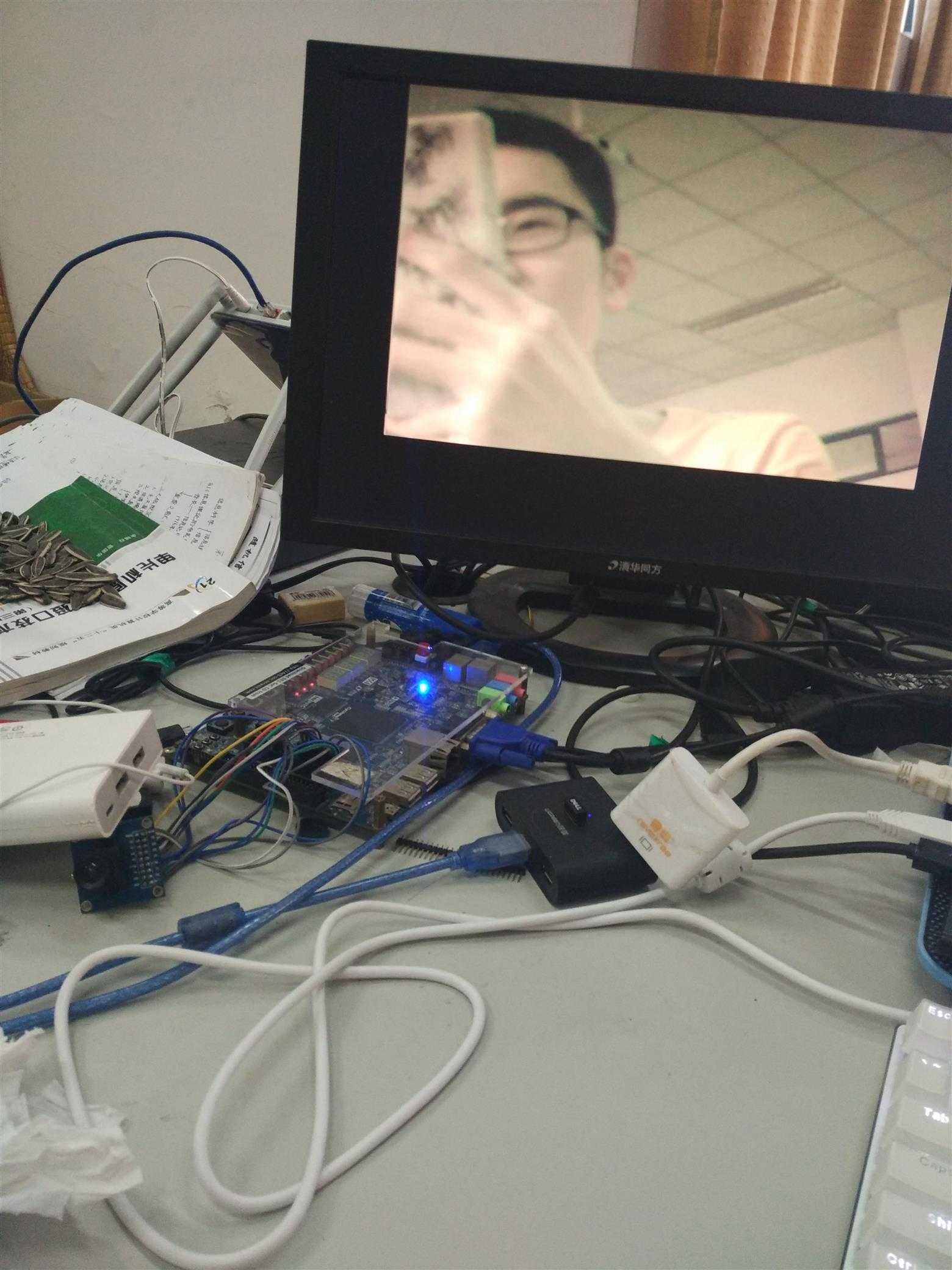

从开学开始写程序,写了大约三个周,程序写的差不多了,然后又调试了一个周,今天可以将ov7670采集的数据显示在显示屏上面了,在调试的过程

遇到了很多bug,简单的几分钟能解决,麻烦的可以调试上一天,而且quartus编译速度又慢,调试一次就得几分钟,等的过程也是比较煎熬的。趁现在刚调试

过了没多久,记录一下之前遇见的bug以及解决过程。

标签:有一个 ges tps 时钟 交流群 区域 fifo 好的 同步

原文地址:http://www.cnblogs.com/bixiaopengblog/p/7612576.html