标签:verilog 区分 使用说明 调试 用户 硬件 注意事项 功能 logs

最近在调试一个LVDS的屏显功能,涉及到了一些LVDS的东东,简单地整理如下,后续会再补充。

(1)对于altera FPGA(CYCLONE III)

1、对于作为LVDS传输的BANK必须接2.5V的VCCIO;

2、左右BANK(即1/2/5/6 BANK)的LVDS发送差分对信号无需外接匹配电阻,而上下BANK(即3/4/7/8 BANK)则需要,如果硬件工程师忘了,还可以在FPGA的IO引脚分配时里加端接电阻设置;

3、分配管脚时,左右BANK的LVDS差分信号脚在IO分配时选择的IO电平标准是LVDS,而上下BANK的LVDS差分信号脚在IO分配时选择的IO电平标准是LVDS_E_3R;

4、分配管脚时,只要指定LVDS信号的p端(+),则n端(-)会自动分配。在verilog代码中只要一个信号接口即可,无需在代码中定义一个差分对接口;

5、在altera FPGA内使用的LVDS收发IP核是altlvds_rx和altlvds_tx,相应的IP使用说明在megawizard里有。

(2)对于xilinx FPGA

区别altera的地方在于首先在Verilog的代码里,xilinx的LVDS信号需要定义一对差分对信号,通过xilinx的原语进行差分对转单端或者单端转成差分对信号。另外在IO引脚分配时,xilinx的电平标准都是一样的,比如都是LVDS_33。

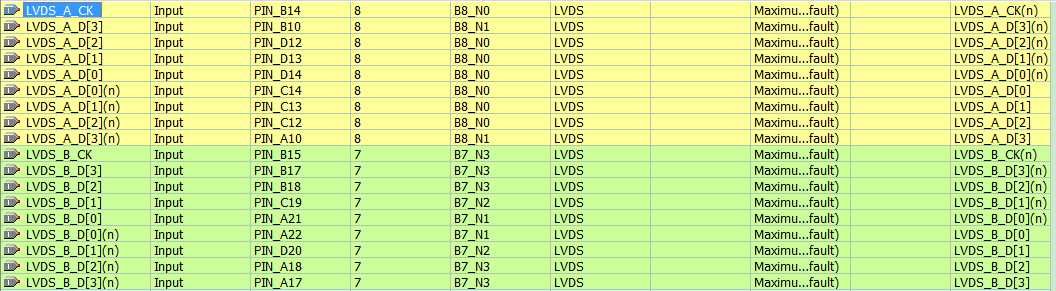

下图1是altera下的LVDS信号引脚分配,可见用户只需要分配p端(+)引脚即可。

图1 altera LVDS引脚分配情况

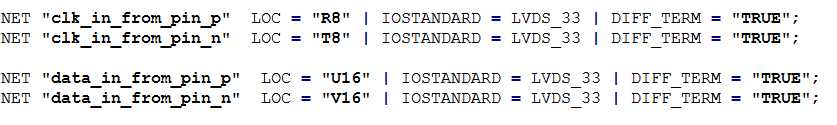

下图2是xilinx的LVDS信号引脚分配,xilinx的LVDS引脚区分p端和n端。当然在vivado下引脚分配可以只分配P端脚号,N端脚号会自动分配。而在代码里都需要写明差分对信号,再通过原语转成单端信号。

图2 xilinx下LVDS的引脚分配情况

标签:verilog 区分 使用说明 调试 用户 硬件 注意事项 功能 logs

原文地址:http://www.cnblogs.com/tubujia/p/7651590.html