标签:传输 差分对 重要 数据传输 back round 微信公众号 image erro

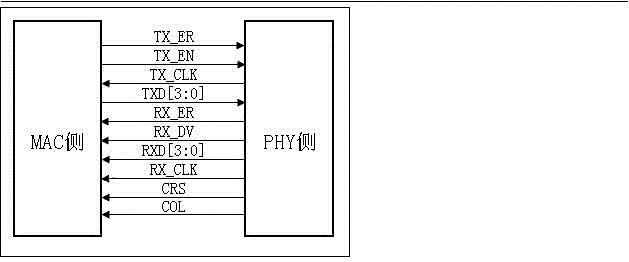

MII (Media Independent Interface(介质无关接口);或称为媒体独立接口,它是IEEE-802.3定义的以太网行业标准。它包括一个数据接口,以及一个MAC和PHY之间的管理接口。数据接口包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需要16个信号。管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。MII (Management interface)只有两条信号线。

MII标准接口用于连快Fast Ethernet MAC-block与PHY。"介质无关"表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。在其他速率下工作的与 MII等效的接口有:AUI(10M 以太网)、GMII(Gigabit 以太网)和XAUI(10-Gigabit 以太网)。

TXD(Transmit Data)[3:0]:数据发送信号,共4根信号线;

RXD(Receive Data)[3:0]:数据接收信号,共4根信号线;

TX_ER(Transmit Error): 发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。对于10Mbps速率下,TX_ER不起作用;

RX_ER(Receive Error): 接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。对于10Mbps速率下,RX_ER不起作用;

TX_EN(Transmit Enable): 发送使能信号,只有在TX_EN有效期内传的数据才有效;

RX_DV(Reveive Data Valid): 接收数据有效信号,作用类型于发送通道的TX_EN;

TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,另外,CRS只有PHY在半双工模式下有效;

COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只有PHY在半双工模式下有效。

MII接口一共有16根线。

以太网协议分7层,PHY通常称为物理层,也就是第一层,MAC层属于第二层,是数据链路层的一个子层。第三层为网络层,也叫IP层,第四层为传输层,主要协议是TCP/UDP协议。

以太网物理层接口主要是水晶头和RJ45,为了保证信号传输质量,网线(双绞线)上的信号都被调制成成对的差分信号传输。所以,物理层芯片的一个主要作用就是将双绞线上的差分信号(串行比特流)进行解码,转换成并行数据,或者将上层发下来的并行数据转换成串行的差分对输出到网线上。对于百兆以太网,并行数据是4位的,所以PHY和上层的并行接口是4位的,MII数据接口是半字节(nibble)的。在以太网传输的过程中,这里指PHY的串行传输,一个字节的最不重要位最先传输,即低位最先传输。

以太网传输数据时先传输高字节,传输字节时先传输低位。比特流进入物理芯片后,在100M是通过MII口输出低半字节在前,高半字节在后。所以在从物理层接收到数据后要注意高半字节和低半字节的顺序。

版权所有权归卿萃科技,转载请注明出处

作者:卿萃科技ALIFPGA

原文地址:卿萃科技FPGA极客空间 微信公众号

扫描二维码关注卿萃科技FPGA极客空间

标签:传输 差分对 重要 数据传输 back round 微信公众号 image erro

原文地址:http://www.cnblogs.com/alifpga/p/7660603.html