标签:思路 内容 enter cache 存储 分享 cpu 描述 使用

全面学习理解TLB(Translation Look-aside Buffer)地址变换高速缓存

前言:

本文学习思路是:存在缘由 --> 存在好处 --> 定义性质 --> 具体分析

存在缘由:

由于地址映射(从虚拟地址转换成物理地址)需要的开销开大。

转换过程如下:

为了提高效率,现代CPU都包含了一个特殊Cache来跟踪最近使用过的地址变换,这个就是TLB。

明显好处:

如果有了TLB,那么地址转换变成如下过程:

这样就省去了一次访问内存的时间,大大提高了效率。

概念概括:

TLB英文全称:Translation Look-aside Buffer

TLB中文全称:地址变换高速缓存

TLB中文简称:快表

TLB实际性质:它是一种cache

TLB的每一项中包含

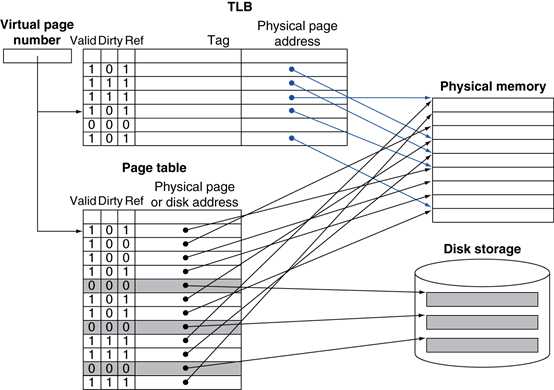

利用TLB进行快速地址转换的过程图

过程描述如下:

首先,先去TLB中根据标志Tag寻找,假如找到了并且有效位是1,说明TLB命中了,那么直接就可以从TLB中获取该虚拟页号对应的物理页号。假如有效位是0,说明该页不在内存中,这时候就发生缺页异常,CPU需要先去外存中将该页调入内存并将页表和TLB更新。

假如在TLB中没有找到,那么就去页表(Page Table)中寻找(以虚拟页号为索引),假如找到了并且有效位是1,那么就可以取出对应的物理页号。假如有效位是0,说明该页不在内存中,这时候就发生缺页异常,CPU需要先去外存中将该页调入内存并将页表和TLB更新。

假如在页表中没有找到,也是缺页。同意会执行上述的缺页处理。

(不管从哪获取到物理页号,都可以根据规则组拼成实际物理地址,然后就可以访存去数据啦)

引用位、脏位何时更新?

页表和TLB都有这两个标志位。如果是TLB命中,那么引用位就会被置1,当TLB或页表满时,就会根据该引用位选择适合的替换位置。如果TLB命中且这个访存操作是个写操作,那么脏位就会被置1,表明该页被修改过,当该页要从内存中移除时会先执行将该页写会外存的操作,保证数据被正确修改。

当TLB的某一项要被替换时,它的引用位和脏位都会被更新会页表。

补充:

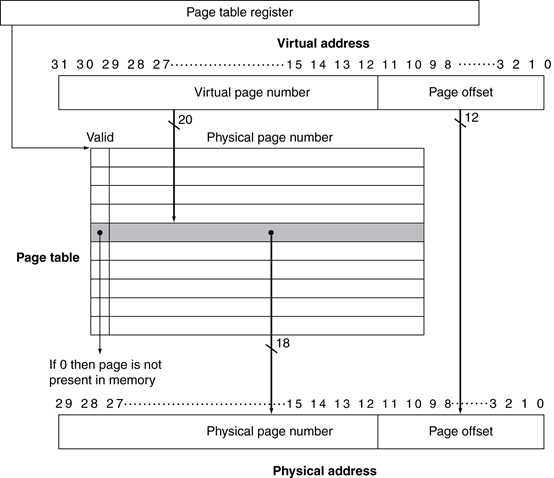

虚拟地址转换成物理地址的简略图(没有TLB只有页表时的情况)

全面学习理解TLB(Translation Look-aside Buffer)地址变换高速缓存

标签:思路 内容 enter cache 存储 分享 cpu 描述 使用

原文地址:http://www.cnblogs.com/toulanboy/p/7745880.html