标签:就会 文件名 project 它的 部分 信号 pga 破解 when

我们专业这学期加了FPGA这门课,老师教授方式自己有点不习惯,我就在自学。后续会持续更新相关进度,欢迎大佬们指导

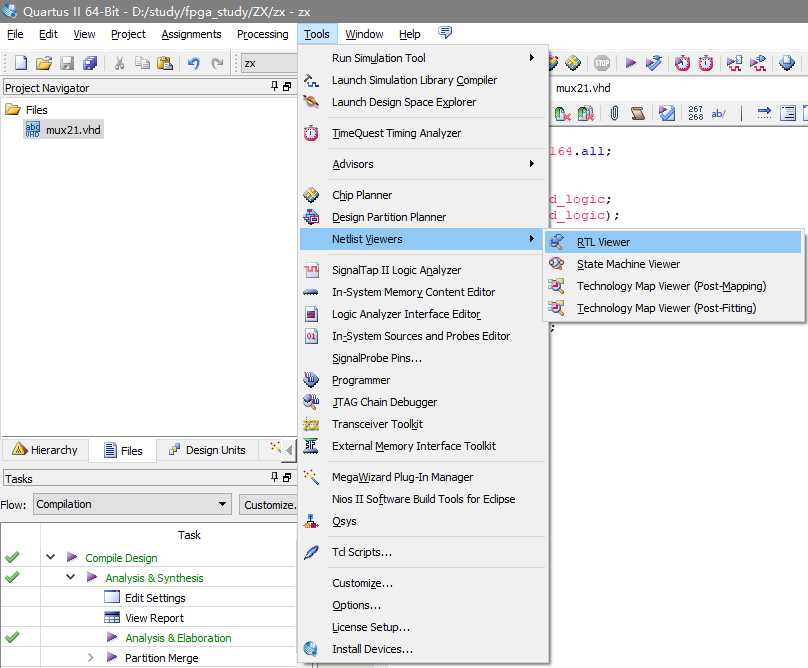

相关软件我是用Quartus II 13.0 我把相关库全部从官网下载下来了,需要的可以找我,安装时间有点久了(怎么破解的已经忘了)

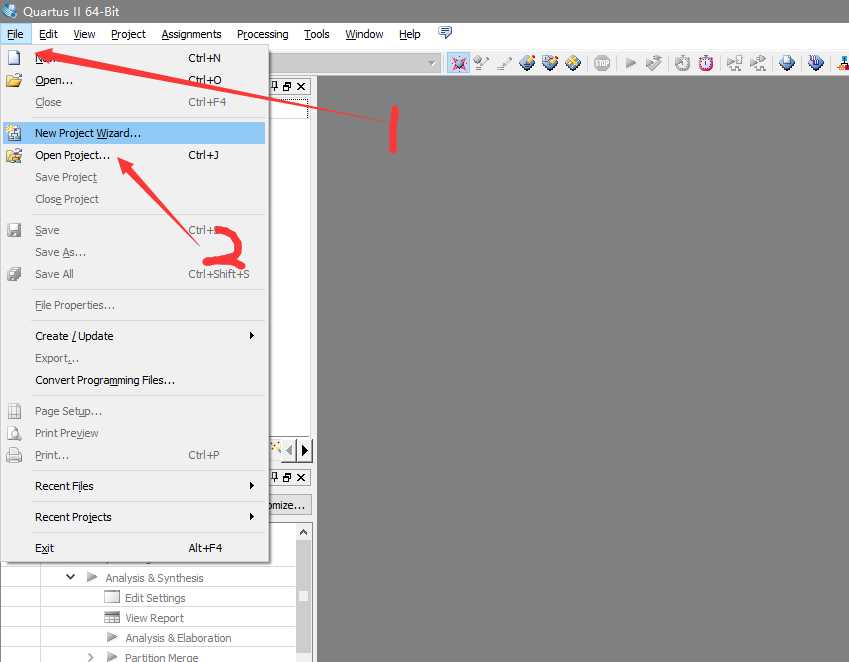

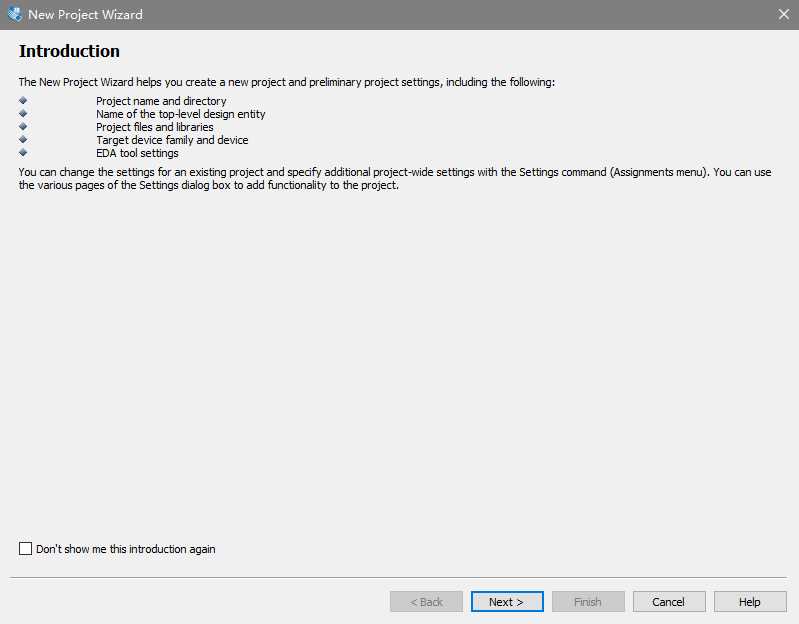

先来建立一个工程

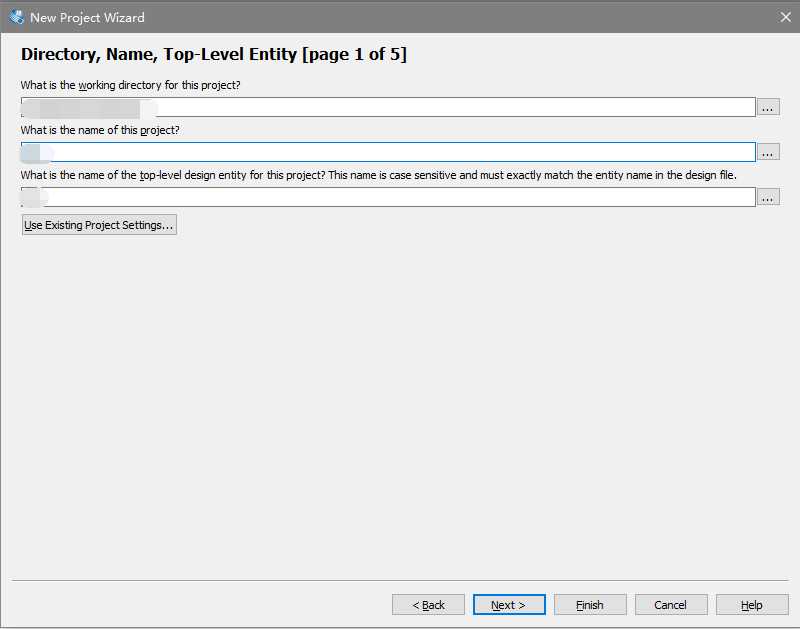

下面是自己这个工程存放的位置

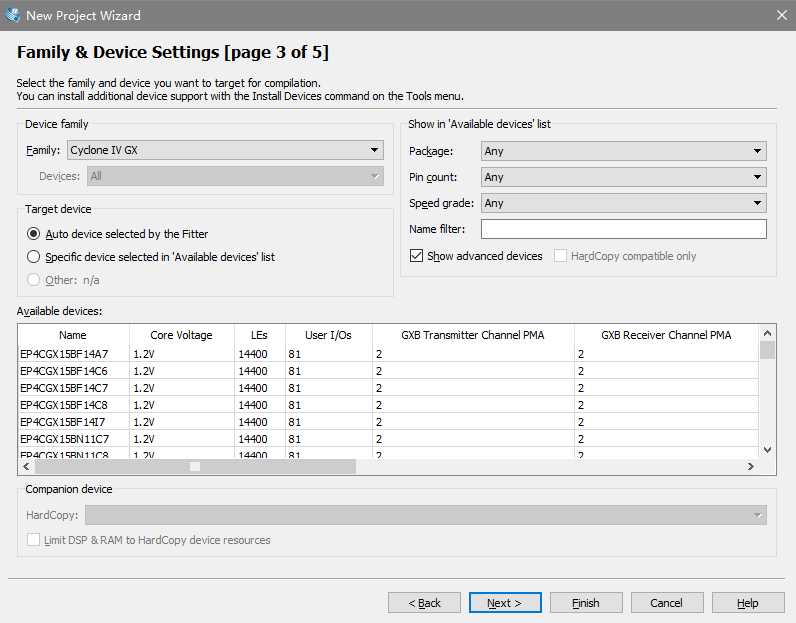

下面是选择自己开发板的芯片型号,在之前安装了芯片库之后这里就会有之前安装的库对应的芯片。

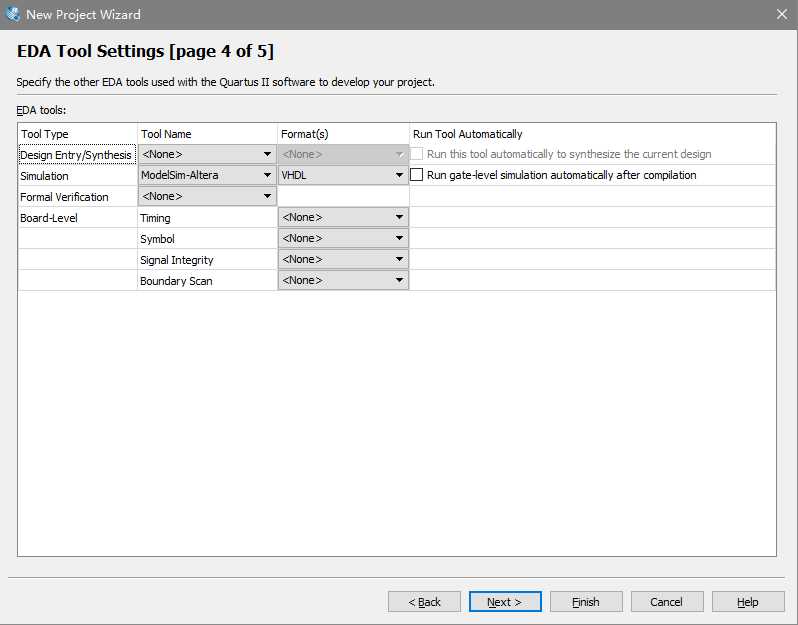

这里是建立你写程序的文本(我不知道具体名称,就让我这么说吧)

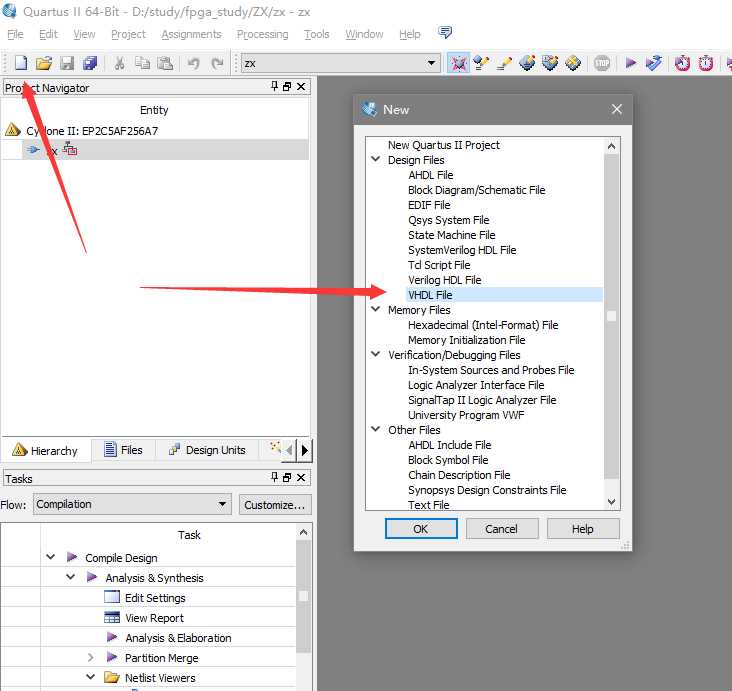

这个图是VHDL设计流程图,讲的很详细,大家可以看一下

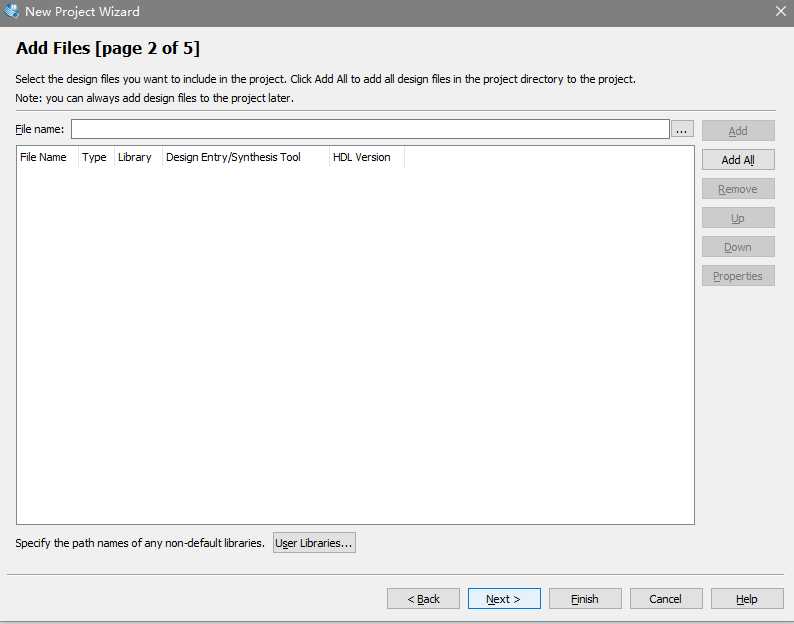

先写一个2选一的选择器,保存工程时记得文件名和程序中实体名要一致,最后将这个文件加入这个工程就可以开始编译了(加入方式:project->archive project)

library ieee;

use ieee.std_logic_1164.all;

entity mux21 is

port( a,b,s:in std_logic;

y:out std_logic);

end entity mux21;

architecture one of mux21 is

begin

y <= a when s = ‘0‘ else

b when s = ‘1‘;

end architecture one;

上面这个选择器整体设计的 VHDL 描述使用了三个层次

(1) 库(LIBRARY)说明

它包含了描述器件的输入 输出端口数据类型 即端口信号的取值类型或范围 中将要用到的 IEEE 的标准库中的 STD_LOGIC_1164 程序包明确地指定和严格地定义端口信号的取值类型是 VHDL 的重要特点 此所谓强类型语言 这是学习 VHDL 特别应当注意的地方

(2) 实体(ENTITY)说明

实体的电路意义相当于器件 在电路原理图上相当于元件符号 实体是一个完整的独立的语言模块 它描述了 mux21 接口信息 定义了器件 mux21 端口引脚 a b s y的输入输出性质和数据类型 它利用 PORT 语句说明了 mux21 的外部引脚的工作方式所以 PORT 所描述的就相当于电路器件的外部引脚 IN 对端口引脚 a 和 b 作了信号流向的方向说明 它规定了信号必须由外部通过端口引脚 a b 流进所描述的器件内部 而 OUT则规定了器件内部的信号需通过端口引脚 y 向外输出 同时指明了端口 a b s 和 y 信号的数据类型是符合 IEEE STD_LOGIC_1164 程序包中的标准数据位 STD_LOGIC中所定义的数据类型

(3) 结构体(ARCHITECTURE)说明

这一层次描述了 mux21 内部的逻辑功能 在电路上相当于器件的内部电路结构 此例的逻辑描述十分简洁 它并没有将选择器内部逻辑门的连接方式表达出来 而是将此选择器看成一个黑盒 以类似于计算机高级语言的表达方式描述了它的外部逻辑行为 符号<= 是信号赋值符 是信号传递的意思 y <= a 表示将 a 获得的信号赋给(传入)y输出端 这是一个单向过程

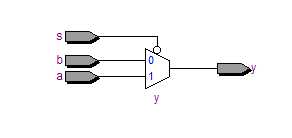

提示没错就可以看看你的2选一选择器长什么样啦

我的2选一选择器长这样

我们趁热打铁,再来写一个锁存器(新建一个VHDL文件就好,不必在建一个工程)

entity latch01 is

port( d,ena:bit;

q:out bit);

end latch01;

architecture one of latch01 is

signal sig_save : bit;

begin

process(d,ena)

begin

if(ena = ‘1‘) then

sig_save <= d;

end if;

q <= sig_save;

end process;

end one;

在 1 位锁存器的设计文件中增加了两个部分的内容

(1) 增加了一条信号赋值语句 SIGNAL

由信号赋值语句 SIGNAL 定义了一个信号变量 sig_save 它的功能是存储来自外 部信号 D 的被锁存的数据位 显然 经综合后将由一个硬件时序器件来完成这一任务

(2) 使用了一个进程语句结构 PROCESS (D, ENA)?END PROCESS

这个语句从系统仿真的角度看 是为此语句结构的行为仿真设定了两个敏感量 D 和ENA 以利于逻辑顺序的测定 但从系统综合结果的角度看 必须引入锁存器才能完成这个时序逻辑过程(VHDL 综合器根据语句自动判别 并完成寄存器的引入)

标签:就会 文件名 project 它的 部分 信号 pga 破解 when

原文地址:http://www.cnblogs.com/xu2hky/p/7799303.html