时钟是STM32单片机的驱动源,使用任何一个外设都必须打开相应的时钟。这样的好处就是,如果不使用一个外设的时候,就把它的时钟关掉,从而可以降低系统的功耗,达到节能,实现低功耗的效果。(低功耗)

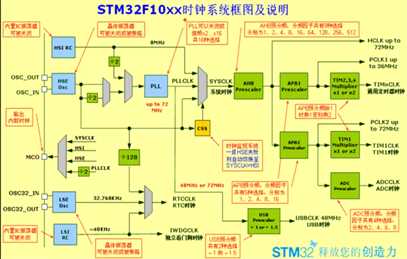

在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

⑤、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

备注:MCO接口的两个作用 --①其上有选择开关,可以观察波形是否正常

--②可以作为其他部件的时钟

系统时钟SYSCLK,它是供STM32中绝大部分部件工作的时钟源。系统时钟可选择为PLL输出、HSI或者HSE。系统时钟最大频率为72MHz,它通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。其中AHB分频器输出的时钟送给5大模块使用:

①、送给AHB总线、内核、内存和DMA使用的HCLK时钟。

②、通过8分频后送给Cortex的系统定时器时钟。

③、直接送给Cortex的空闲运行时钟FCLK。

④、送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出一路供APB1外设使用(PCLK1,最大频率36MHz),另一路送给定时器(Timer)2、3、4倍频器使用。该倍频器可选择1或者2倍频,时钟输出供定时器2、3、4使用。

⑤、送给APB2分频器。APB2分频器可选择1、2、4、8、16分频,其输出一路供APB2外设使用(PCLK2,最大频率72MHz),另一路送给定时器(Timer)1倍频器使用。该倍频器可选择1或者2倍频,时钟输出供定时器1使用。另外,APB2分频器还有一路输出供ADC分频器使用,分频后送给ADC模块使用。ADC分频器可选择为2、4、6、8分频。

STM32单片机的时钟可以由以下3个时钟源提供:

1、HSI:高速内部时钟信号 stm32单片机内带的时钟 (8M频率) 精度较差

2、HSE:高速外部时钟信号 精度高 来源(1)HSE外部晶体/陶瓷谐振器(晶振) (2)HSE用户外部时钟

3、LSE:低速外部晶体 32.768kHz 主要提供一个精确的时钟源 一般作为RTC时钟使用

stm32单片机的将时钟信号(例如HSE)经过分频或倍频(PLL)后,得到系统时钟,系统时钟经过分频,产生外设所使用的时钟。

设置时钟流程:

1、将RCC寄存器重新设置为默认值 RCC_DeInit

2、打开外部高速时钟晶振HSE RCC_HSEConfig(RCC_HSE_ON);

3、等待外部高速时钟晶振工作 HSEStartUpStatus = RCC_WaitForHSEStartUp();

4、设置AHB时钟 RCC_HCLKConfig

5、设置高速AHB时钟 RCC_PCLK2Config

6、设置低速速AHB时钟 RCC_PCLK1Config

7、设置PLL RCC_PLLConfig

8、打开PLL RCC_PLLCmd(ENABLE);

9、等待PLL工作 while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET)

10、设置系统时钟 RCC_SYSCLKConfig

11、判断是否PLL是系统时钟 while(RCC_GetSYSCLKSource()!= 0x08)

12、打开要使用的外设时钟 RCC_APB2PeriphClockCmd()/RCC_APB1PeriphClockCmd()

关于系统时钟配置分为寄存器配置和固件库配置两种:

(1)固件库配置

void RCC_Config(void)

{

RCC_DeInit(); //设置RCC寄存器默认值

RCC_HSEConfig(RCC_HSE_ON); //使能外部高速时钟HSE

while(RCC_GetFlagStatus(RCC_FLAG_HSERDY)==RESET);//等待HSE使能就绪

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);//enable prefetch buffer(开启预取指令功能,可以提高效率)

FLASH_SetLatency(FLASH_Latency_2); //flash 2 wait state

RCC_HCLKConfig(RCC_SYSCLK_Div1);//HCLK=SYSCLK

RCC_PCLK1Config(RCC_HCLK_Div2); //PCLK1=HCLK/2

RCC_PCLK2Config(RCC_HCLK_Div1); //PCLK2=HCLK

RCC_PLLConfig(RCC_PLLSource_HSE_Div1,RCC_PLLMul_9);//PLLCLK=8*9

RCC_PLLCmd(ENABLE); //enable PLLCLK

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY)==RESET);//wait till PLLCLK is ready

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);//select PLL as system clock

while(RCC_GetSYSCLKSource()!=0x08); //wait till PLL is used as system clock source

}

参考:http://blog.csdn.net/u011784994/article/details/53057736