1、搭建vivado工程。

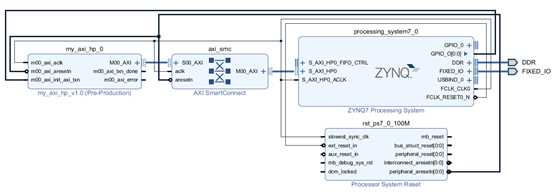

用户自建一个AXI接口,配置成AXI4、Full、Master类型。输入信号m00_axi_int_axi_txn控制内部开始数据传输。

通过axi_smc或者axi_interconnect跟PS_HP接口对接,可以实现N-1或1-N。

PS核部分配置出HP0接口,以及一个GPIO(PL扩展EMIO)来控制_axi_txn信号。

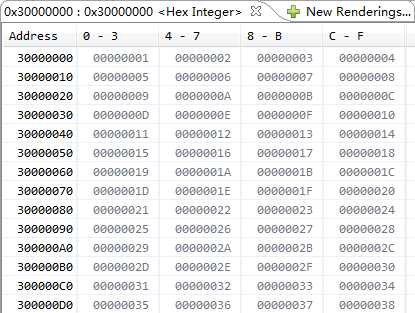

读写的起始地址设置在DDR的0x3000_0000。

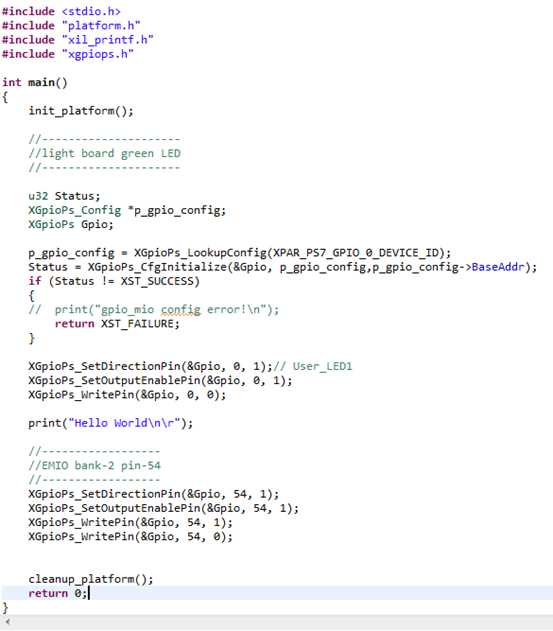

2、C代码主要是控制上面的GPIO信号。

扩展到PL侧的EMIO信号位于bank2,pin排序54。先高后低出个pulse触发信号。

3、在SDK上读到的DDR内容。

4、关于DDR地址分配

OCM-RAM0: 0x0000_0000 <-> 0x0002_FFFF

DDR (1GB): 0x0010_0000 <-> 0x3FFF_FFFF

OCM-RAM1: 0xFFFF_0000 <-> 0xFFFF_FDFF