中断是将正常的指令流运行过程转向中断服务程序。在中断处理完之后,处理器返回到原来运行的程序。

处理器状态包括寄存器状态和程序流返回地址,他们保存在特殊寄存器和通用寄存器的R28~R31中。所以有两套额外的寄存器在不同的中断等级下调出使用。

处理器有外部中断或称为硬件中断(Hwi)供其他系统单元请求处理器暂停正在执行的程序,而内部中断则发生在处理器内部。内部中断又分为异常(EXC)和软件中断(SWI)两种。

异常是指令执行过程中发生错误时自动调用的,软件中断是SWI指令调用的。

软件通过跳转到不同的中断处理程序,能够分别处理不同含义和不同优先级的中断。

硬件中断则是通过各自独立的中断序号来区分的。通过中断向量,中断处理程序的起始地址便可以计算出来。

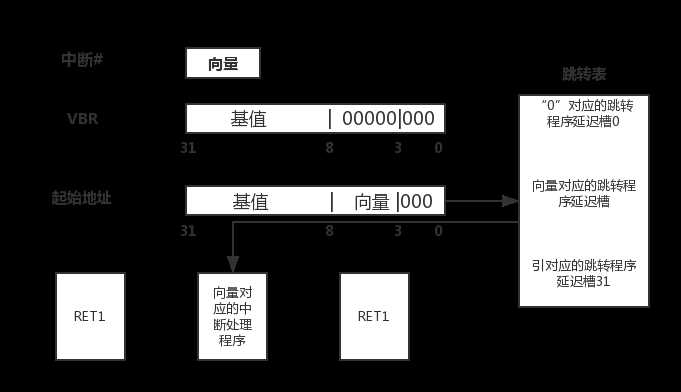

一个向量基值寄存器VBR为中断处理程序提供快速地址指示。这个指示地址是可编程的。中断号和VBR的组合便产生了中断服务程序的入口地址。

VBR寄存器的内容或基址寄存器中的内容,指示了每一个中断处理程序在存储器中的起始地址。

这个表包含了指向32个中断处理程序地址入口的跳转指令,以及包含2个字8个字节的延迟槽指令。

因此VBR寄存器的0、1和2位都是0.中断处理程序入口由5位向量表示,即为VBR的3-7位。

|

类型

|

向量

|

说明

|

| Hwi

00xxx

|

00000

00001

00010

00011

00100

00101

00110

00111

|

BUS_ERROR总线错误

PAGE_FAULT页面错误

MISS_ALIGN未对准

操作系统定义

操作系统定义

操作系统定义

操作系统定义

操作系统定义

|

| Exc

01xxx

|

01000

01001

01010

01011

01100

01101

01110

01111

|

延迟槽为CTR指令

PRIVILEGE_VIOLATION越权指令

ILLEGAL_INSTRUCTION非法指令

UNIMPLEMENTED_INSTRUCTION未实现指令

保留

保留

保留

PANIC严重错误

|

| Swi

1xxxx

|

10000

|

操作系统定义

|