LCD就是液晶显示器,分为TN、STN和TFT显示器。其中TFT显示器为主流。

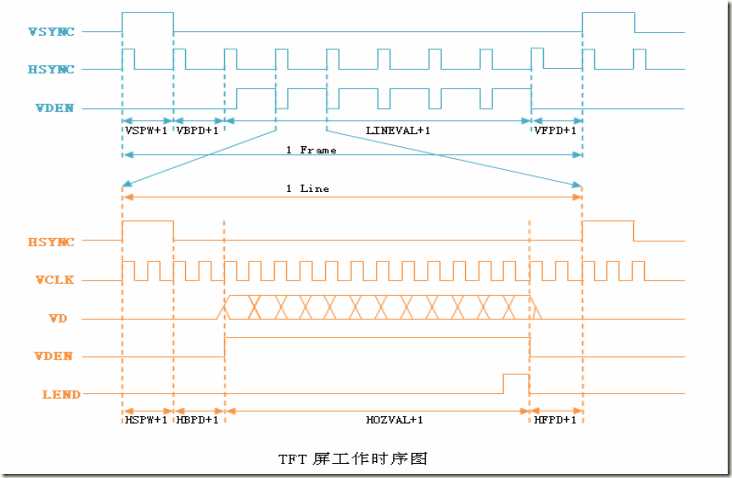

下面是TFT屏典型时序:

一副图像可以看做是一个矩形,由很多排列整齐的点一行一行的组成,这些点称之为像素。TFT屏显示图像就是从上到下,从左到右的显示这幅图像的像素。

一副图像在LCD上的显示过程:

- 显示指针从矩形左上角的第一行第一个点开始,一个点一个点的在LCD上显示,在上面的时序图中表示为VCLK,称为像素时钟信号。

- 当显示指针一直显示到矩形的右边就结束这一行,那么这一行的动作在上面的时序图中称为1 Line。

- 接下来显示指针又回到矩形的左边从第二行开始显示,注意,显示指针在从第一行的右边回到第二行的左边是需要一定的时间的,称为行切换。

- 以此类推,显示指针就这样一行一行的显示至矩形的右下角才把一副图显示完成。因此,这一行一行的显示在时间线上看,就是时序图上的HSYNC。

- 然而,LCD的显示并不是对一幅图像快速的显示一下,为了持续和稳定的在LCD上显示,就需要切换到另一幅图上(另一幅图可以和上一幅图一样或者不一样,目的只是为了将图像持续的显示在LCD上)。那么这一副一副的图像称为帧,在时序图上表示为1 Frame,因此从时序图上可以看出1 Line只是1 Frame中的一行。

- 同样的,在帧与帧切换之间也是需要一定的时间的,称为帧切换,那么LCD整个显示的过程在时间线上看,就可表示为时序图上的VSYNC。

上述时序图中各时钟参数具体含义:

|

术语 |

说明 |

|

VSYNC |

帧同步信号,每发出一个脉冲,表示新的一屏图像数据开始传送 |

|

HSYNC |

行同步信号,每发出一个脉冲,表示新的一行图像数据开始传送 |

|

VCLK |

像素时钟信号,每发出一个脉冲,表示新的一个点的图像数据开始传送 |

|

LEND |

行结束信号 |

|

VBPD |

表示在一帧图像开始时,帧同步信号以后的无效的行数,对应驱动的upper_margin |

|

VFBD |

表示在一帧图像结束后,帧同步信号以前的无限的行数,对应驱动的lower_margin |

|

VSPW |

表示垂直同步脉冲的宽度、用行数计算,对应驱动的vsync_len |

|

HBPD |

表示从水平同步信号开始到一行的有效数据开始之间的VCLK的个数,对应驱动中的left_margin |

|

HFPD |

表示一行的有效数据结束到下一个水平同步信号开始之间的VCLK的个数,对应驱动中的right_margin |

|

HSPW |

表示水平同步信号的宽度,用VCLK计算,对应驱动的hsync_len |