上拉(Pull Up )或下拉(Pull Down)电阻(两者统称为“拉电阻”)最基本的作用是:将状态不确定的信号线通过一个电阻将其箝位至高电平(上拉)或低电平(下拉),无论它的具体用法如何,这个基本的作用都是相同的,只是在不同应用场合中会对电阻的阻值要求有所不同,从而也引出了诸多新的概念,本节我们就来小谈一下这些内容。

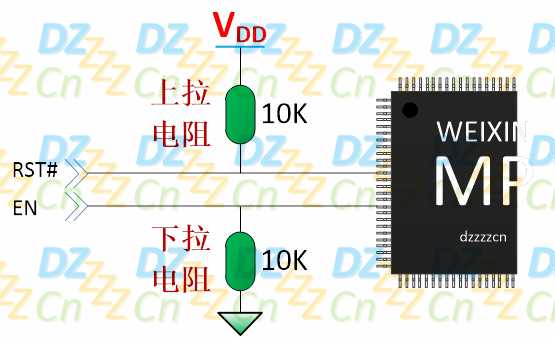

如果拉电阻用于输入信号引脚,通常的作用是将信号线强制箝位至某个电平,以防止信号线因悬空而出现不确定的状态,继而导致系统出现不期望的状态,如下图所示:

在实际应用中,10K欧姆的电阻是使用数量最多的拉电阻。需要使用上拉电阻还是下拉电阻,主要取决于电路系统本身的需要,比如,对于高有效的使能控制信号(EN), 我们希望电路系统在上电后应处于无效状态,则会使用下拉电阻。

假设这个使能信号是用来控制电机的,如果悬空的话,此信号线可能在上电后(或在运行中)受到其它噪声干扰而误触发为高电平,从而导致电机出现不期望的转动,这肯定不是我们想要的,此时可以增加一个下拉电阻。

而相应的,对于低有效的复位控制信号(RST#),我们希望上电复位后处于无效状态,则应使用上拉电阻。

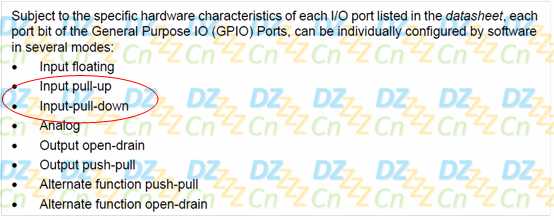

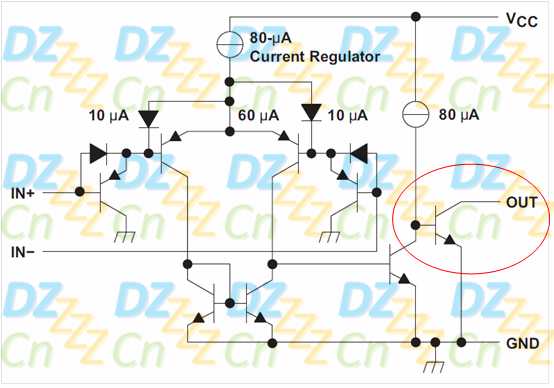

大多数具备逻辑控制功能的芯片(如单片机、FPGA等)都会集成上拉或下拉电阻,用户可根据需要选择是否打开,STM32单片机GPIO模式即包含上拉或下拉,如下图所示(来自ST数据手册):

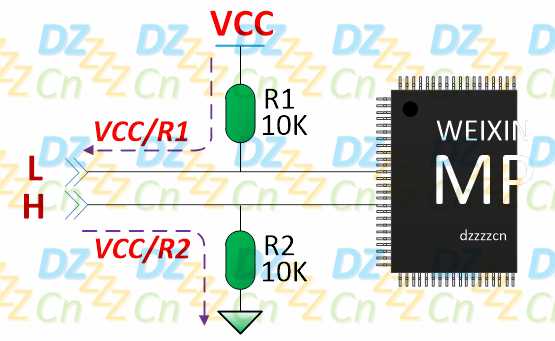

根据拉电阻的阻值大小,我们还可以分为强拉或弱拉(weak pull-up/down),芯片内部集成的拉电阻通常都是弱拉(电阻比较大),拉电阻越小则表示电平能力越强(强拉),可以抵抗外部噪声的能力也越强(也就是说,不期望出现的干扰噪声如果要更改强拉的信号电平,则需要的能量也必须相应加强),但是拉电阻越小则相应的功耗也越大,因为正常信号要改变信号线的状态也需要更多的能量,在能量消耗这一方面,拉电阻是绝不会有所偏颇的,如下图所示:

对于上拉电阻R1而言,控制信号每次拉低L都会产生VCC/R1的电流消耗(没有上拉电阻则电流为0),相应的,对于下拉电阻R2而言,控制信号每次拉高H也会产生VCC/R2R 电流消耗(本文假设高电平即为VCC)。

强拉与弱拉之间没有严格说多少欧姆是强弱的分界,一般我们使用的拉电阻都是弱拉,这样我们仍然可以使用外部控制信号将已经上/下拉的信号线根据需要进行电平的更改。

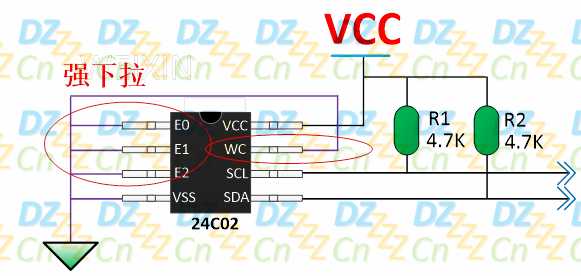

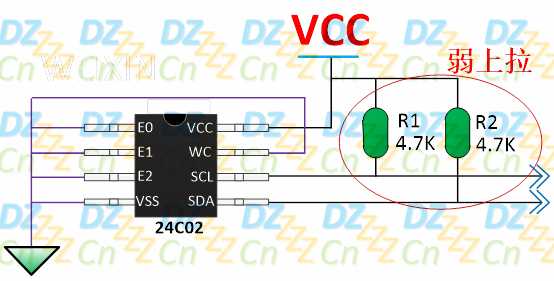

强拉电阻的极端就是零欧姆电阻,亦即将信号线直接与电源或地相连接,比如,对于EEPROM存储芯片24C02应用电路,如下图所示:

其中,E0,E1,E2(地址配置位)在应用中通常都是直接强上拉到电源VCC,或强下拉到GND,因为存储芯片的地址在系统运行过程中是不会再发生变化的,同样,芯片的写控制引脚WC(Write Control)也被强下拉到GND。

拉电阻作为输出(或输入输出)时牵涉到的知识点会更多一些,但本质的功能也是将电平箝位,最常见的输出上拉电阻出现在开集(Open Collector,OC)或开漏(Open Drain,OD)结构的引脚。

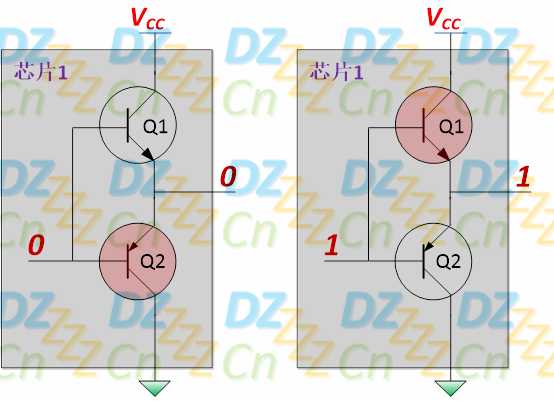

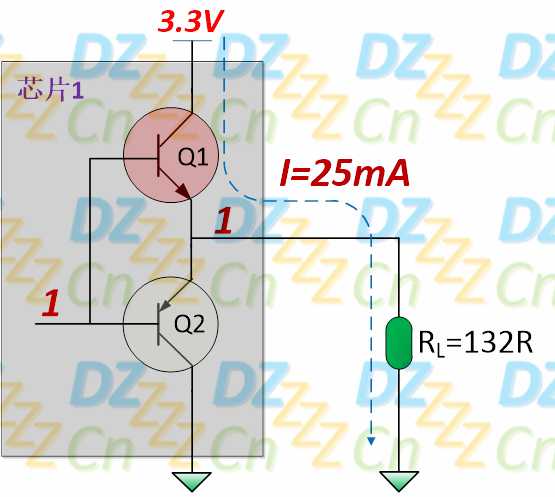

我们有很多芯片的输出引脚是推挽输出结构(Output Push-Pull),如下图所示(还有一种反相输出的结构,本质也是一样的):

推挽输出结构引脚的特点是:无论引脚输出高电平“H”还是低电平“L”,都有比较强的驱动能力(输入或输出电流能力)!

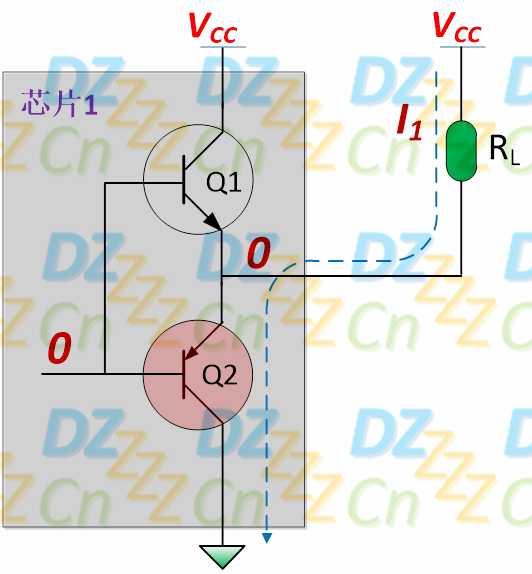

当推挽输出结构的控制信号为低电平“L”时,Q1截止Q2导通,电流I1由电源VCC经负载RL与三极管Q2流向公共地,我们称此电流为灌电流(Sink Current),也就是外部电流灌入芯片内部,如下图所示:

相应的,当推挽输出结构的控制信号为高电平“H”时,Q1导通Q2截止,电流I1由电源VCC经三极管Q1与负载RL流向公共地,我们称此电流为拉电流(Source Current),也就是芯片内部可以向外提供的电流(所以称之为“源电源”),从另一个角度讲,也就是外电路可以从芯片中拉走多少电流,如下图所示:

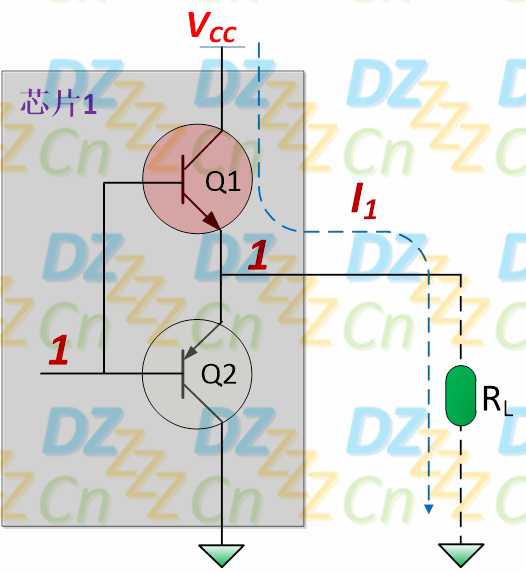

灌电流能力与拉电流能力也称为芯片引脚的驱动能力。对于任何给定的芯片,引脚的驱动能力都是有限的,如下图所示为STM32单片机的IO引脚电流驱动能力(来自ST数据手册):

由上表可知,STM32的IO引脚的驱动能力为25mA,负号“-”表示电流的方向,灌与拉的电流方向是相反的(表中SUNK为SINK的过去分词)

由于芯片引脚的驱动能力都是有限的,如果引脚驱动的负载比较重,将可能导致输出电平不正确(无法输出预定的电平),如下图所示:

假定芯片的供电电压为3.3V(忽略晶体管饱和压降),则输出最大电流25mA时,负载RL的值约为132欧姆(3.3V/25mA),如果负载值小于132欧姆,则相应输出电流会更大(超过25mA),但是芯片引脚只能提供最大25mA的电流,因此,输出电平将会下降(老板你只给我2500月薪,我就只能干2500的活,你要我干更多的活得开更多的工资,一个道理)

一般情况下,这种驱动重负载(小电阻)的电路连接是不会烧毁内部晶体管的,因为内部也是有限流电阻的,换句话讲,就算输出引脚对地短路,输出电流也不会超过最大的驱动能力(除非是不正规的芯片),当然,在实际应用过程中尽量不要超出引脚的驱动能力。

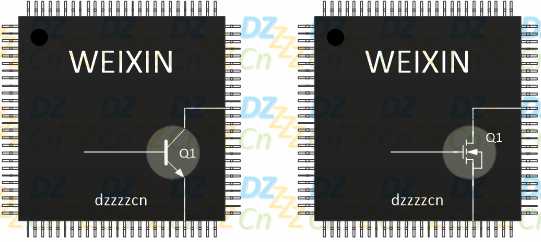

而OC(OD)的引脚输出结构有所不同(OC结构存在于三极管,而OD结构存在于场效管,下面以OC输出结构为例,OD输出结构的原理是一致的),如下图所示:

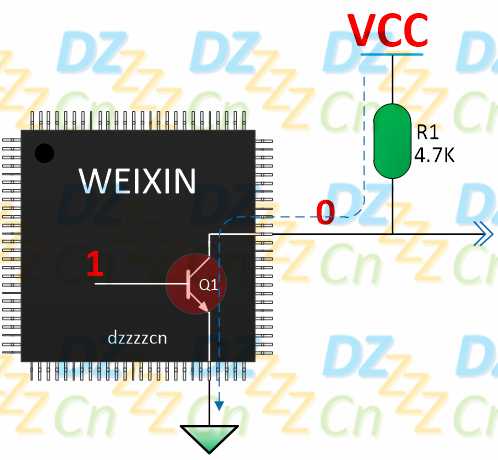

当三极管Q1的驱动控制信号为高电平“H”时,Q1饱和导通,将对应输出引脚拉为低电平“L”,如下图所示:

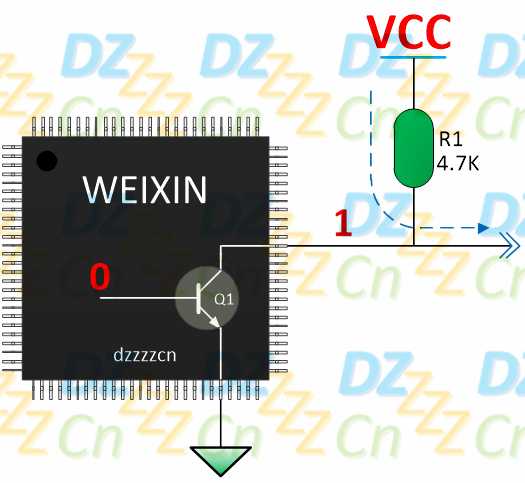

但是当控制驱动信号为低电平“L”时,三极管Q1截止,如果没有外部上拉电阻的话,该引脚相当于悬空(高阻态),无法输出高电平,也就是说,OC/OD结构输出的引脚没有拉电流(向外部电路提供电流)能力。因此,我们通常都会将OC/OD引脚通过外接电阻上拉到电源电压VCC,这样引脚输出高电平时的拉电流就直接由电源VCC提供,如下图所示:

大多数比较器芯片的输出都是OD/OC输出结构,如下图所示(来自TI比较器LM393数据手册):

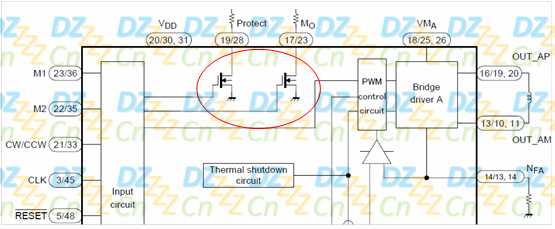

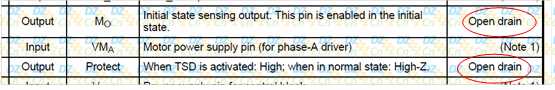

很多芯片或模块向外反馈系统状态的信号引脚也是这种结构,这样用户就可以根据电路系统实际需要将电平上拉到对应的电源电压VCC,就可以省略电平转换了,如下图所示(来自东芝步进电机控制芯片TB6560数据手册):

I2C(Inter Integrated Circuit,内部集成电路)总线也是典型的OD输出结构的应用,如下图所示:

其中,SCL与SDA都是OD输出结构输出,这样的好处是可以作为双向数据总线(也称“线或Wire-OR”功能)。

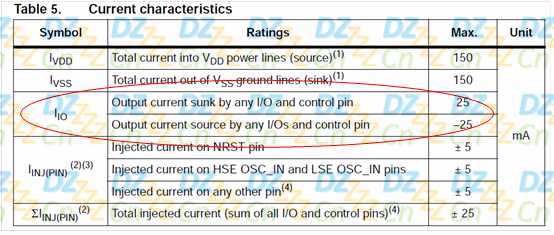

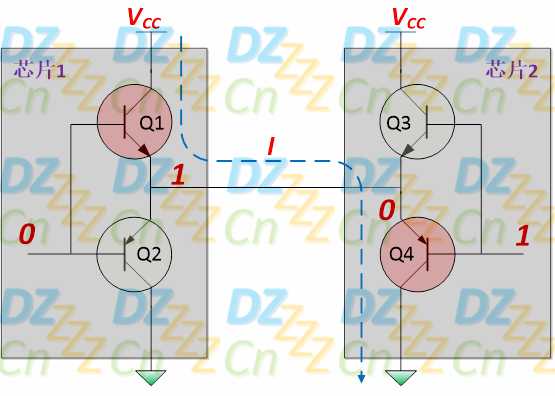

如果芯片引脚使用之前描述的推挽结构,则两个或多个芯片的引脚连接时将如下图所示:

假设如上图所示芯片的输出分别为0与1,则两者直接相互连接后,会有非常大的电流自电源VCC经Q1与Q4到公共地,虽然大多数情况下不至于烧芯片,但也会引起很大的功率消耗,同时也会导致数据冲突(芯片1总会试图将数据线拉高,而芯片2则会试图将数据线拉低,我们称之为数据冲突或总线冲突,表示双方都在抢占总线)

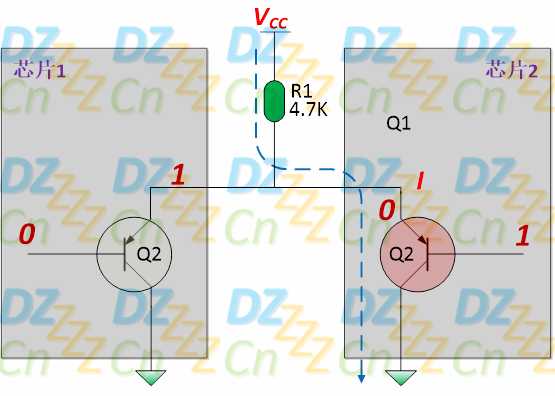

如果使用OC/OD输出结构,则相应的电路如下图所示:

此时,无论两个芯片的引脚输出什么状态,都不会引起数据冲突,配合各自芯片内部的数据识别电路及仲裁系统,双方都可以主动给另一方发送信息,也就是说,任何一方都可以将信号线拉高或拉低,而不会影响起数据冲突。

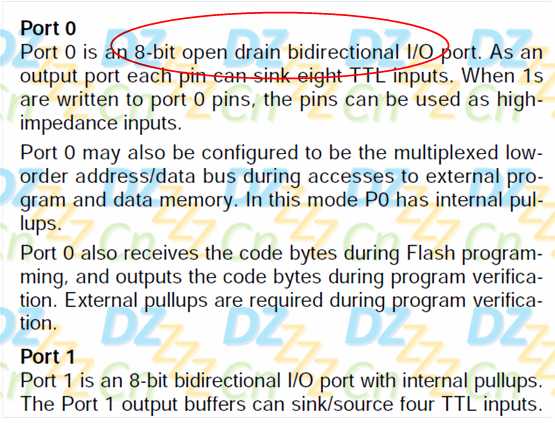

我们所熟悉的51单片机P0口也是OD结构,如下图所示(来自ATMEL单片机AT89C51数据手册):

这样我们可以使用同一个P0口,再配合多个片选信号即可访问多个外挂的存储芯片。

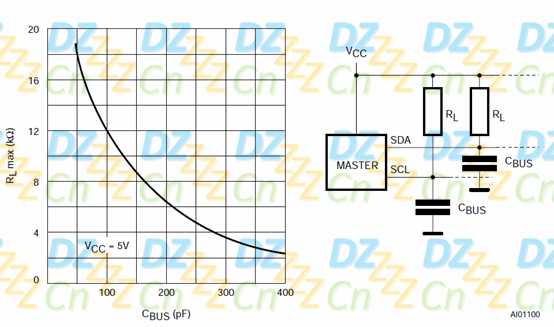

前面所述上拉电阻的阻值对输入引脚引起的功耗同样适用于输出拉电阻,因此拉电阻不宜太小,但在输出信号速度比较快的电路下,拉电阻也不宜太大,如下图所示为I2C总线上拉电阻的参考最大值(来自ST存储芯片 AT24C02数据手册)。

在总线上总会有些杂散电容CBUS,这些电容与上拉电阻RL形成了一个RC充放电电路,上拉电阻越大则充放电常数越大,这样会把原先比较陡峭的数据边沿变得平缓,如下图所示:

严重的情况下将导致数据无法正常识别,这样我们只能进一步优化电路参路,或降低通讯的速率。

拉电阻还有其它作用,我们留待下一节再继续讲解。