作者:桂。

时间:2018-02-05 19:36:08

链接:http://www.cnblogs.com/xingshansi/p/8419182.html

一、概述

本文简要记录FIR的小trick,主要参考:

Shen, Zhi. “Improving FIR Filter Coefficient Precision [DSP Tips & Tricks].” IEEE Signal Processing Magazine 27 (2010): 120-124.

全文主要分两种实现结构:

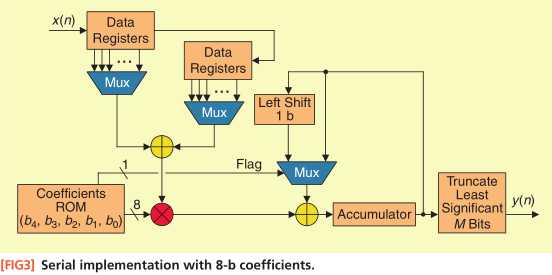

1)serial method.主要借助标志位flag,结合依次递减的无效位,利用移位寄存器实现。

2)parallel method. serial method需要借助额外的标志位flag,增加了开销,parallel 则仅借助输出的幅度范围进行移位,一方面无需标志位,另一方面也不必逐一递减,增大了无效位宽,进一步提高滤波器精度。

二、算法简述

A-serial method

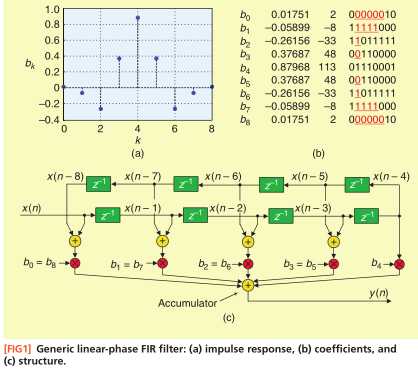

传统FIR滤波器:

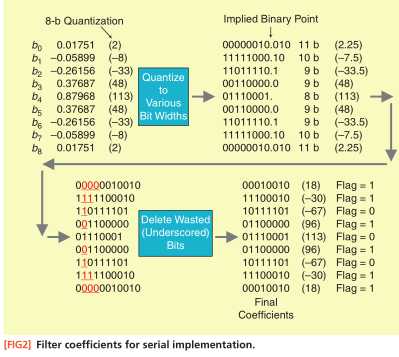

可以看到越到两边,滤波器的幅值越小,从而无效位越多。剔除一部分无效位,结合FLAG:

具体实现结构:

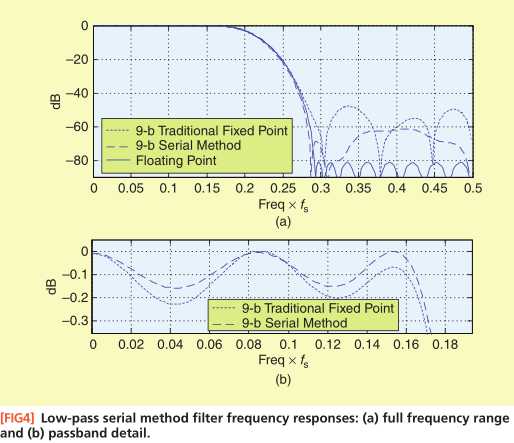

不增加位宽、不增加滤波器阶数,性能还不错,idea不错!

B-parallel method

滤波器系数压缩:

可以看出系数是越来越小,利用这个特性:

具体操作流程:

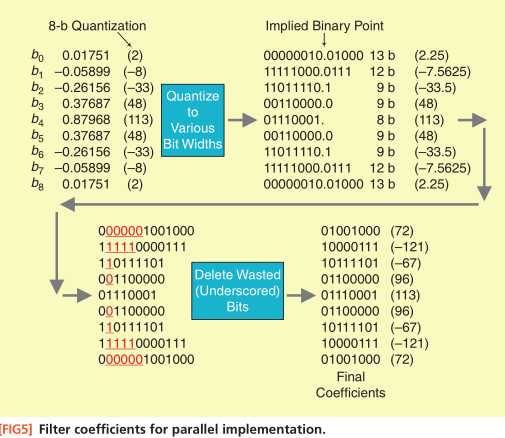

Step 1 ■ : Repeatedly multiply an original b k floating-point coefficient (the upper left side of Figure 5) by two until the magnitude of the result resides in the optimum magnitude range R. Denote the number of necessary multiply-by-two operations as Q.

Step 2 ■ : Multiply the original bk floating-point coefficient by 2 B+Q-1 (the minus one in the exponent accounts for the final coefficient’s sign bit) and round the result to the nearest integer. That integer is our final value saved in ROM.

Step 3 ■ : Repeat Steps 1 and 2 for all the remaining original bk floating-point coefficients.

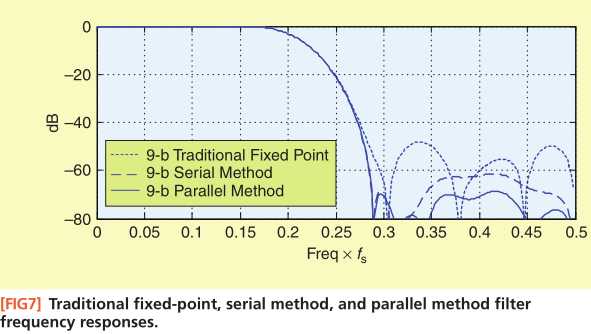

符合预期,效果进一步提升:

对于传统FPGA,25x15的DSP48精度足够,该算法对于微芯片可能起一定作用,对于快速处理的FPGA平台个人认为意义不大。