一、综述

参考ug474.pdf:

.png)

二、主要功能

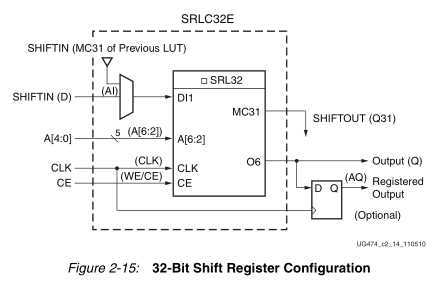

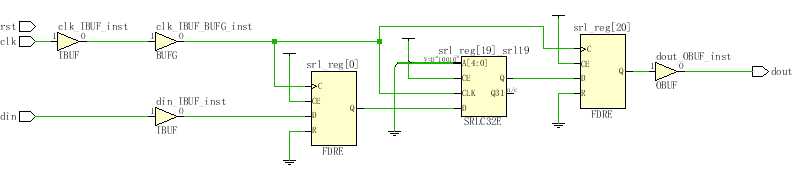

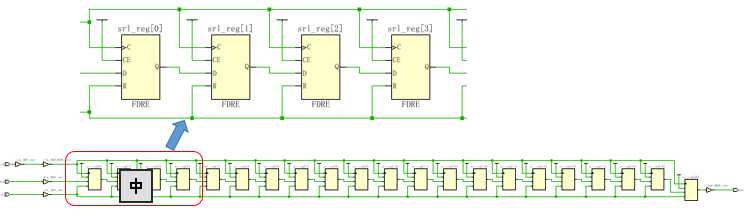

always @(posedge clk)

srl <= {srl[31:0],din};

assign dout = srl[20];

当添加复位信号:

always@ (posedge clk)

if(rst)

srl <= 32‘d0;

else

srl <= {srl[31:0],din]};

assign dout = srl[20]

为什么结构不一致?因为LUT没有同步复位控制输入端,因此综合器无法将代码综合成有LUT实现的结构,因此写代码需要根据相应结构编写。

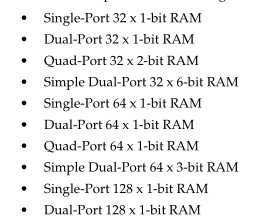

以下列举了一些适用于分布式RAM的情况:

1. 深度小于64-bit

2. 在深度大于64-bit小于128-bit情况下,有时延要求并需要异步输出(其clock-to-out时间小,并且布线比Block RAM自由)

3. 数据宽度小于16-bit

(个人观点:这里配置RAM调用FPGA内部逻辑资源,而Block RAM blocks内部的RAM只能作为RAM使用,因此在时序没有要求,且固定RAM容量有剩余的情况下,不建议配置CLB中的RAM,固定RAM容量不够,可用CLB配置作为补充)。

CLB还有一个重要功能:多路复用器(multiplexer)。

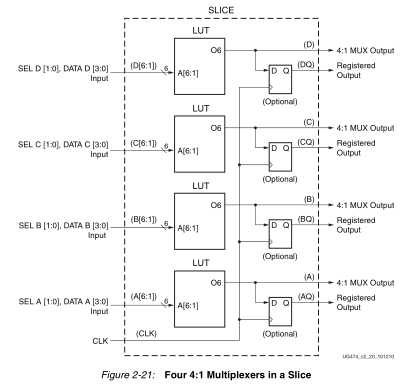

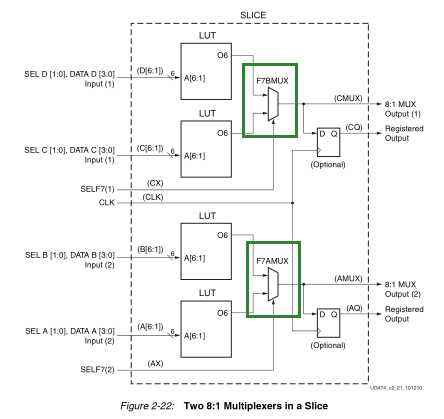

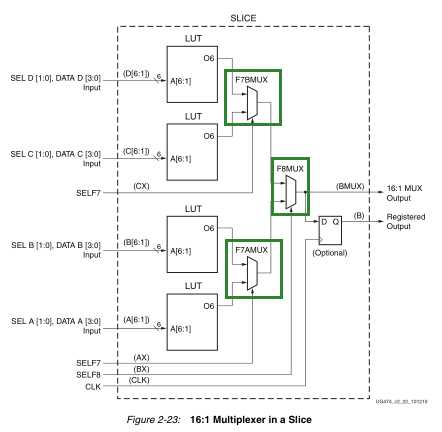

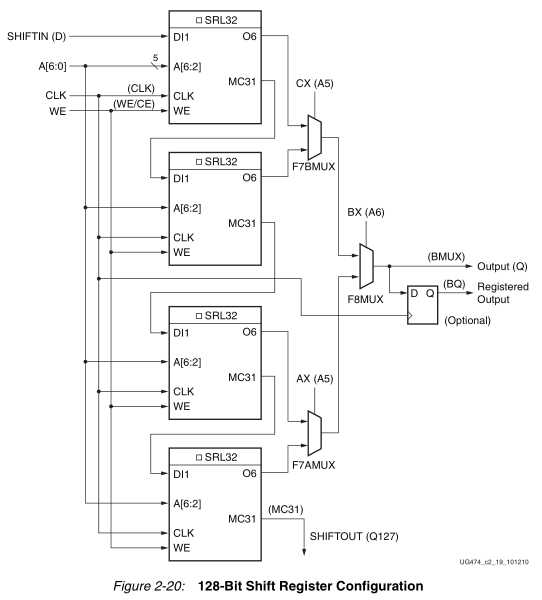

在一个Slice中包含有三个多路复用器:F7MUXA、F7MUXB和F8MUX。其中F7MUXA组合LUT A和LUT B成为7输入LUT,F7MUXB组合LUT C和LUT D成为7输入LUT,而F8MUX组合1个Slice中的4个LUT成为8输入LUT。因此通过F7MUXA、F7MUXB和F8MUX的搭配,1个Slice可以实现4:1、8:1和16:1多路复用器,如图1、2、3所示。