S5PV210 时钟体系

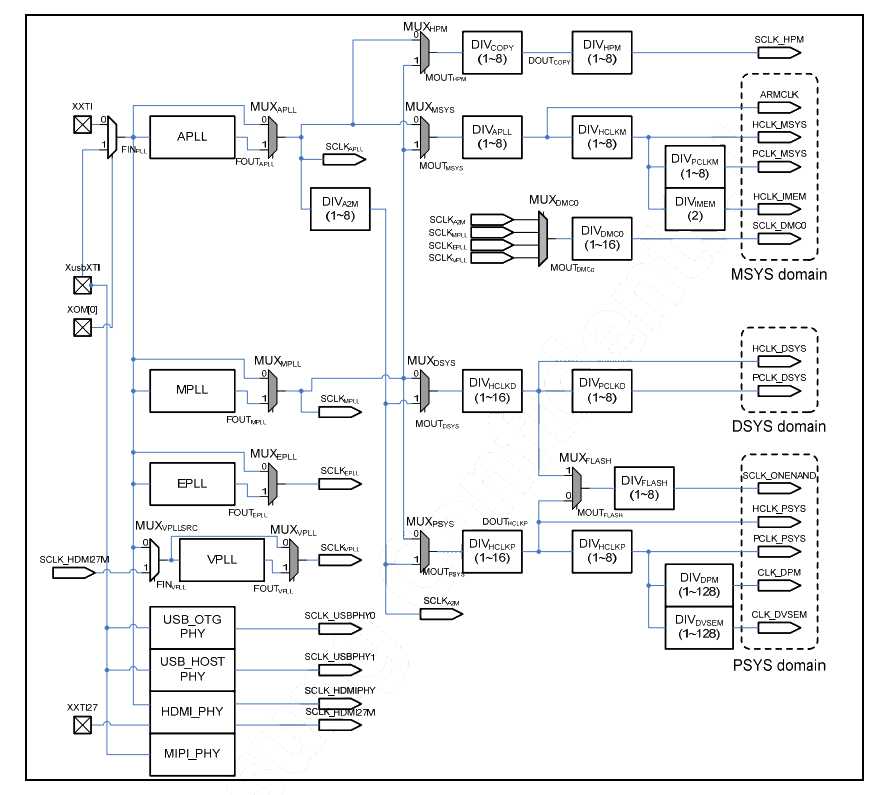

如下面时钟结构图所示,S5PV210 中包含 3 大类时钟域, 分别是主系统时钟域(简称 MSYS)、显示相关的时钟域(简称 DSYS)、 外围设备的时钟域(简称 PSYS)。

1) MSYS:用来给 cortex a8 处理器、DRAM 控制器、3D、IRAM、IROM、INTC(中断控制器)等提供时钟;

2) DSYS:用来给显示相关的部件提供时钟,包括 FIMC、FIMD、JPEG 和 multimedia IPs;

3) PSYS:用来给外围设备提供时钟,如 i2s、spi、i2c、uart 等。Mini210S 外接的晶振频率(简称 Fin)为 24MHz,通过时钟控制逻辑 PLL 可以提高系统时钟。

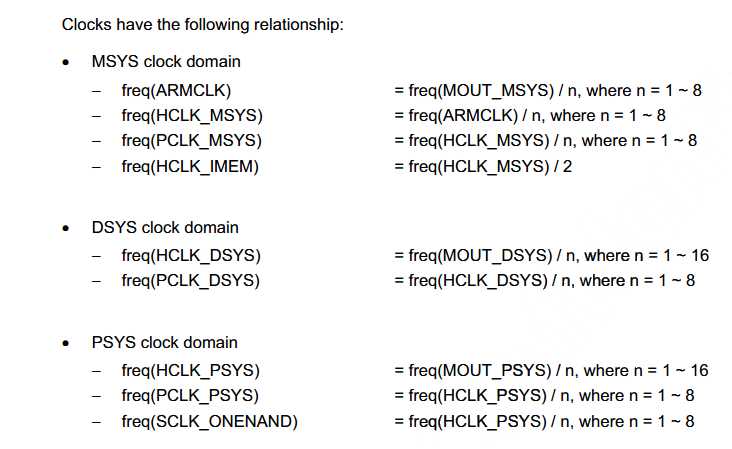

S5PV210 共有 4 个倍频器,即 PLL, 包括 APLL(供 MSYS 使用),MPLL(供 DSYS 使用),EPLL(供 PSYS使用),VPLL(供 video 相关的时钟使用)。 3 大类时钟域中,可以使用不同的分频,使其给不同部件输出所需要的时钟,各类时钟的关系如下图:

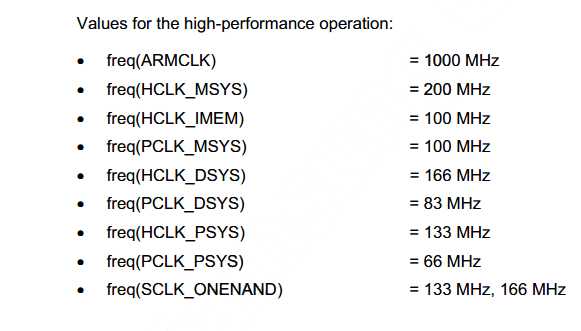

芯片手册上给出了参考值, 我们按照参考值设置即可, 各类时钟的参考值如下图:

时钟初始化程序

#define APLL_MDIV 0x7d

#define APLL_PDIV 0x3

#define APLL_SDIV 0x1

#define MPLL_MDIV 0x29b

#define MPLL_PDIV 0xc

#define MPLL_SDIV 0x1

#define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv)

#define APLL_VAL set_pll(APLL_MDIV,APLL_PDIV,APLL_SDIV)

#define MPLL_VAL set_pll(MPLL_MDIV,MPLL_PDIV,MPLL_SDIV)

void clock_init()

{

/* 1 设置各种时钟开关, 暂时不使用 PLL */

CLK_SRC0 = 0x0;

/* 2 设置锁定时间,使用默认值即可 */

APLL_LOCK = 0x0000FFFF;

MPLL_LOCK = 0x0000FFFF;

/* 3 设置分频 */

CLK_DIV0 = 0x14131440;

/* 4 设置 PLL */

APLL_CON0 = APLL_VAL;

MPLL_CON = MPLL_VAL;

/* 5 设置各种时钟开关,启用 PLL */

CLK_SRC0 = 0x10001111;

}程序分析:

第一步 设置各种时钟开关,暂时不使用 PLL

在未设置 PLL 和各种分频系数之前,我们不能使用 PLL, 为了保险起见, 暂时直接使用频率较低的外接的 24MHz 晶振,待设置好 PLL 和分频系数后再重新设置各种时钟开关。

第二步 设置锁定时间

设置 PLL 后,时钟从 Fin 提升到目标频率时,需要一定的时间,即锁定时间,使用默认值即可。

第三步 设置分频

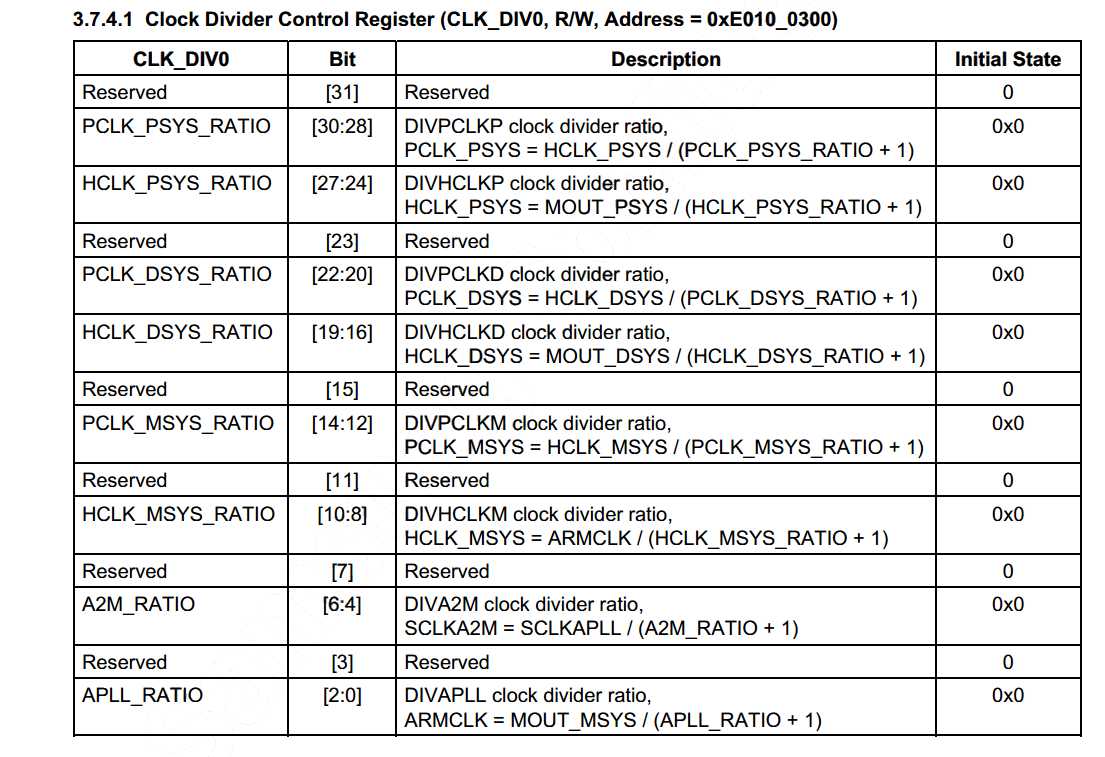

与分频相关的寄存器是 CLK_DIV0,见下图:

根据手册中给出的参考值来设置该寄存器。

ARMCLK = 1000MHz = MOUT_MSYS / (APLL_RATIO + 1),经过在第四和第五步的设置后, MOUT_MSYS会被设置为 1000MHz,所以 APLL_RATIO=0 即可

SCLKA2M = 200MHz = SCLKAPLL / (A2M_RATIO + 1),由于 SCLKAPLL = 1000MHz,所以 A2M_RATIO=4。

HCLK_MSYS = 200MHz = ARMCLK / (HCLK_MSYS_RATIO + 1),所以 HCLK_MSYS_RATIO=4

PCLK_MSYS = 100MHz = HCLK_MSYS / (PCLK_MSYS_RATIO + 1),所以 PCLK_MSYS_RATIO=1

HCLK_DSYS = 166MHz = MOUT_DSYS / (HCLK_DSYS_RATIO + 1), 经过在第四和第五步的设置后,MOUT_DSYS =667MHz, 所以 HCLK_DSYS_RATIO=3

PCLK_DSYS = 83MHz = HCLK_DSYS / (PCLK_DSYS_RATIO + 1),所以 PCLK_DSYS_RATIO=1

HCLK_PSYS = 133Mhz = MOUT_PSYS / (HCLK_PSYS_RATIO + 1), 经过在第四和第五步的设置后,MOUT_PSYS =667MHz 所以 HCLK_PSYS_RATIO=4

PCLK_PSYS = 66Mhz = HCLK_PSYS / (PCLK_PSYS_RATIO + 1), 所以 HCLK_PSYS_RATIO=1第四步 设置 PLL

PLL 即倍频器,用来放大运行频率。 设置好分频后,我们就需要设置 PLL 了。 APLL 和 MPLL 的启动是通过分别设置 APLL_CON0 和 MPLL_CON 寄存器,我们逐个来设置。

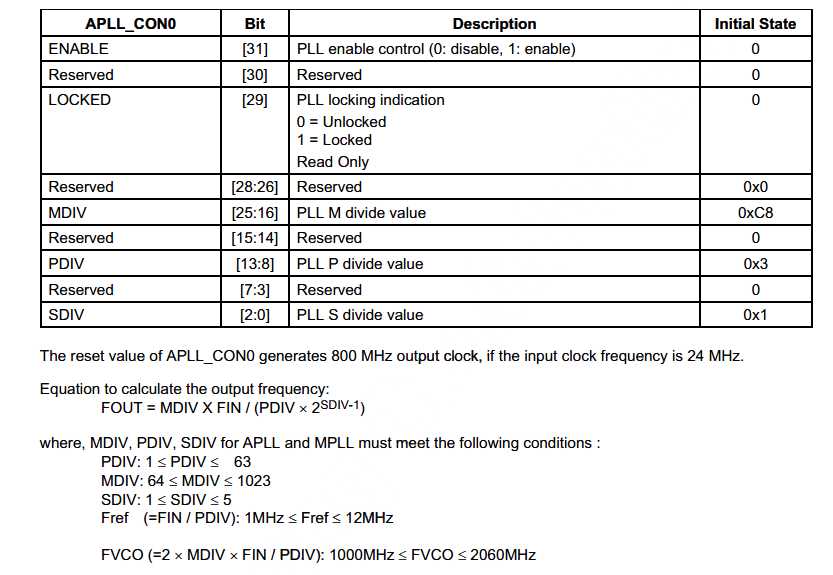

APLL_CON0

APLL_CON0 负责设置 APLL, FINPLL=24MHz,经过 APLL 后,我们将输出 FOUT=1000Mhz 的时钟频率, FOUT 的计算公式如下:

FOUT=MDIV*FIN/(PDIV*2^(SDIV-1)) = 1000 MHz由于 FIN=24MHz,FOUT=1000MHz,我们可以这样取值: MDIV= 0x7d, PDIV= 0x3, SDIV=1。这 3 个值并不是固定死的,只要能使 FOUT=1000Mhz,任意搭配都是可以的。

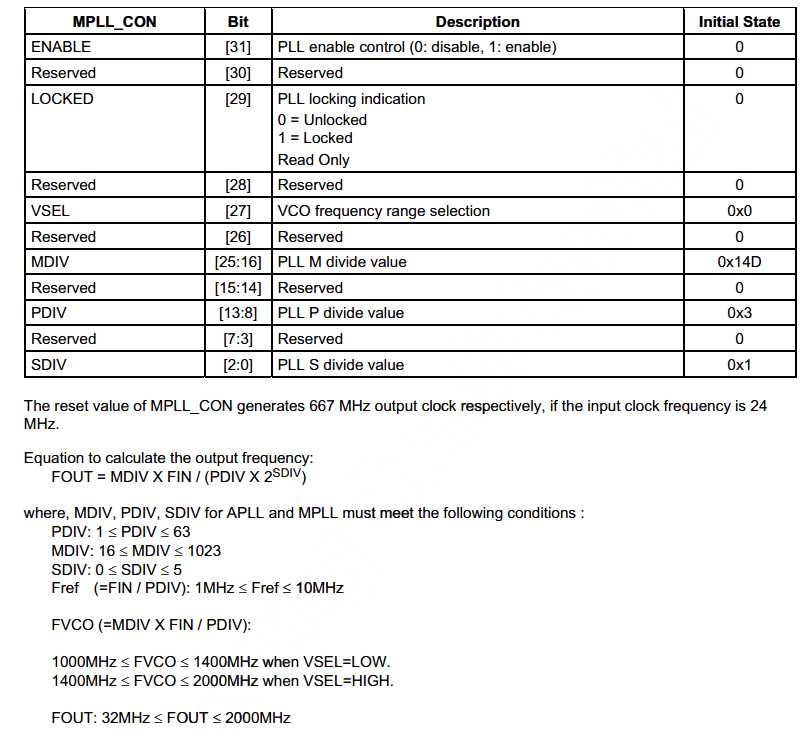

MPLL_CON

MPLL_CON 寄存器负责设置 MPLL,经过 MPLL 后,我们将输出 FOUT=667Mhz 的时钟频率, FOUT 的计算公式如下:

FOUT=MDIV*FIN/(PDIV*2^SDIV) = 667 MHz由于 FIN=24MHz,FOUT=667MHz,我们可以这样取值: MDIV=0x29B,PDIV= 0xC, SDIV=1。这 3 个值并不是固定死的,只要能使 FOUT=667Mhz,任意搭配都是可以的。

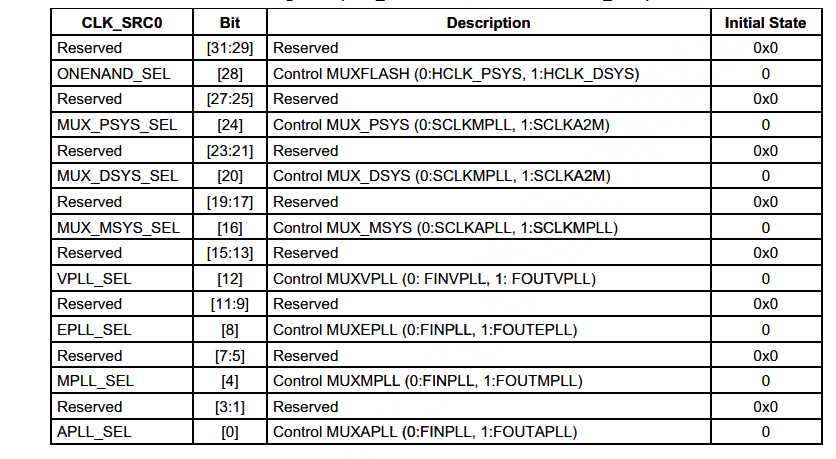

第五步 设置各种时钟开关

参考 S5PV210 时钟结构图,设置各种时钟开关:

APLL_SEL = 1,使用 FOUTAPLL

MPLL_SEL = 1,使用 FOUTMPLL

EPLL_SEL = 1, 使用 FOUTEPLL

VPLL_SEL = 1,使用 FOUTVPLL

MUX_MSYS_SEL = 0, 使用 SCLKAPLL

MUX_DSYS_SEL = 0, 使用 SCLKMPLL

MUX_PSYS_SEL = 0,使用 SCLKMPLL

ONENAND_SEL = 1, 使用 HCLK_DSYS

所以 CLK_SRC0 = 0x10001111;以上程序,通过设置时钟相关的寄存器,达到了初始化时钟的目的(实际上我们并不需要设置好所有部件的工作时钟,我们只需设置好我们需要使用的硬件部件的工作时钟即可)。

本篇文章参考:《友善之臂210手册》