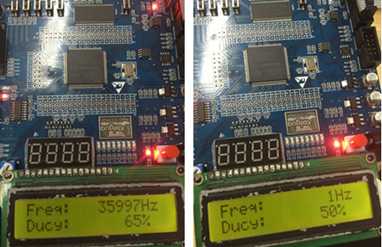

(2)频率测量1-10MHz以及占空比10%-99% 精确到1%;

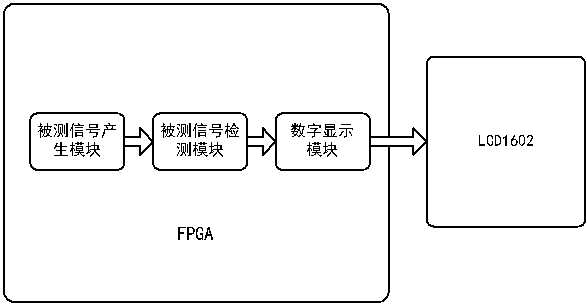

FPGA设计主要分为三个大模块来设计:1.被测信号产生模块;2.被测信号检测模块;3.数字显示模块。设计框图如图 1所示。

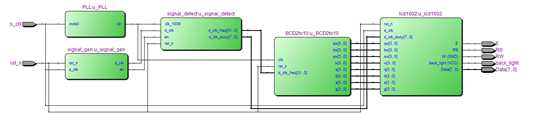

该模块主要是用来产生被测信号,可以在模块中设置被测信号的频率和占空比。采用的方法是对系统时钟进行计数分频产生被测信号。这部分也采用了一个PLL,输出一个100MHz的时钟作为检测模块的采样时钟。该部分涉及的模块:signal_gen模块和PLL模块。

检测被测信号的占空比,利用系统时钟,在外部使能信号有效时(即一段时间内),计数被测信号的正脉宽数Np和负脉宽数Nn,则占空比ducy=Np/(Np+Nn)*100%。