基于FPGA的AD0832

芯片特点

ADC0832 具有以下特点:

- 8 位分辨率;

- 双通道 A/D 转换;

- 输入输出电平与 TTL/CMOS 相兼容;

- 5V 电源供电时输入电压在 0~5V 之间;

- 工作频率为 250KHZ,转换时间为 32μS;

- 一般功耗仅为 15mW;

- 8P、14P—DIP(双列直插) 、PICC 多种封装;

- 商用级芯片温宽为0°C to +70°C,工业级芯片温宽为?40°C to +85°C;

芯片引脚

芯片接口说明

- CS_ 片选使能,低电平芯片使能。

- CH0 模拟输入通道 0,或作为 IN+/-使用。

- CH1 模拟输入通道 1,或作为 IN+/-使用。

- GND 芯片参考 0 电位(地) 。

- DI 数据信号输入,选择通道控制。

- DO 数据信号输出,转换数据输出。

- CLK 芯片时钟输入。

- Vcc/REF 电源输入及参考电压输入(复用)

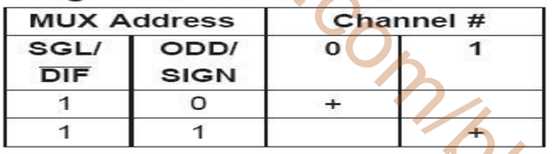

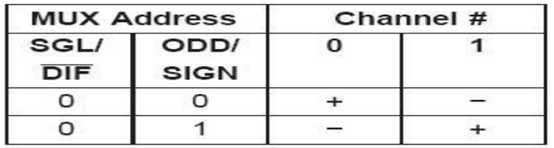

芯片通道选择

当 ADC0832 未工作时其 CS 输入端应为高电平,此时芯片禁用,CLK 和DO/DI 的电平可任意。当要进行 A/D 转换时,须先将 CS 使能端置于低电平并且保持低电平直到转换完全结束。此时芯片开始转换工作,同时由处理器向芯片时钟输入端 CLK 输入时钟脉冲,DO/DI 端则使用 DI 端输入通道功能选择的 数据信号。在第 1 个时钟脉冲的下沉之前 DI 端必须是高电平,表示启始信号。 在第 2、3 个脉冲下沉之前 DI 端应输入 2 位数据用于选择通道功能,其功能项:

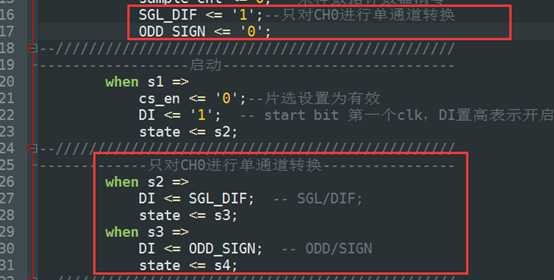

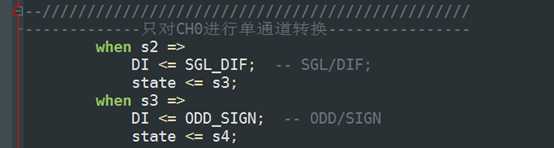

- 当2位数据为"1""0"时,只对CH0进行单通道转换;

- 当2位数据为"1""1"时,只对CH1进行单通道转;

- 当2位数据为"0""0"时,将CH0作为正输入端IN+,CH1作为负入端IN-进行输入;

- 当2位数据为"0""1"时,将CH0作为负输入端IN-,CH1 作为正输入端IN+进行输入;

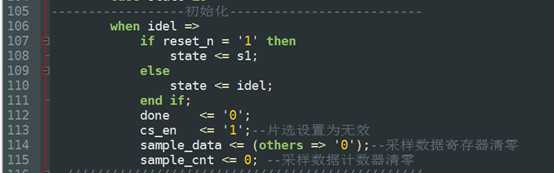

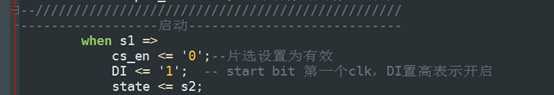

本设计采用第一种工作模式,代码设置如下图所示:

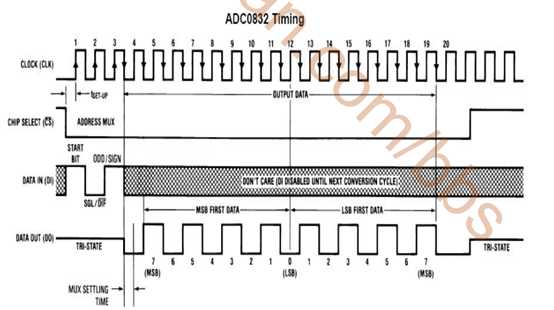

芯片时序

当要进行A/D转换时,须先将CS使能端置于低电平并且保持低电平直到转换完全结束,同时由处理器向芯片时钟输入端CLK输入时钟脉冲,

- 在第1个时钟脉冲的下沉之前DI端必须是高电平,表示启始信号;

- 在第2、3个脉冲下沉之前DI端应输入2位数据用于选择通道功能;

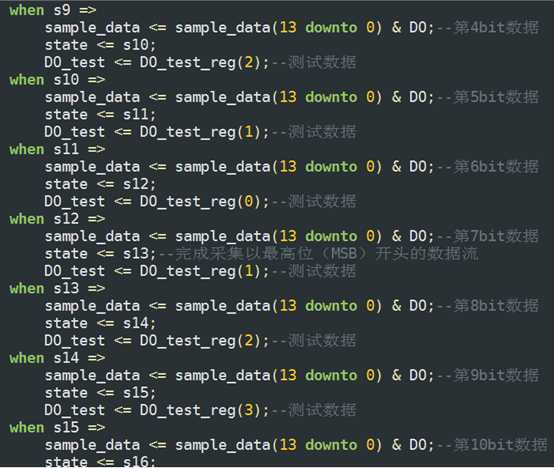

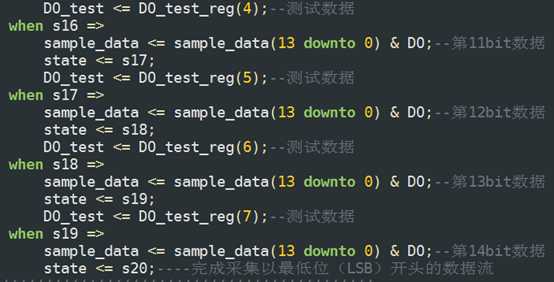

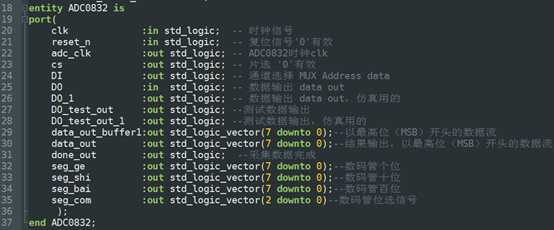

- 在第4个脉冲下沉开始由DO端输出转换数据最高位DATA7,随后每一个脉冲下沉DO端输出下一位数据,直到第11个脉冲时发出最低位数据DATA0,一个字节的数据输出完成;

- 也正是从此位开始输出下一个相反字节的数据,即从第11个脉冲的下沉输出DATD0,随后输出8位数据,到第19个脉冲时数据输出完成,也标志着一次 A/D 转换的结束;

- 最后将CS置高电平,禁用芯片,直接将转换后的数据进行处理就可以了。

注意:通常ADC0832在输出以最高位(MSB)开头的数据流后,会以最低位(LSB)开头重输出一遍(前面的数据流)。

因此,编程时要发两轮脉冲,第一次取数据,第二次若不要从低到高的数据,也必须要发一轮8 个脉冲将0832中寄存器的数据移出。

芯片驱动

本设计采用状态机进行设计:

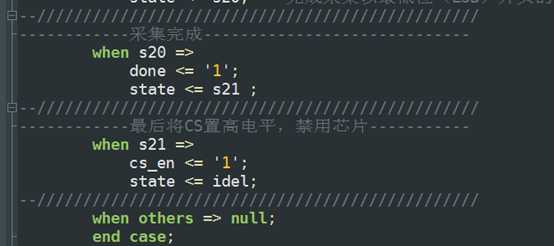

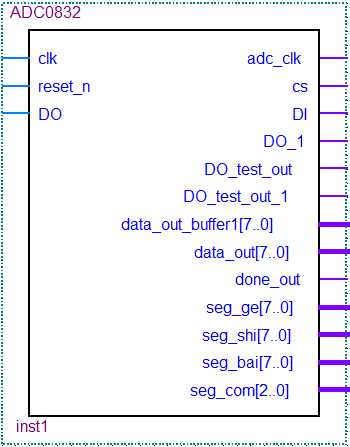

顶层接口

顶层原理图

顶层代码接口

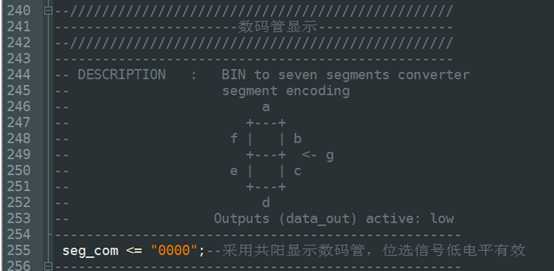

数码管显示原理

位选信号

本设计采用共阳数码管,即位选低电平有效,需要使用3位数码管显示3位的学号,所以需要位宽为3bit的位选信号,并且将位选信号设置为低电平;

段选信号

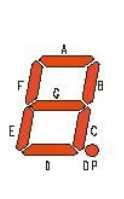

本设计采用共阳数码管,数码管的段选信号为8bit,数码管的段选对应实物图如下:

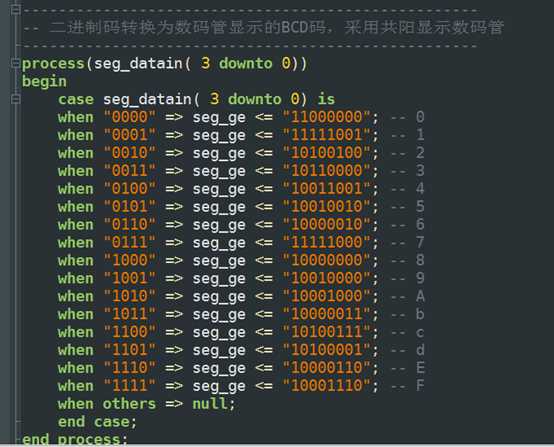

一个数码管有八段:A,B,C,D,E,F ,G,H,DP,即由八个发光二极管组成,; 因为发光二极管导通的方向是一定的(导通电压一般取为1.7V),这八个发光二极管的公共端有两种: +5V(即为共阳极数码管)、接地(即为共阴极数码管),其中共阳极每个段均有0导通,而共阴极则1导通发光,所以共阳极数码管和共阴极数码管显然是不同的,段选码表如下图所示:

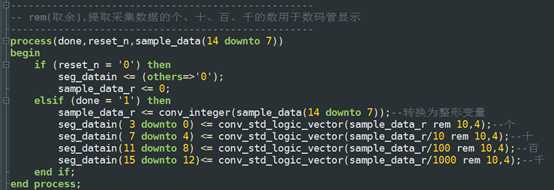

由于采集ADC0832的数据位8bit二进制数据,而数码管显示位3位数码管,所以在进行BCD转换之前需要先提取出8bit数据的个、十、百这三个位,然后再进行BCD码转换。

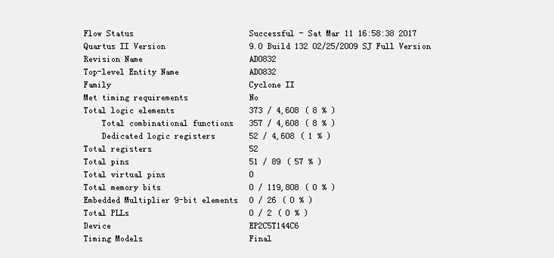

编译报告

本设计使用的逻辑单元数量为373个,只占用到所选器件EP2C5T144C6所有逻辑单元总数的8%。

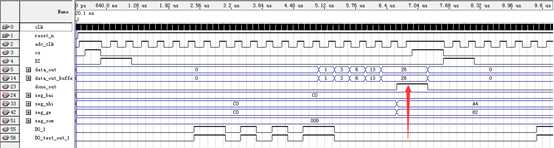

仿真图

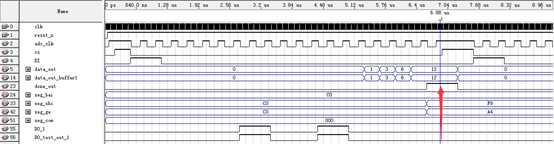

学号012

图中红色箭头所指的信号done_out为高电平,表示采集ADC0832的8位数据已经完成,data_out信号输出采集结果为12,同时,可以读出进行提取个位、十位、百位的二进制数,然后进行转换为数码管显示需要的BCD码,通过仿真结果图可以看出:

个位对应的十六进制数为:A4-----------数码管显示字型:2

十位对应的十六进制数为:F9-----------数码管显示字型:1

百位对应的十六进制数为:C0-----------数码管显示字型:0

根据段选码表如下图所示:

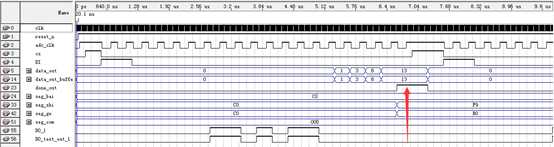

学号013

图中红色箭头所指的信号done_out为高电平,表示采集ADC0832的8位数据已经完成,data_out信号输出采集结果为13,同时,可以读出进行提取个位、十位、百位的二进制数,然后进行转换为数码管显示需要的BCD码,通过仿真结果图可以看出:

个位对应的十六进制数为:B0-----------数码管显示字型:3

十位对应的十六进制数为:F9-----------数码管显示字型:1

百位对应的十六进制数为:C0-----------数码管显示字型:0

根据段选码表如下图所示:

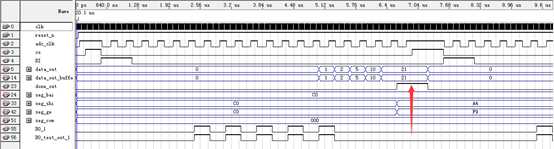

学号021

图中红色箭头所指的信号done_out为高电平,表示采集ADC0832的8位数据已经完成,data_out信号输出采集结果为21,同时,可以读出进行提取个位、十位、百位的二进制数,然后进行转换为数码管显示需要的BCD码,通过仿真结果图可以看出:

个位对应的十六进制数为:F9-----------数码管显示字型:1

十位对应的十六进制数为:A4-----------数码管显示字型:2

百位对应的十六进制数为:C0-----------数码管显示字型:0

根据段选码表如下图所示:

学号026

图中红色箭头所指的信号done_out为高电平,表示采集ADC0832的8位数据已经完成,data_out信号输出采集结果为26,同时,可以读出进行提取个位、十位、百位的二进制数,然后进行转换为数码管显示需要的BCD码,通过仿真结果图可以看出:

个位对应的十六进制数为:82-----------数码管显示字型:6

十位对应的十六进制数为:A4-----------数码管显示字型:2

百位对应的十六进制数为:C0-----------数码管显示字型:0

根据段选码表如下图所示: