基于FPGA的LDPC编译码器说明文档

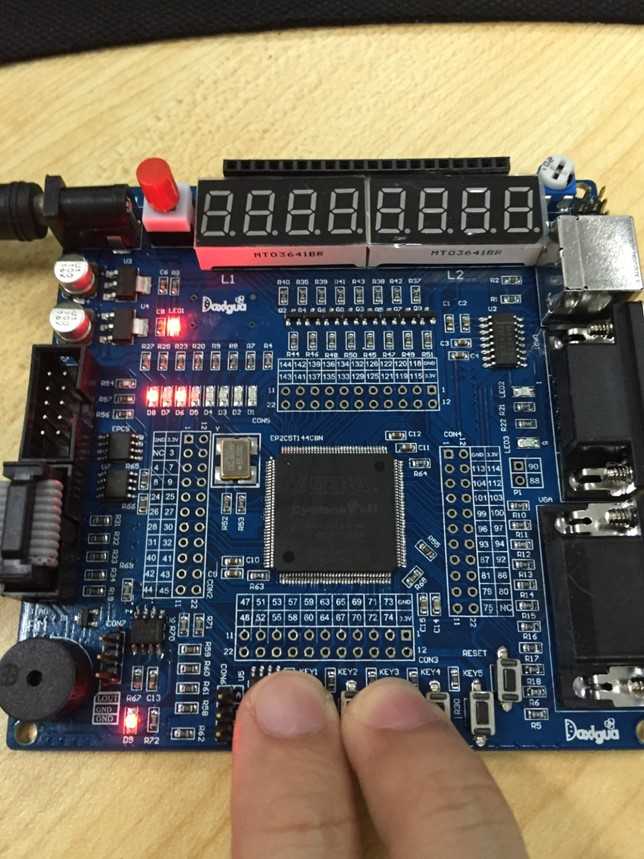

该FPGA设计实现的是一个LDPC码编译码器,采用的是并行输入与并行输出。设计主要分为两个模块:1.LDPC码编码器;2.LDPC码译码器。实现的功能:并行输入4位信息序列,经过编码器后获得12位编码后序列,然后经过译码器译码还原出原始的4位信息序列。LDPC编译码器设计功能框图如图 1所示。

图 1 LDPC编译码器设计功能框图

具体说明如下:

- LDPC码编码器设计

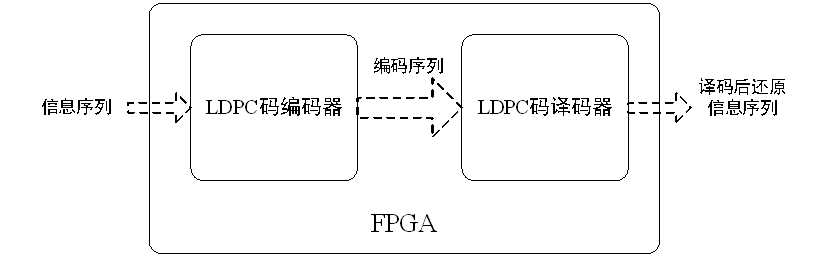

本设计采用的是(8,12)二进制不规则LDPC码,码率为0.33,行重为3和4,列重为2和3。校验矩阵H如下:

编码部分采用的是高斯消元法,获得校验序列c,即可构造出编码序列。具体方法如下:假设有一信息序列,码长为,经过编码之后为码字,码长为,则检验位长度为。其检验矩阵为,如果将检验矩阵分解为,其中为维数矩阵,为维数的满秩矩阵。将分解为(为信息位,为校验位),根据。将校验矩阵变换为(为单位矩阵),有,则有。因为在二元域中,所以检验位为。最后根据(信息位已知),得到编码后的码字。如果高斯消元过程中进行了列交换,则只需记录列交换,并以相反次序对编码后的码字同样进行列交换即可。译码时先求出,再进行列交换得到,后面部分即是还原出来的信息序列。

通过这种方法,可以获得设计中采用的校验矩阵H的P矩阵和列变换。P矩阵为:

列变换col_recoeder为:

意思就是计算出后,要进行列变换,[0 0 0 0 0 0 0 9]意思是第8列与第9列进行交换,其他列都为0,所以不用交换。这个矩阵里面有8列,就是根据对应的数字,与该数字的列进行交换。

由于P矩阵和列变换记录都在设计之前用Matlab计算获得,所以在FPGA中实现时,只需要利用P矩阵计算获得校验比特,最后再进行列变换获得最终的编码后码字。

- LDPC码译码器设计

由于该LDPC码的校验矩阵满足任意两行至多一个相同码元 该码没有4环和6环,可采用大数逻辑译码算法进行译码,能纠正一个错误比特。简单介绍大数逻辑译码原理:

设有一个码字的校验矩阵为

设接收到的码字。相应的伴随式为

对伴随式的分量、、和进行线性组合, 也就是对H矩阵的行进行线性组合,得到以下一组校验方程:

- 发生一个错误, 且在正交码元位上: ,则可得,, 。

- 发生一个错误但不在正交码元位上: , (取5, 4, 3, 2, 1, 0中的某一个), 则只有一个 (), 其它两个均为0。

- 发生两个错误, 其中一个在正交位上, 另一个在其它位(如):, , 则, , 。

- 发生两个错误, 都不在正交位上, 设,, 则, , 。

一个循环码若在任一位上能建立个正交一致校验和式, 则该码能纠正个错误(式中表示取的整数部分)。

在本设计当中,通过这种大数逻辑算法,对码字中每个比特计算它们对应的伴随式的分量(即校正子),可以进行译码纠错。由于由于该LDPC码的校验矩阵满足任意两行至多一个相同码元 该码没有4环和6环,所以只需要一步就可以完成对应比特的纠正(使用的译码算法具体来说叫做一步大数逻辑译码算法)。根据设计所用的校验矩阵H,可以计算出每个比特对应的校验子。例如,假设编码后码字为[,,,…,],则的校验方程如下:

=+

=+++

=0

判断、、当中为1的个数可以判断是否发生错误。当1的个数大于等于2时,则发生错误,进行改正,。

- 测试仿真

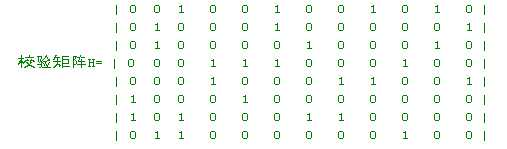

经过设计之后,LDPC编译码器RTL视图如图 2所示。采用Modelsim对设计进行仿真,testbench已经附带在工程目录下。结果如下:

图 2 LDPC编译码器RTL视图

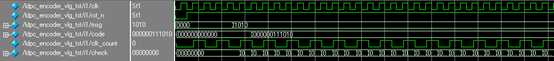

- LDPC编码功能仿真结果

msg为信息序列,code为编码后序列。输入msg为1010,编码的code为0000_0011_1010。

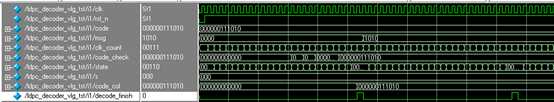

- LDPC译码功能仿真结果

code为编码后序列,msg为译码后还原出来的信息序列。输入code为0000_0011_1010,译码后msg为1010。

假如code发生了一个比特错误变为1000_0011_1010,则译码可以纠错一个比特错误,可以还原出正确的msg为1010。

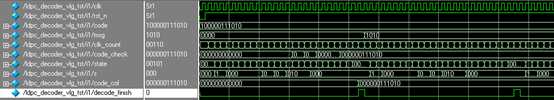

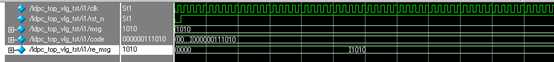

- LDPC编译码功能整体仿真结果

msg为信息序列,code为编码后序列。输入msg为1010,编码的code为0000_0011_1010,译码后还原出的信息序列re_msg为1010,译码正确。

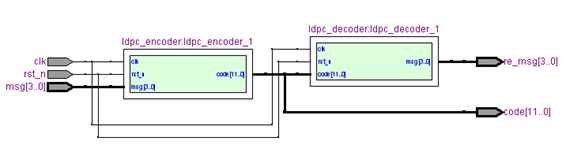

- 板级验证

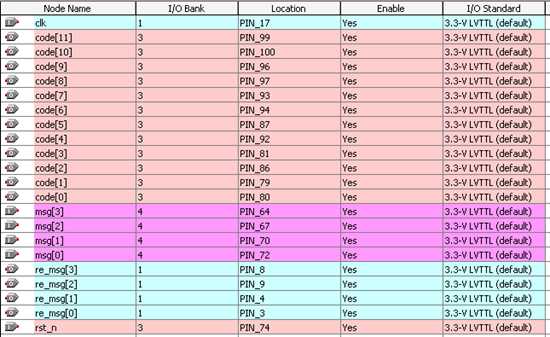

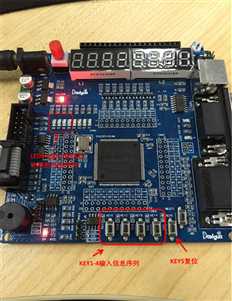

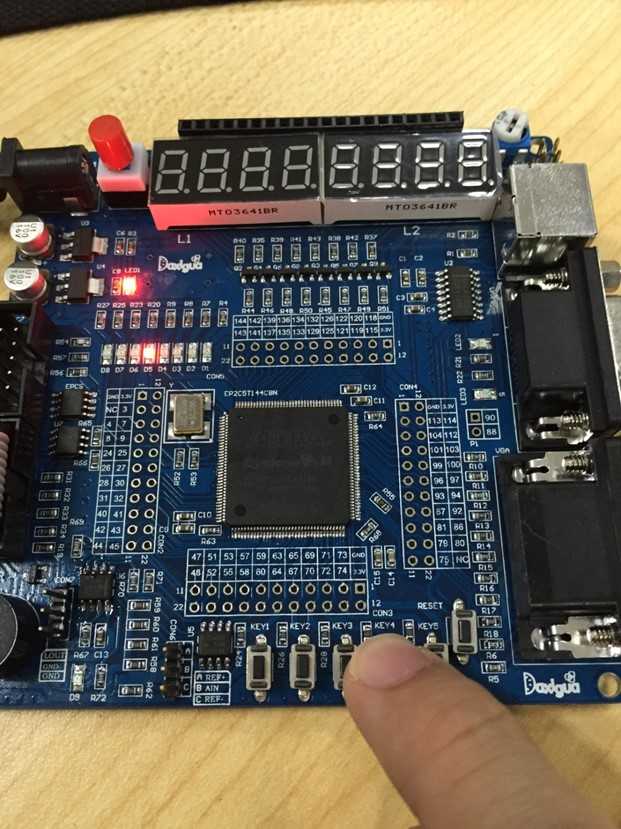

把工程烧录到FPGA开发板上进行验证。板上的按键KEY1-4作为信息序列的输入,通过按键可以输入4位任意比特信息,KEY5作为复位按键。LED8-5显示译码后还原的信息序列。LED灯亮表示对应比特位按键按下。未来方便测试,把编码后的序列分配到了板上12个扩展IO口,分别为pin99、100、96、97、93、94、87、92、81、86、79、80。具体管脚分配如下所示:

开发板操作说明如下:

- 验证一:

输入信息序列为1110,即按下KEY4。开发板上对应的LED5发亮,译码正确。

- 验证二:

输入信息序列为0101,即按下KEY1和KEY3。开发板上对应的LED8和LED6发亮,译码正确。