标签:style blog http os 使用 ar strong 数据 2014

近日根据RF系统,本着节约FPGA内部逻辑资源以及引脚优化的角度,根据计数器的特征,记录个人的一些偶得。

1. 时钟分频

在项目中经常会遇到需要时钟分频,除了使用PLL或DLL;有时所需的分频时钟较多,不适宜采用过多的PLL或DLL,此时采用计数器即为较好的解决方案。

下面以50 MHz的时钟分频产生1KHz的脉冲以及1Hz的时钟信号为例来进行阐述。为避免产生时钟偏移(skew),在设计时钟分频时,须使用主时钟作为节拍。

//////////////////////////////////////////////////////////

/***************** 50000 = 500*100 **********************/

always @(posedge clk_50M) begin

if(!rst_n||cnt100 == 7‘d100) cnt100 <= 7‘d0;

else cnt100 <= cnt100 + 7‘d1;

end

always @(posedge clk_50M) begin

if(!rst_n||cnt500 == 10‘d500) cnt500 <= 10‘d0;

else if(cnt100 == 7‘d100) cnt500 <= cnt500 + 10‘d1;

else cnt500 <= cnt500;

end

always @(posedge clk_50M) begin

if(cnt500 == 10‘d500) clk_1K <= 1;

else clk_1K <= 0;

end

//////////////////////////////////////////////////////////

/************* 50000000 = 500*100*1000 ******************/

always @(posedge clk_50M) begin

if(!rst_n||cnt1K == 10‘d499) cnt1K <= 10‘d0;

else if(clk_1K) cnt1K <= cnt1K + 10‘d1;

else cnt1K <= cnt1K;

end

always @(posedge clk_50M) begin

if(!rst_n) clk_1Hz <= 0;

else if(cnt1K == 10‘d249 && clk_1K) clk_1Hz <= ~ clk_1Hz;

else clk_1Hz <= clk_1Hz;

end

2. 数据通路选择

在某些系统设计中,经常需要选择数据通路,并确定该数据通路数据的有效性。以下以4位计数器为例简要介绍。

reg [3:0] cnt;

// 0000 0001 0010 0011 0100 0101 0110 0111 ……

always @(posedge clk) begin

if(!rst_n) cnt <= 4’d1;

else cnt <= cnt + 4’d1;

end

2.1 数据通路模型

如图1所示,为4通道数据通路模型。 图1 数据通路模型

图1 数据通路模型

2.2 数据通路有效

2.2.1 数据通路历经2个时钟有效

assign datadv = cnt[0];

assign datapath = cnt[2:1];

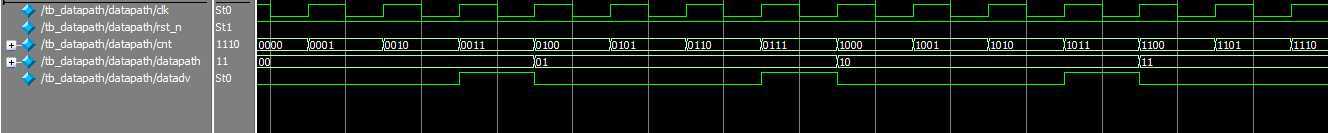

仿真如图2所示。

图2 数据通路历经2个时钟周期仿真图

2.2.2 数据通路历经4个时钟有效

assign datadv = cnt[1]&cnt[0];

assign datapath = cnt[3:2];

仿真如图3所示。

图3 数据通路历经4个时钟周期仿真图

标签:style blog http os 使用 ar strong 数据 2014

原文地址:http://www.cnblogs.com/ssym/p/3984527.html