一,总线

地址总线 想象100个停车位需要多少根线编码? 指针? 7根,

(1)CPU是通过地址总线来指定存储单元的。指针的大小实际上是由CPU的寻址位数决定

(2)地址总线决定了cpu所能访问的最大内存空间的大小。eg: 10根地址线能访问的最大的内存为1024位二进制数据(1B)

(3)地址总线是地址线数量之和。

数据总线 想象2车道、4车道、6车道?

(1) 是CPU与内存或其他器件之间的数据传送的通道。

(2)数据总线的宽度决定了CPU和外界的数据传送速度。

(3)每条传输线一次只能传输1位二进制数据。eg: 8根数据线一次可传送一个8位二进制数据(即一个字节)。

(4)数据总线是数据线数量之和。

控制总线

(1)CPU通过控制总线对外部器件进行控制。

(2)控制总线的宽度决定了CPU对外部器件的控制能力。

(3)控制总线是控制线数量之和。

二,总线通信方式

1、串行通信 和 并行通信

并行通讯通常可以一次传送8bit、16bit、32bit甚至更高的位数,相应地就需要8根、16根、32根信号线,同时需要加入更多的信号地线。传输速度快,距离近;

串行通讯的数据线比较少,这样一条信息的各位数据被逐位按顺序传送。串行通讯的特点是:数据位传送,传按位顺序进行,最少只需一根传输线即可完成,成本低但送速度慢

2、串行通讯根据信息的传送方向可分为单工、半双工和全双工三种

信息只能单向传送为单工;

信息能双向传送但不能同时双向传送称为半双工;

信息能够同时双向传送则称为全双工。

3、串行通信根据是否有时钟线进行同步又分为 同步通信、异步通信

同步通信是一种比特同步通信技术,要求发收双方具有同频同相的同步时钟信号,只需在传送报文的最前面附加特定的同步字符,使发收双方建立同步,此后便在同步时钟的控制下逐位发送/接收。

异步通信在发送字符时,所发送的字符之间的时隙可以是任意的。但是接收端必须时刻做好接收的准备(如果接收端主机的电源都没有加上,那么发送端发送字符就没有意义,因为接收端根本无法接收)。

发送端可以在任意时刻开始发送字符,因此必须在每一个字符的开始和结束的地方加上标志,即加上开始位和停止位,以便使接收端能够正确地将每一个字符接收下来

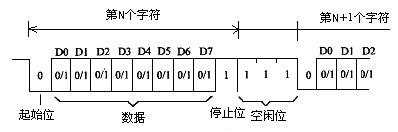

异步通信规定传输的数据格式由起始位(start bit)、数据位(data bit)、奇偶校验位(parity bit)和停止位(stop bit)组成,

如图所示(该图中未画出奇偶校验位,因为奇偶检验位不是必须有的,如果有奇偶检验位,则奇偶检验位应该在数据位之后,停止位之前)。

4,串口总线通信

识别管脚的位置对应哪一位。实现通信至少要2到3根线,其中GND是判别低电平。

5,RS232、RS499、RS423、RS422和RS485等接口标准规范和总线标准规范

TTL电平:输出低电平要小于0.8V,高电平要大于2.4V;输入低于1.2V就认为是0,高于2.0就认为是1;

RS232电平:逻辑1的电平为-3~-15V,逻辑0的电平为+3~+15V,介于-3~+3V之间的电压无意义;

RS485电平:差分信号-2500mv~-200mv为逻辑0;差分信号+2500mv~+200mv为逻辑1;-200mv~+200mv为高阻状态

MAX232芯片是 TTL电平与RS232电平的专用双向转换芯片,可以TTL转RS-232,也可以RS-232转TTL;

TTL与RS232 他们在数据传送上都是一个bit位传输(串行),数据格式也是一样的。最大的区别是他们硬件上有很大的不同。TTL以Vcc作为高电平1(3.3v或5v),以0作为低电平。

而Rs232以-3~-15作为高电平,3~15作为低电平,这种设置使得Rs232更抗电磁干扰和信号的衰减。因此陀螺仪串口发送采用了Rs232,但是你得先把TTL转换成Rs232才行

三,总线类型

1,I2C总线

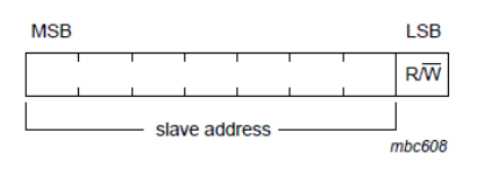

使用:给地址,方向,最后数据 如选定哪个slave,再定读还是写,最后给数据。大端字节序

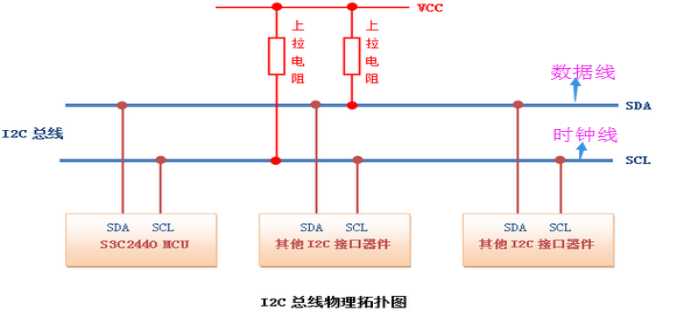

I2C是由Philips公司发明的一种串行数据通信协议,仅使用两根信号线:SerialClock(简称SCL)和SerialData(简称SDA)。I2C是总线结构,1个Master,1个或多个Slave,

各Slave设备以7位地址区分,地址后面再跟1位读写位,表示读(=1)或者写(=0),所以我们有时也可看到8位形式的设备地址,此时每个设备有读、写两个地址,高7位地址其实是相同的。

系统中可能有多个同种芯片,为此addr分为固定部分和可编程部份

1.空闲状态

I2C总线总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。由两条信号线各自的上拉电阻把电平拉高。

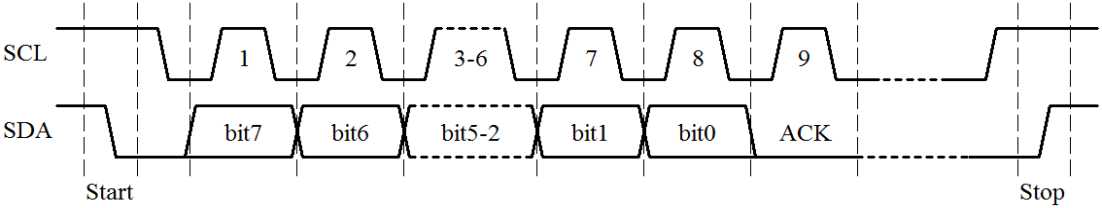

2.起始位与停止位的定义:

起始信号:当SCL为高期间,SDA由高到低的跳变;启动信号是一种电平跳变时序信号,而不是一个电平信号。

停止信号:当SCL为高期间,SDA由低到高的跳变;停止信号也是一种电平跳变时序信号,而不是一个电平信号。

3.数据的有效性:

I2C总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定,只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化。

4.ACK/NACK

发送器每发送一个字节,就在时钟脉冲9期间释放数据线,由接收器反馈一个应答信号。 应答信号为低电平时,规定为有效应答位(ACK简称应答位),表示接收器已经成功地接收了该字节;

应答信号为高电平时,规定为非应答位(NACK),一般表示接收器接收该字节没有成功。 对于反馈有效应答位ACK的要求是,接收器在第9个时钟脉冲之前的低电平期间将SDA线拉低,

并且确保在该时钟的高电平期间为稳定的低电平。 如果接收器是主控器,则在它收到最后一个字节后,发送一个NACK信号,以通知被控发送器结束数据发送,并释放SDA线,

以便主控接收器发送一个停止信号P。

二,SPI总线

PI全称是串行外设接口(Serial Peripheral Interface),是由Motorola提出的一种全双工同步串行通信接口,通信波特率可以高达5Mbps,

但具体速度大小取决于SPI硬件。SPI接口具有全双工操作,操作简单,数据传输速率较高的优点,但也存在没有指定的流控制,

没有应答机制确认是否接收到数据的缺点。

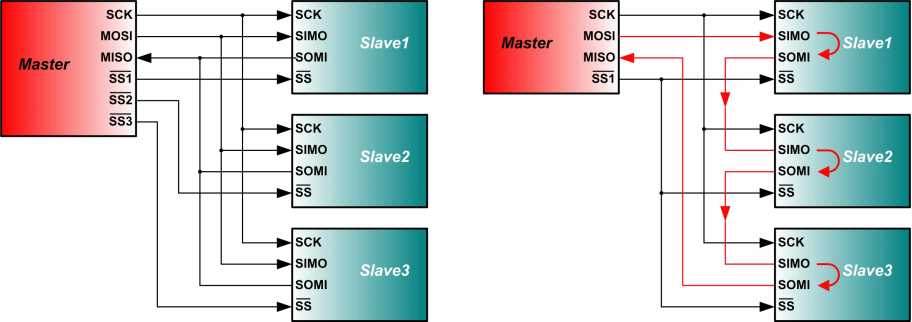

SPI总线只需四条线(如图所示)就可以完成MCU与各种外围器件的通讯:

1)MOSI – Master数据输出,Slave数据输入 2)MISO – Master数据输入,Slave数据输出

3)SCK – 时钟信号,由Master产生 4)/CS – Slave使能信号,由Master控制。

SPI通信采用主从模式(Master-Slave)架构,一般为一个Master和多个Slave的应用模式。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

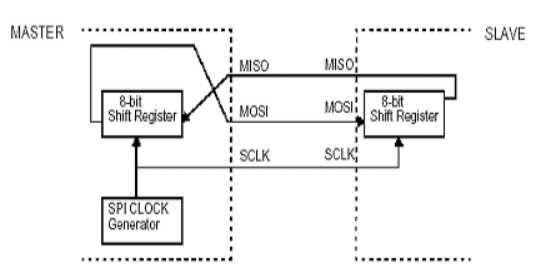

SPI工作原理:

PI接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。

如上右图所示,在SCLK的下降沿上数据改变,上升沿一位数据被存入移位寄存器。SPI接口没有指定的流控制,没有应答机制确认是否接收到数据

四,内存

根据内存的工作原理划分出的两种内存:SRAM(Static Random Access Memory)与DRAM(Dynamic Random Access Memory)

DRAM是一种以电荷形式进行存储的半导体存储器,每个存储单元由一个晶体管和一个电容器组成。数据存储在电容器中。电容器会由于漏电而导致电荷丢失,因而DRAM器件是不稳定的。

为了将数据保存在存储器中,DRAM器件必须有规律地进行刷新。

SRAM每个存储单元需要四到六个晶体管和其他零件,接通代表1,断开表示0,并且状态会保持到接收了一个改变信号为止。这些晶体管不需要刷新,但停机或断电时,它们同DRAM一样,会丢掉信息。

SRAM的速度非常快,通常能以20ns或更快的速度工作。所以,除了价格较贵外,SRAM芯片在外形上也较大,与DRAM相比要占用更多的空间。

SRAM的高速和静态特性使它们通常被用来作为Cache存储器。

SDRAM(Synchronous Dynamic Random Access Memory)在一个时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输;

DDR(Double Data Rate SDRAM)内存则是一个时钟周期内传输两次次数据,它能够在时钟的上升期和下降期各传输一次数据;

在嵌入式MCU中,cache一般是SRAM,外接内存一般都支持SDRAM,现在的ARM处理器普遍都可以支持DDR内存。SDRAM单片大小一般最大到64MB左右,而DDRAM可以到GB。