通常我们使用Modelsim进行仿真,是通过图形界面点点点来进行操作,殊不知Modelsim完美支持TCL脚本语言及批处理命令do文件。简单来说就是从你修改完代码后到你重新编译把需要的信号拉出来查看,现在只需要一个动作即可完成。大大提高了工作效率,博主之前也是点点点了好久,最后发现有这么好的仿真技巧,真是相见恨晚。

下面列举一些常见的TCL脚本命令

Run do文件的一些常用命令 #打开现有工程 project open C:/Users/jayash/Desktop/sim/ImageProcess #新建一个库 vlib my_lib #将其映射到work vmap my_lib work #删除制定库 vmap -del my_lib #添加指定设计文件 project addfile src/Verilog/test.v #编译工程内所有文件 project compileall #编译指定verilog文件 vlog src/Verilog/test.v #编译指定的vhdl文件,同时检查可综合性 vcom –check_synthesis src/video_cap.vhd ##仿真work库下面的test_tb实例,同时调用220model_ver库,不再进行任何优化,仿真分辨率1ns。 vsim –t 1ns –L 220model_ver –gui –novopt work.test_tb #取消warning,例如‘x’,‘u’,‘z’信号的警告,对提高编译速度很有帮助 set StdarithNoWarning 1 #查看object View objects #查看局部变量 View locals #查看source View source #添加模块顶层所有信号到波形图 add wave* #10进制无符号显示 Radix usigned #16进制显示 Radix hex #重新进行仿真 Restart #开始仿真 Run #仿真指定时间 Run 1ms #时钟激励50ns周期 占空比50% Force –repeat 50 clk 0 0,1 25 #指定信号置0 Force rst_n 0 #指定信号置1 Force rst_n 1 #指定信号赋值 Force din_a 123 Force din_b 39

下面是博主经常用的仿真脚本模板,仿真新的工程只需要修改一点点,就可以直接使用了。将sim.do文件放在仿真工程目录下,即和Modelsim仿真工程xxx.mpf在同一个文件夹。sim是我定义的do文件名,用户可自行定义。

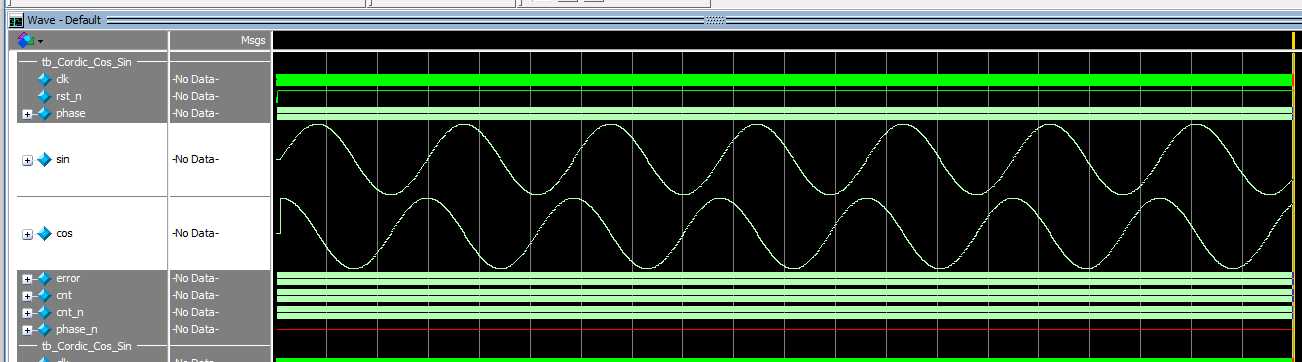

#退出当前仿真 quit -sim vlib work #编译修改后的文件,我这里把设计文件和仿真文件分开放了,所以写两个。 vlog "../Src/*.v" vlog "../Sim/*.v" #开始仿真 vsim -voptargs=+acc work.tb_Cordic_Cos_Sin #添加指定信号 #添加顶层所有的信号 # Set the window types # 打开波形窗口 view wave view structure # 打开信号窗口 view signals # 添加波形模板 add wave -divider {tb_Cordic_Cos_Sin} add wave tb_Cordic_Cos_Sin/* add wave -divider {tb_Cordic_Cos_Sin} add wave tb_Cordic_Cos_Sin/uut/* .main clear #运行xxms run 100us

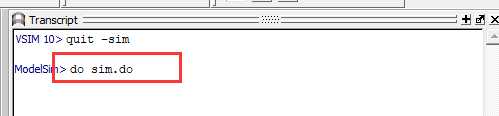

不必每次都输入指定do文件的命令,在脚本控制台直接按上键就会显示上一个执行过的命令。

最后在Transcript窗口下,直接输入do sim.do + 回车即可自动化仿。

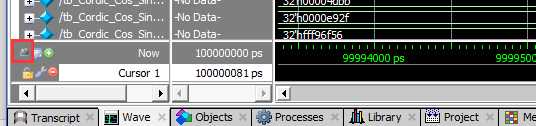

点击wave窗口的这里可以不用显示信号的相对路径。最后直接可以看仿真波形了。

适当的修改do脚本文件,可以添加任意你需要的信号,以及仿真库文件,让我们共同学习,高效工作吧。

最后欢迎关注博主的个人微信订阅号【开源FPGA】,总结、记录自己的学习过程,一个FPGA工程师的养成之路。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/8685991.html