标签:技术 cer 结构 init 大致 公司 data .com 帮助

所谓“中断”,通俗地讲,就是CPU在遇到一个需要即时处理的情况时,暂时中止当前程序的执行,转而处理新情况。

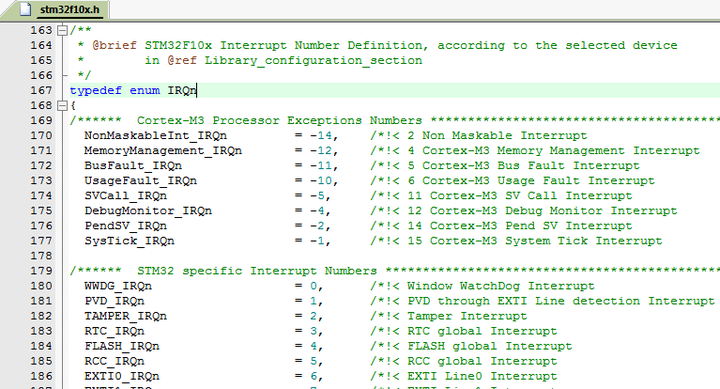

在stm32参考手册中的中断和异常向量表里可查阅到,其内核的异常响应系统里有10个系统异常(含Reset和HardFault),60个外部中断。具体的定义可在库文件stm32f10x.h头文件的IRQn_Type枚举里查到。如图5-1。

图5-1

图5-1

在进行中断配置前,有两个概念需要先弄清楚——NVIC、优先级定义及分组。

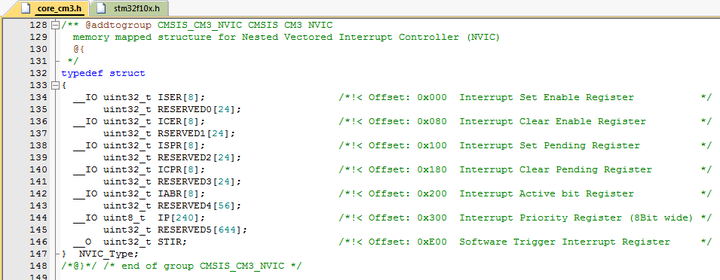

NVIC即为嵌套向量中断控制器,控制着整个芯片的中断相关,是Cortex-M3内核里的一个外设。其在库文件core_cm3.h里定义如下:

图5-2

图5-2

其中ISER(中断使能寄存器NVIC_ISERx)、ICER(中断清除寄存器NVIC_ICERx)、IP(8bit中断优先级寄存器NVIC_IPRx)会在配置中断的时候用到。我们可在core_cm3.h库文件里找到相关寄存器操作的函数声明,如操作ISER的NVIC_EnableIRQ()函数,操作ICER的NVIC_DisableIRQ()函数,操作IP的NVIC_SetPriority()函数等。

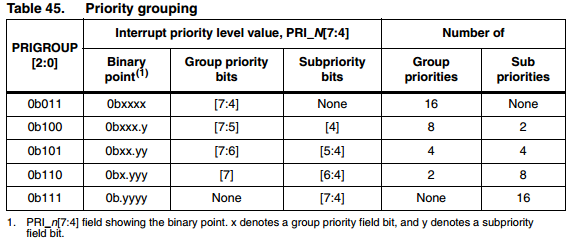

NVIC里有一个中断优先级寄存器NVIC_IPRx,用来配置外部中断的优先级。IPR的宽度为8bit,而ST公司的F103芯片只用了高4bit来配置优先级,即每个外部中断可配置的优先级为0~15。这4bit被分组为抢占优先级(pre-emption priority)和子优先级(subpriority),数值越小,优先级越高。首先会比较抢占优先级,如果相同则比较子优先级,还是相同则继续比较各自的硬件中断编号(编号可在参考手册里的异常向量表查到,编号越小,优先级越高)。

优先级分组由内核外设SCB的AIRCR(应用程序中断及复位控制寄存器)的PRIGROUP[10:8]位决定,在F103里分成了5组。如图5-3。

图5-3

图5-3

上图中的表格里显示了5组的优先级,由于只用了高4位,所以级数最多为16(0~15,有16个级数)。优先级分组配置可调用NVIC_PriorityGroupConfig()函数实现,函数声明和定义分别在库文件misc.h和misc.c中。该函数便是封装了对SCB_AIRCR寄存器的操作。

经以上了解后,可以开始进入程序环节了。一般中断编程按以下三点来完成:

其中,

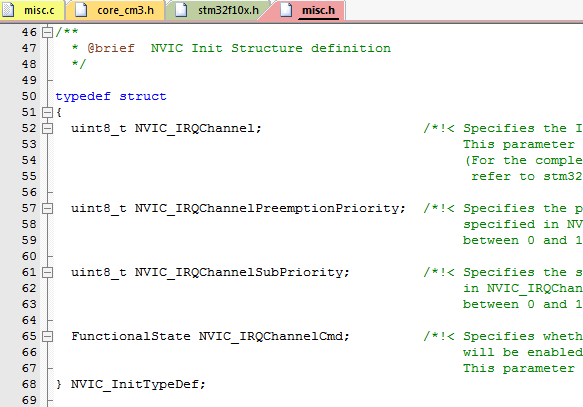

在第3点,NVIC_InitTypeDef结构体是在库文件misc.h中定义的。如图5-4。

图5-4

图5-4

由图中库函数源码可知,

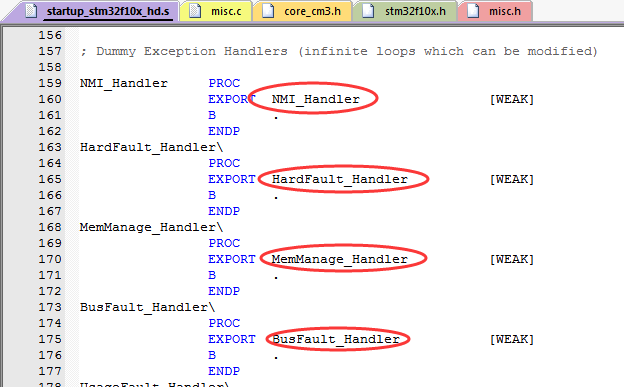

图5-5

图5-5

至此,对中断已经有了一个大致的认识,第一步算是圆满完成啦。那么接下来的下半部分会开始借用一个实例来帮助巩固实践。

标签:技术 cer 结构 init 大致 公司 data .com 帮助

原文地址:https://www.cnblogs.com/fire909090/p/8872510.html