标签:|| 语法规则 nbsp logic sys 标准 表达 png ril

在使用Verilog对硬件逻辑进行建模和模拟的同时,必须理解代码与硬件实现的联系和Verilog语言本身的语法规则,如果对于这些理解不够,往往会造成代码调试周期延长,更有甚者造成电路逻辑功能异常的情况出现,从而拖延电路设计的周期。本文列举的错误不仅初学者经常遇到,在一些经验丰富的电路设计人员中也经常会出现这些问题,为此,本文以尽量浅显易懂的方式及示例展示这些常见的问题,希望对于广大有需要的朋友提供一些力所能及的帮助。同时,希望大家在完成必要的编码之后能够对编写的代码进行代码规则检查,目前常用的代码规则检查工具有:SpyGlass(Synopsys)、Leda(Synopsys)、HAL(Cadence)等,同时这些工具中还集成了大量的业界标准规则集,可以通过这些EDA工具对于设计代码进行比较全面的检查,为后续电路的仿真及实现提供必要的帮助,可以极大地缩短研制周期。

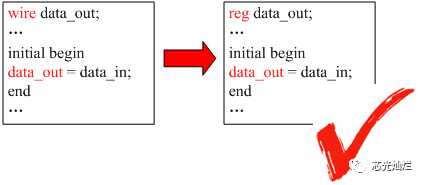

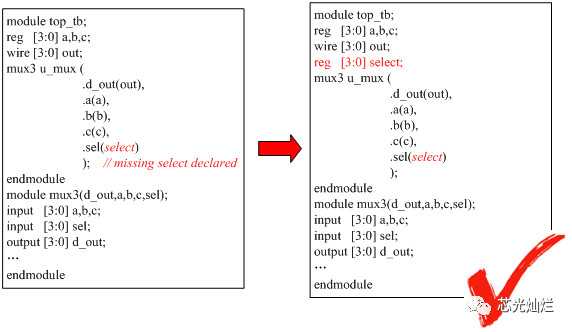

过程性赋值语句左侧信号没有声明为reg或者logic类型,而是声明为了线网类型,例如:

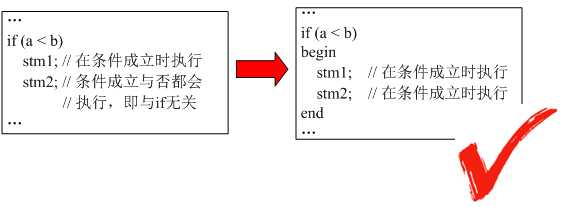

使用begin-end没有配对使用,导致语句执行与预期不相符,特别是在条件表达式中,例如:

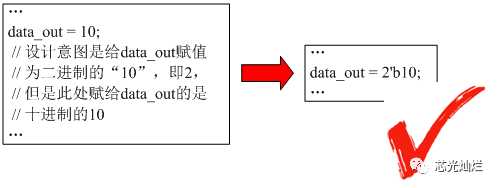

进行常量赋值时,没有执行相应的数制,可能导致结果与预期不一致。例如:

语句结尾缺失当前行结束标志“;”,将会导致编译失败。例如:

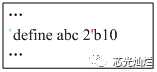

混用“‘”(位于回车键旁)和“`”(位于ESC键下方),“‘”常用语具体数字表达式中的进制中,而“`”常用语各种编译命令中。例如:

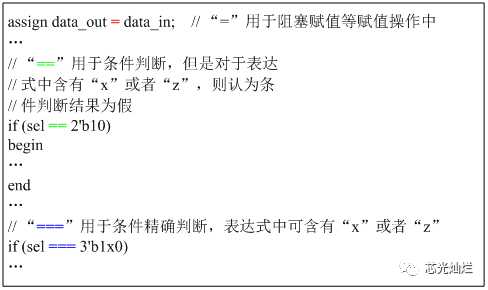

混淆使用“=”,“==”和“===”

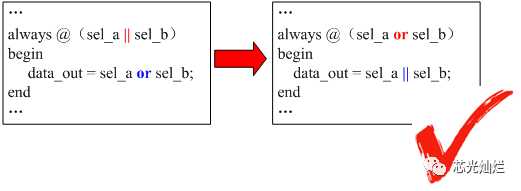

混淆使用“||”和“or”

如果将“||”用于敏感信号列表中,进程是否不触发不是取决于其中任何一个信号的变化,而是取决于两个敏感信号列表中的信号“||”完的结果是否发生变化,所以将“||”放入敏感信号列表并不会导致仿真错误,但是将会导致你的结果不是期望的,试想“||”任何一侧的信号如果为常1,那么另一侧信号怎么变化,其结果都是1,此时进程是不会被触发的。但是or是如果用在了赋值语句中,编译即会报错。

使用关键字作为信号名,具体关键词可参考IEEE中附录,建议不要使用如下关键词命名信号。

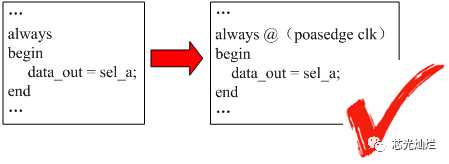

在always未使用时序控制相关的描述,导致always进程陷入无限循环。例如:

在设计中使用隐含线网连接多位矢量端口,将会导致多位矢量仅有最低位的变化会反应到隐含线网上,即隐含线网默认为1位宽。例如:

标签:|| 语法规则 nbsp logic sys 标准 表达 png ril

原文地址:https://www.cnblogs.com/xgcl-wei/p/8905701.html